|              |              |              |              |                 |

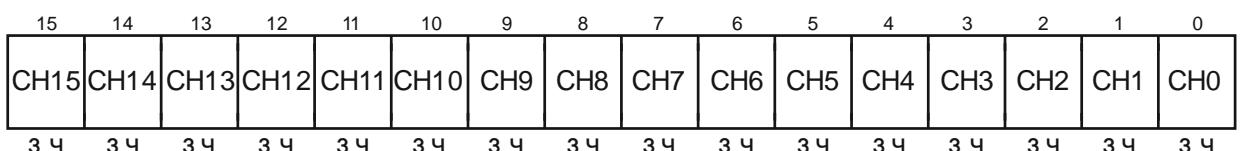

|--------------|--------------|--------------|--------------|-----------------|

| Инв. № подл. | Подп. и дата | Взам. инв. № | Инв. № дубл. | Подп. и дата    |

|              |              |              |              | КФДЛ.431295.072 |

МИКРОСХЕМА ИНТЕГРАЛЬНАЯ

K1946BK035

Руководство пользователя

|              |              |              |              |              |

|--------------|--------------|--------------|--------------|--------------|

| Инв. № подл. | Подп. и дата | Взам. инв. № | Инв. № дубл. | Подп. и дата |

|              |              |              |              | 2021         |

## Содержание

|                                                        |    |

|--------------------------------------------------------|----|

| Введение .....                                         | 5  |

| 1 Область применения и особенности ИС К1946ВК035 ..... | 6  |

| 2 Краткое техническое описание микроконтроллера .....  | 7  |

| 2.1 Функциональные параметры .....                     | 7  |

| 2.2 Электрические параметры .....                      | 11 |

| 3 Архитектура изделия.....                             | 13 |

| 4 Блок управления сбросом и синхронизацией RCU .....   | 15 |

| 4.1 Общая система тактирования .....                   | 15 |

| 4.2 Синтезатор частоты PLL .....                       | 15 |

| 4.3 Система слежения за тактовыми сигналами .....      | 16 |

| 4.4 Сигналы сброса .....                               | 17 |

| 4.5 Прерывания .....                                   | 17 |

| 4.6 Тактирование и сброс периферийных блоков.....      | 17 |

| 5 Блок управления энергопотреблением PMU .....         | 19 |

| 5.1 Режим Sleep .....                                  | 19 |

| 5.2 Режим Deepsleep .....                              | 19 |

| 6 Организация памяти .....                             | 21 |

| 7 Контроллер Flash-памяти.....                         | 23 |

| 7.1 Основная Flash-память .....                        | 23 |

| 7.2 Загрузочная Flash-память .....                     | 24 |

| 7.3 Сервисный сброс всей Flash-памяти .....            | 25 |

| 8 Контроллер прямого доступа к памяти DMA.....         | 26 |

| 8.1 Программное управление контроллером DMA .....      | 27 |

| 8.2 Правила обмена данными .....                       | 32 |

| 8.3 Правила арбитража .....                            | 33 |

| 8.4 Типы циклов .....                                  | 35 |

| 8.5 Индикация ошибок .....                             | 47 |

| 9 Система прерываний .....                             | 48 |

| 10 Порты ввода-вывода.....                             | 52 |

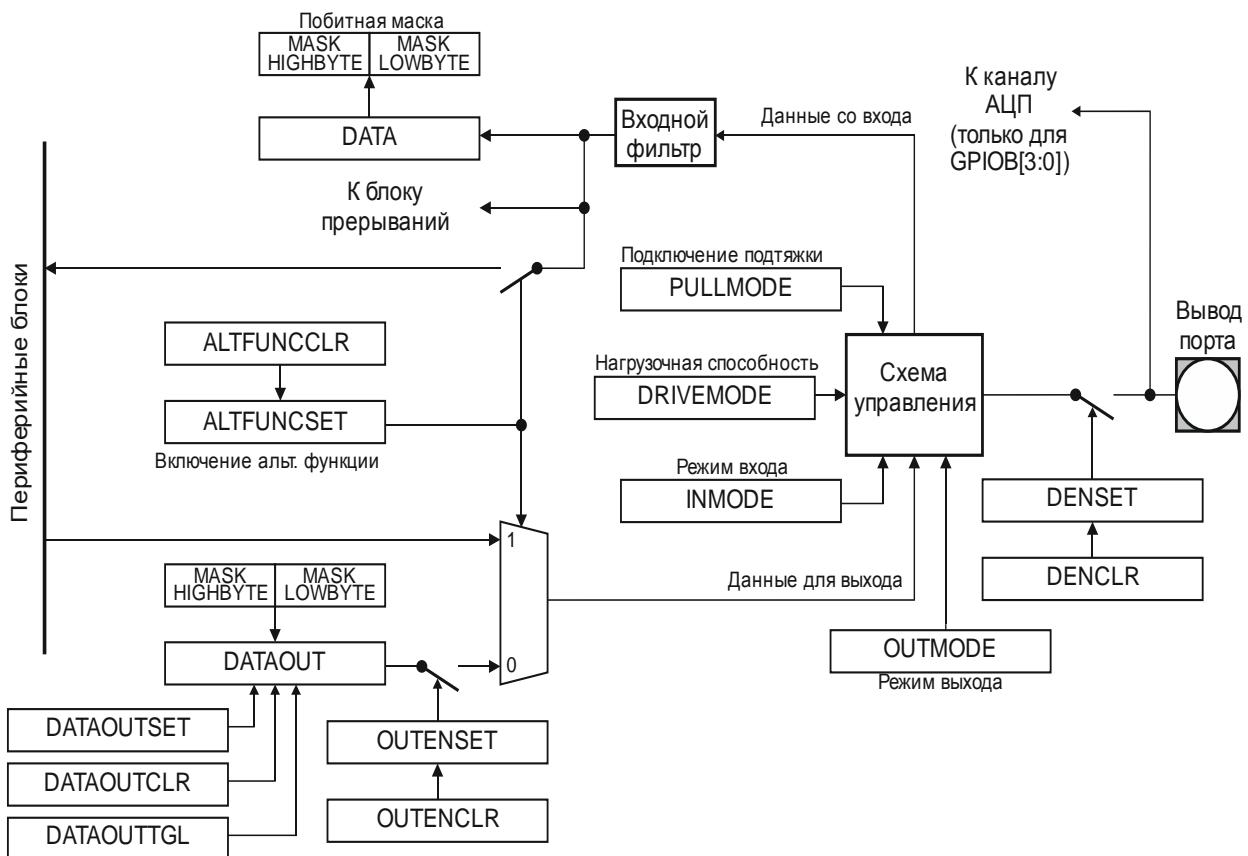

| 10.1 Функционирование порта .....                      | 52 |

| 10.2 Режим альтернативных функций .....                | 53 |

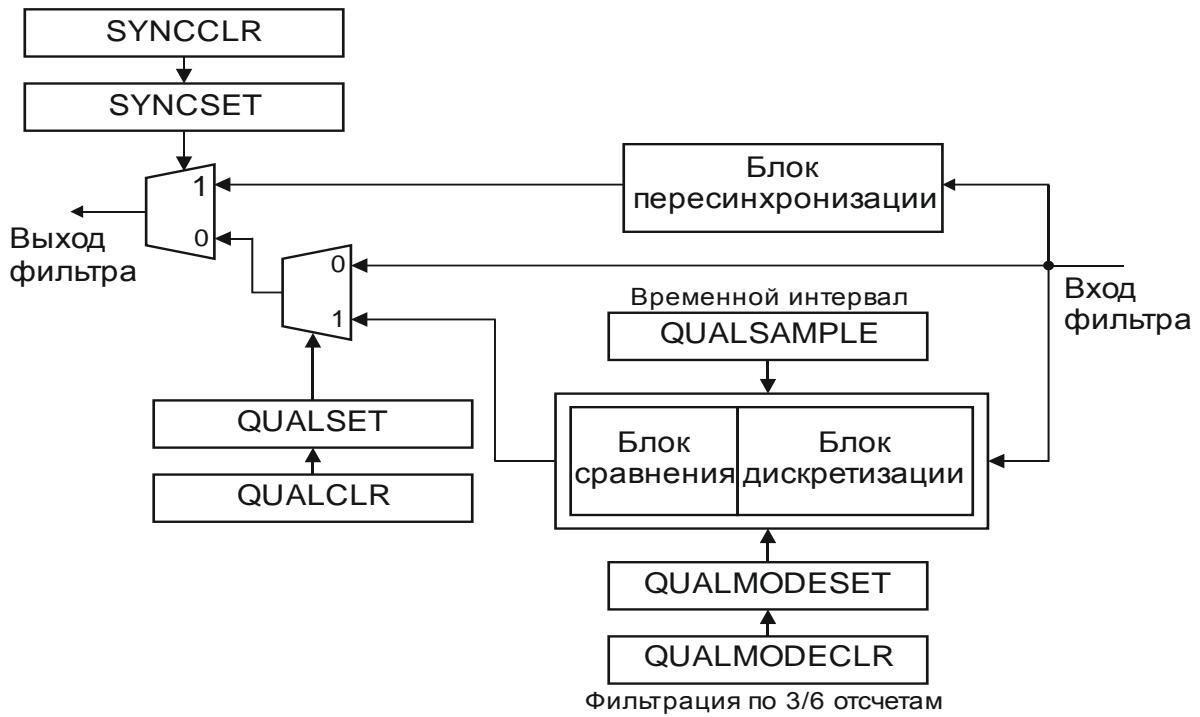

| 10.3 Входные фильтры .....                             | 53 |

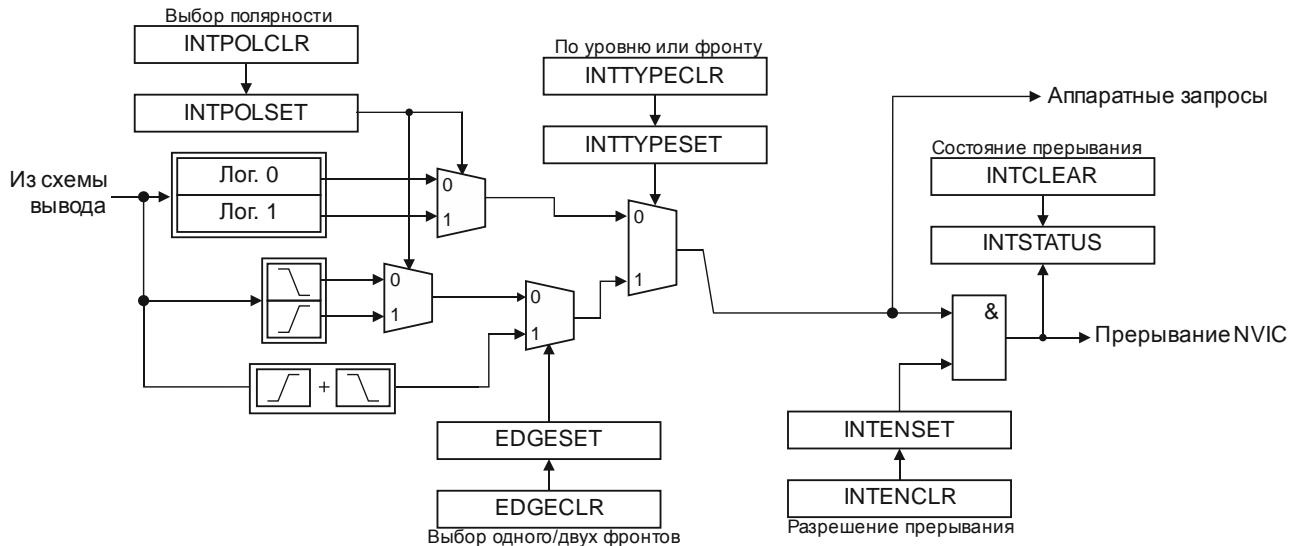

| 10.4 Прерывания .....                                  | 54 |

| 10.5 Генерация аппаратных запросов .....               | 55 |

| 10.6 Механизм блокировки конфигурации .....            | 55 |

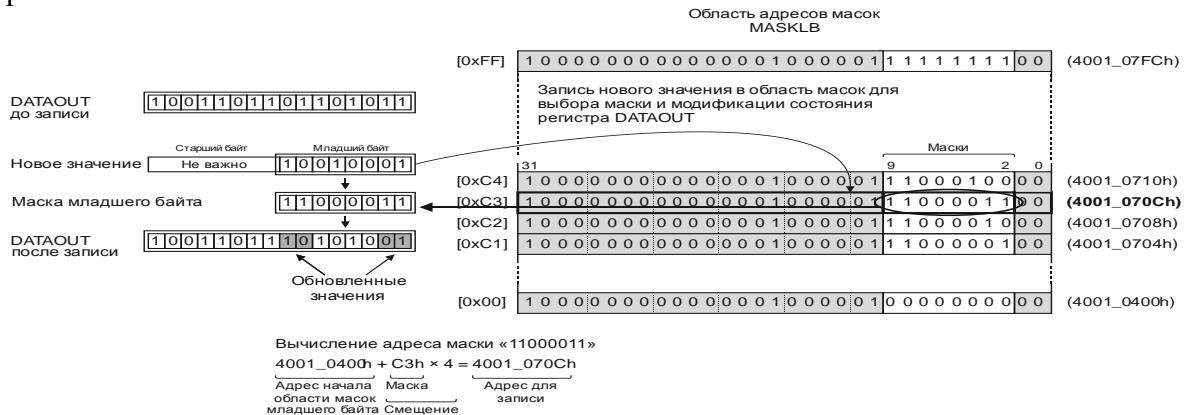

| 10.7 Механизм маскирования .....                       | 56 |

| 11 Блоки таймеров .....                                | 57 |

| 12 Блоки захвата .....                                 | 58 |

| 12.1 Режим захвата времени .....                       | 59 |

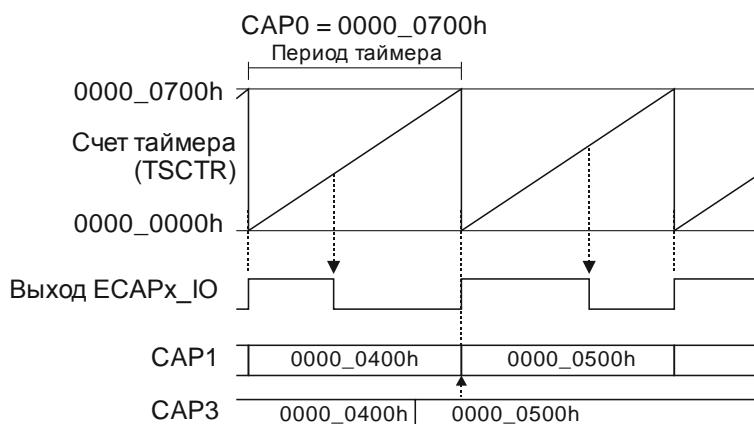

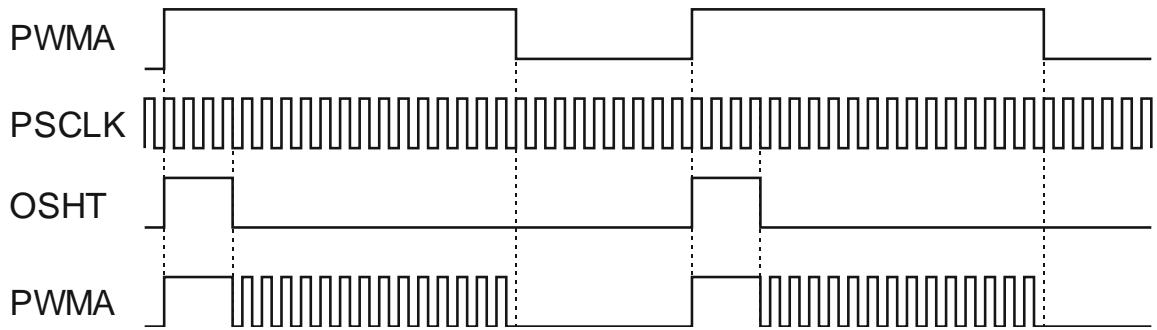

| 12.2 Режим работы «генератор ШИМ» .....                | 60 |

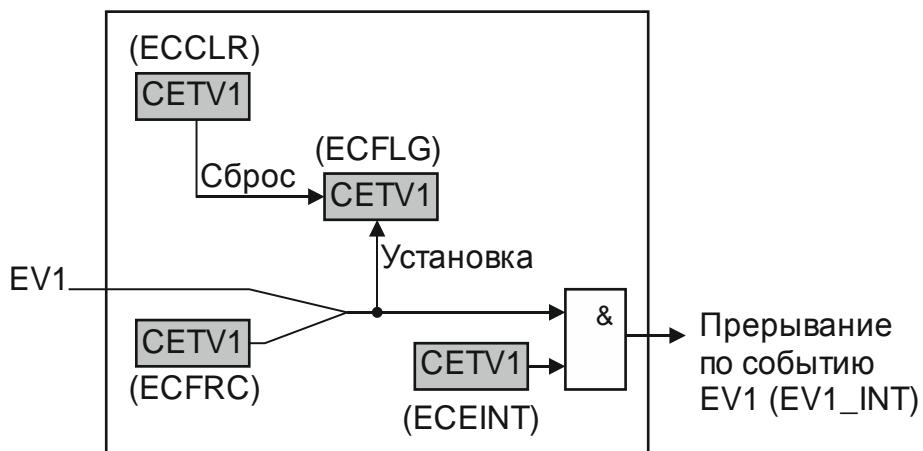

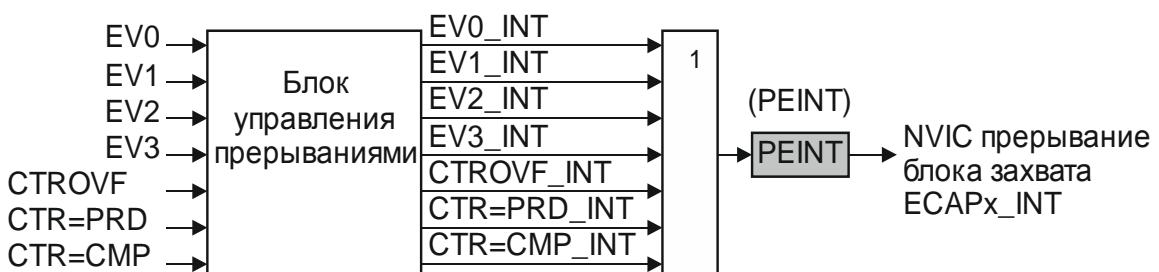

| 12.3 Прерывания .....                                  | 62 |

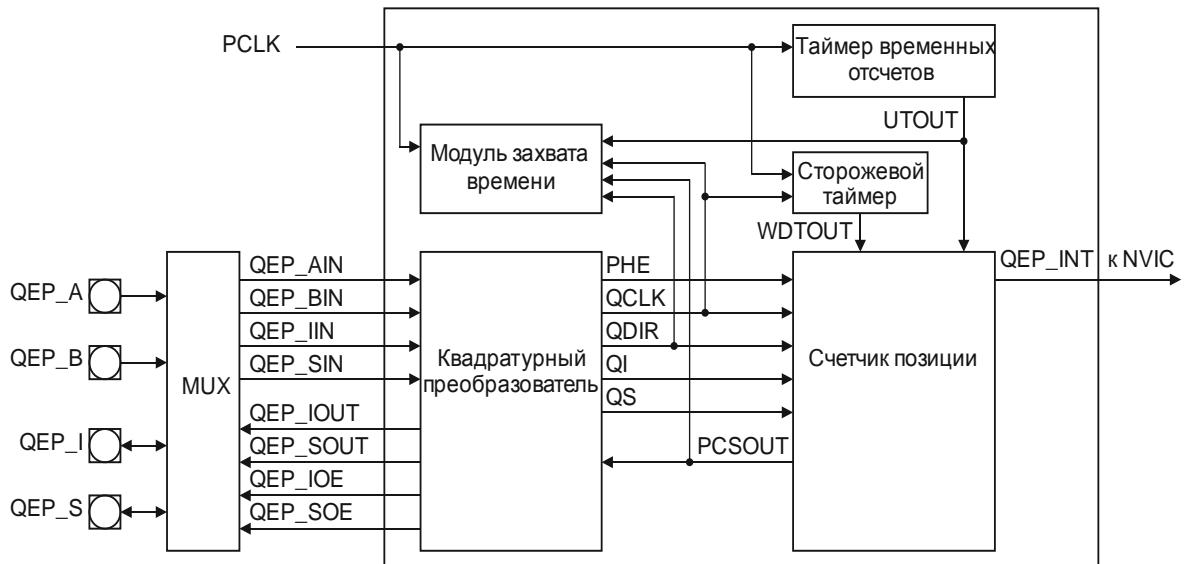

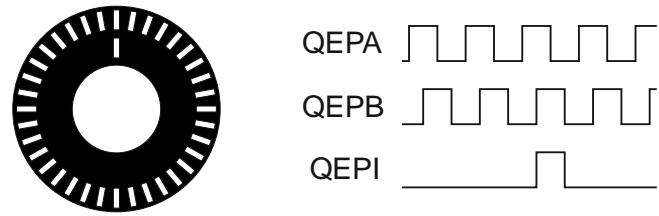

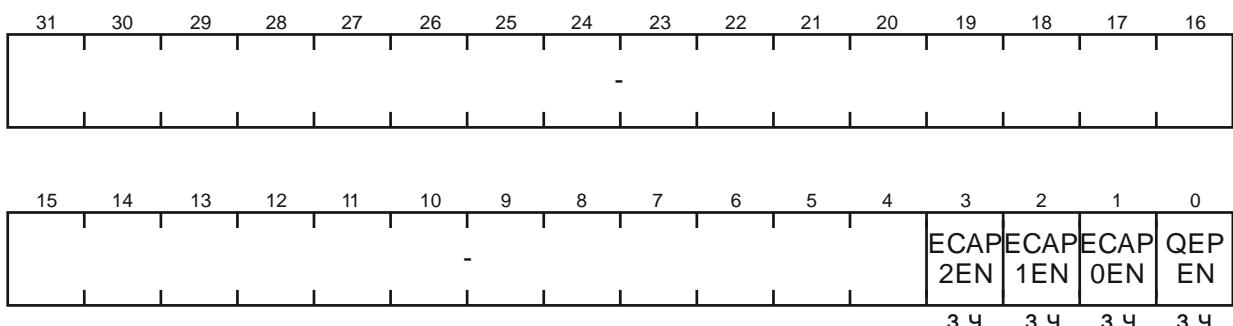

| 13 Модуль квадратурного декодера QEP .....             | 63 |

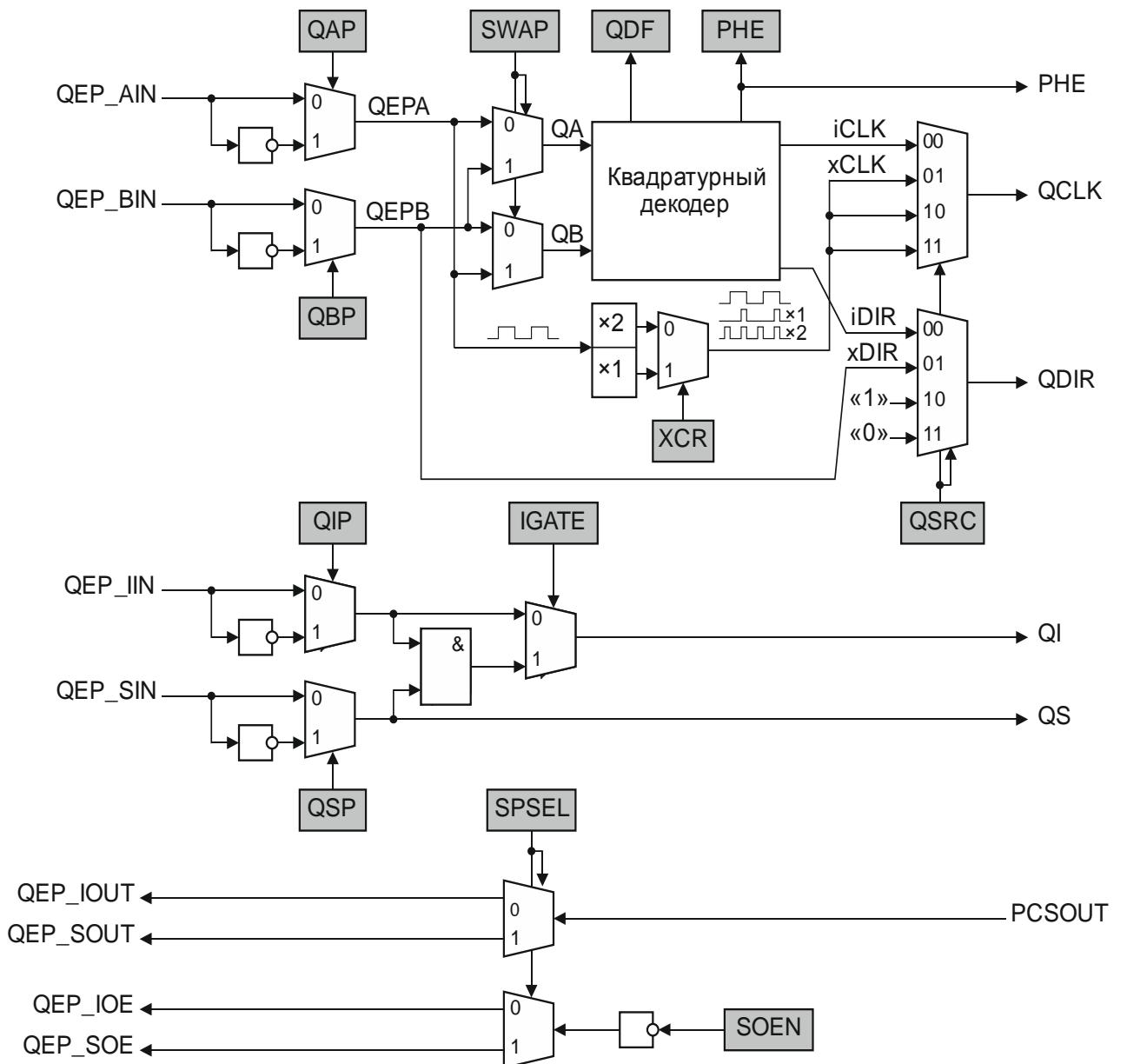

| 13.1 Обработчик сигналов входов.....                   | 63 |

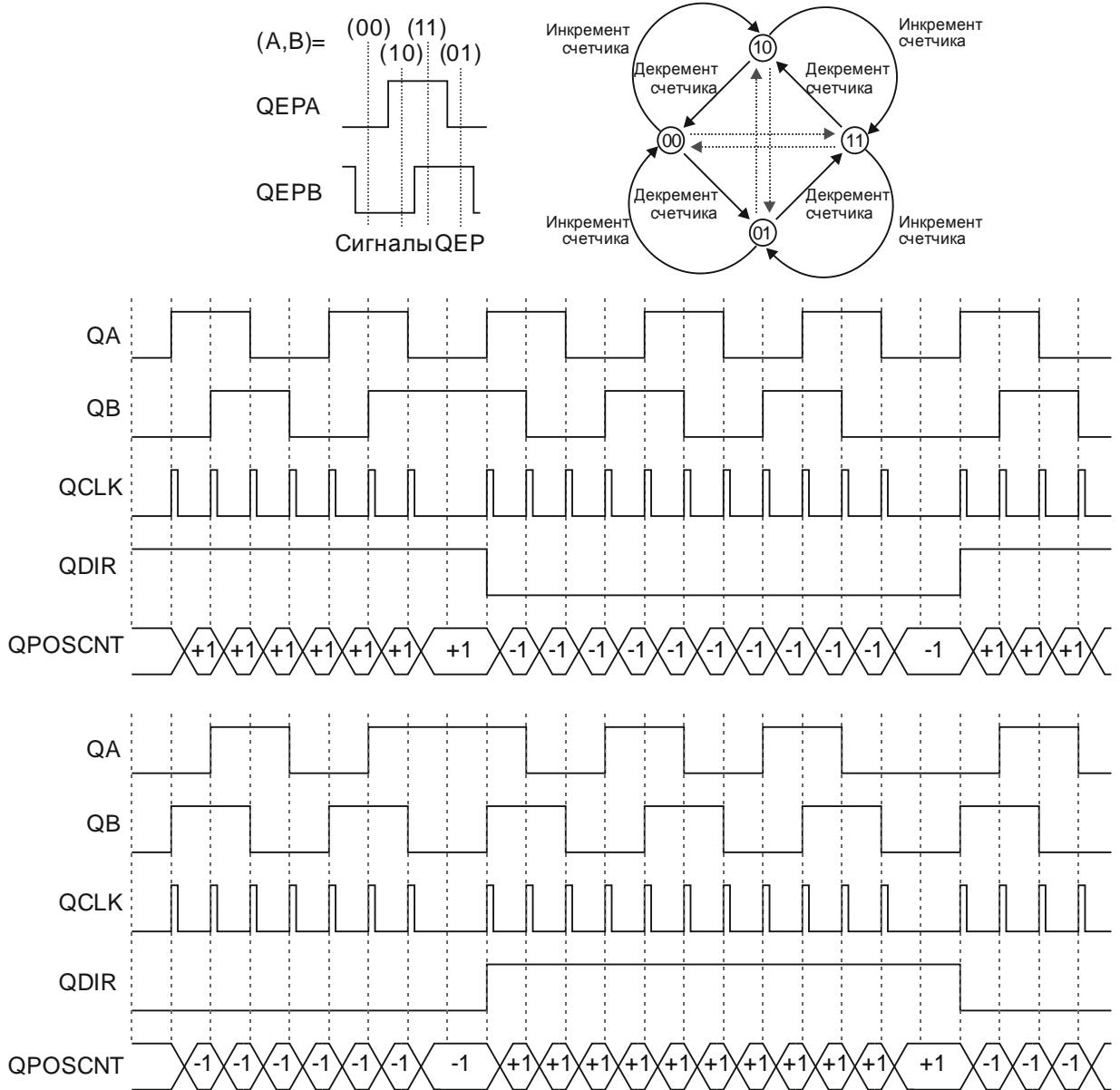

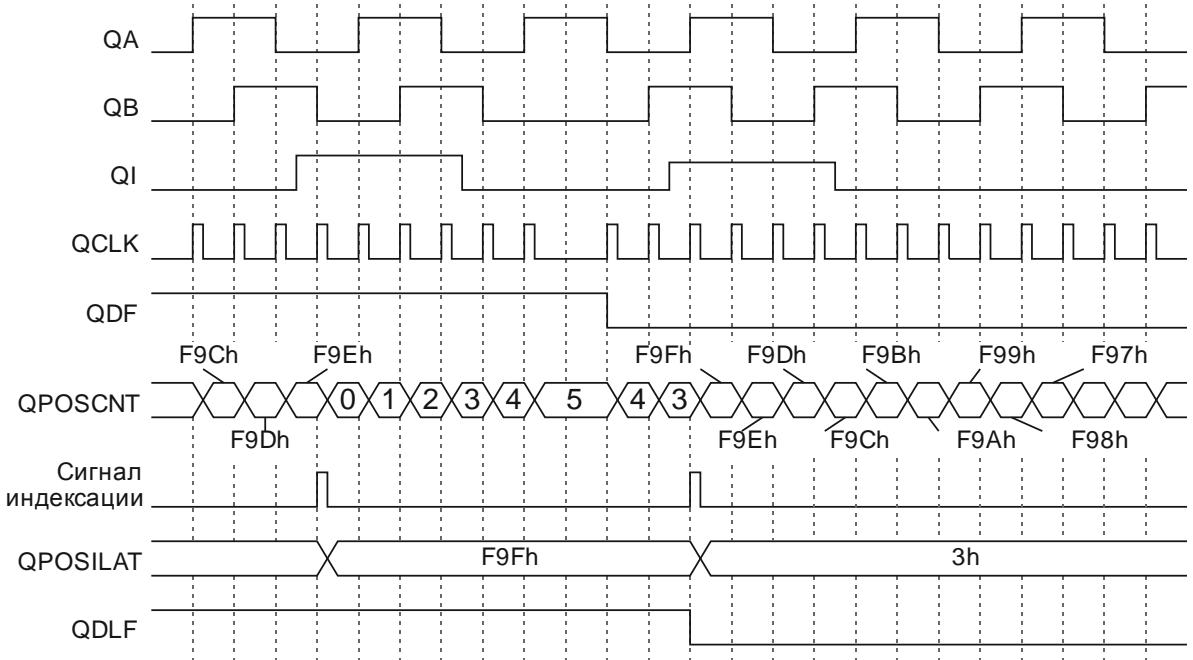

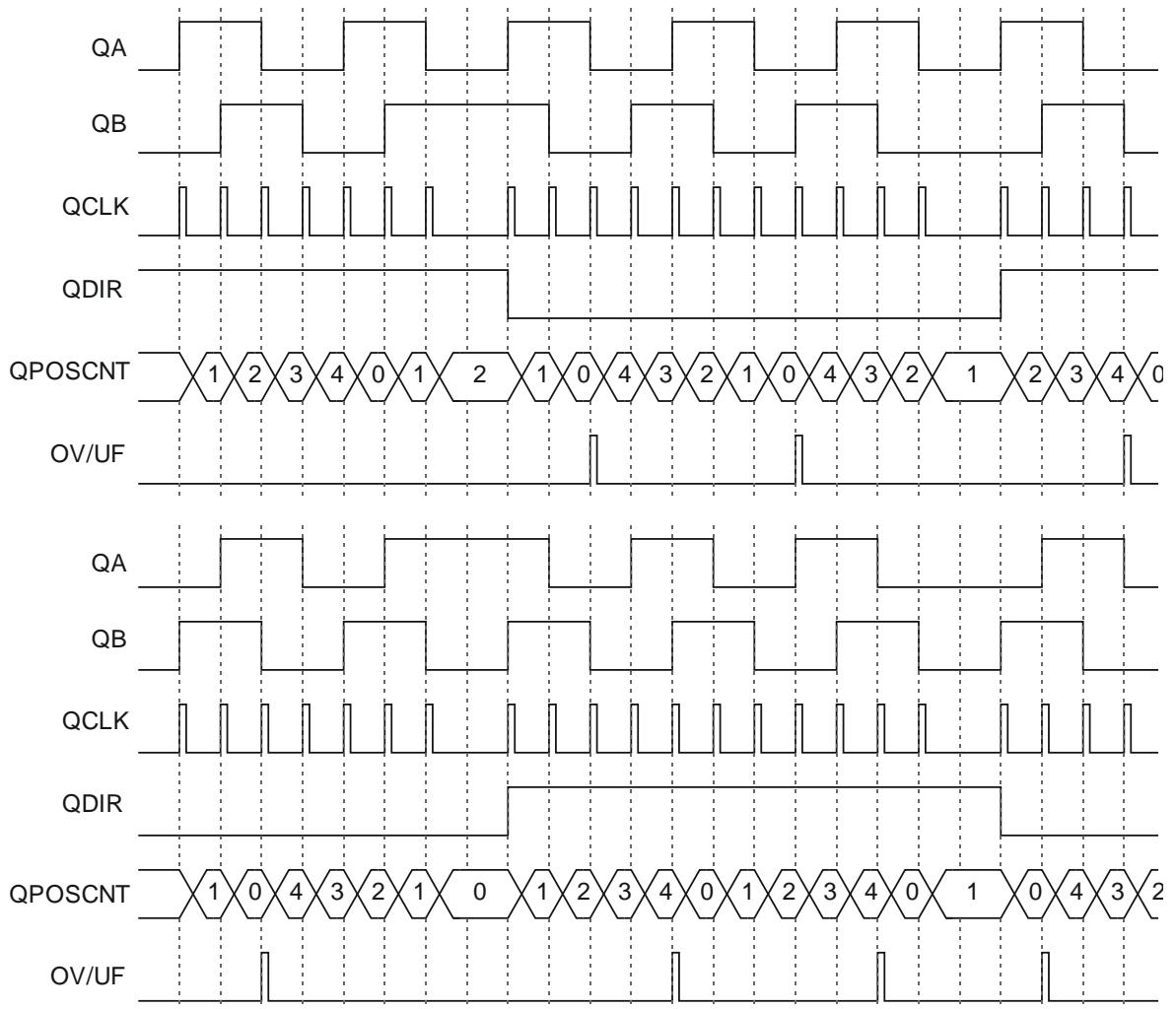

| 13.2 Квадратурный преобразователь .....                | 64 |

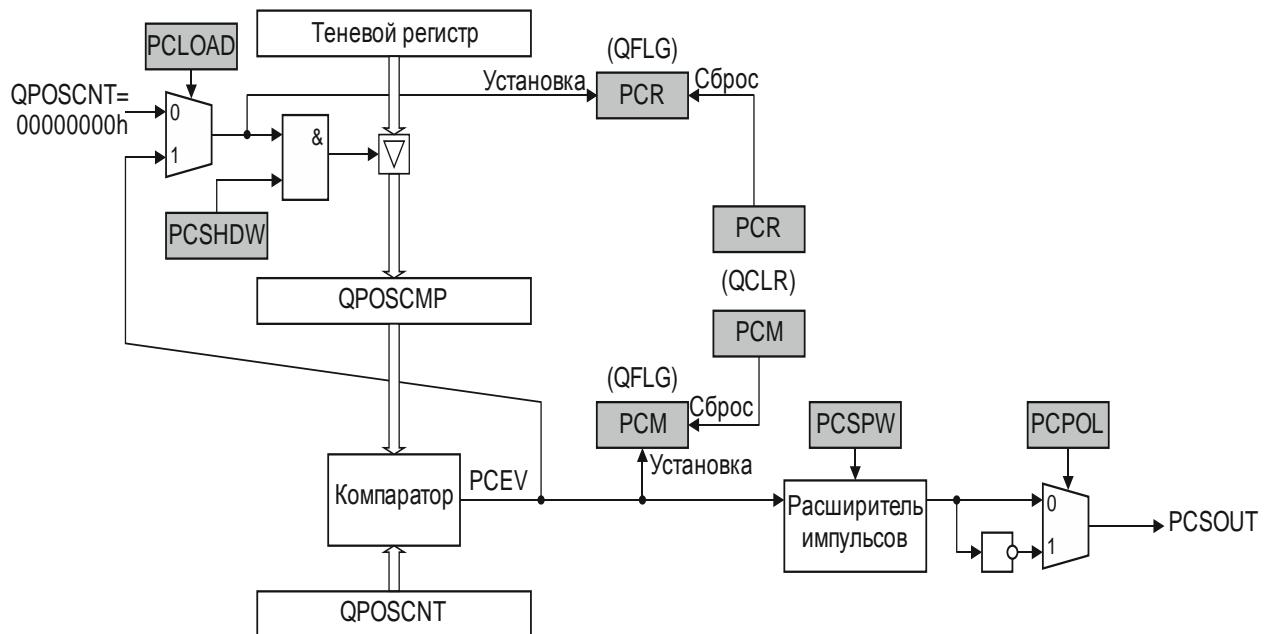

| 13.3 Счетчик позиции.....                              | 66 |

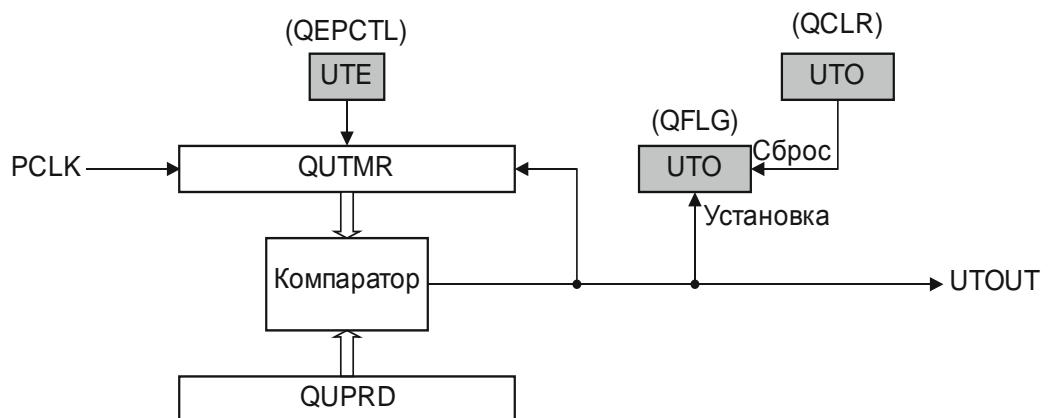

| 13.4 Таймер временных отсчетов .....                   | 71 |

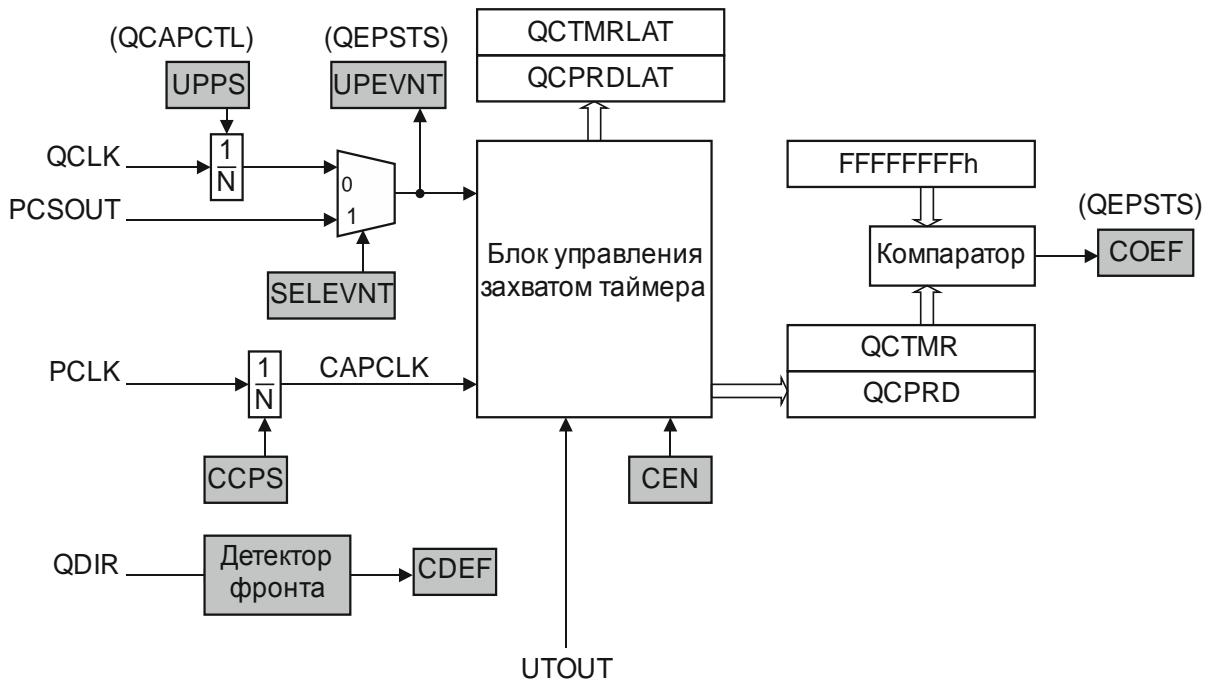

| 13.5 Модуль захвата времени .....                      | 71 |

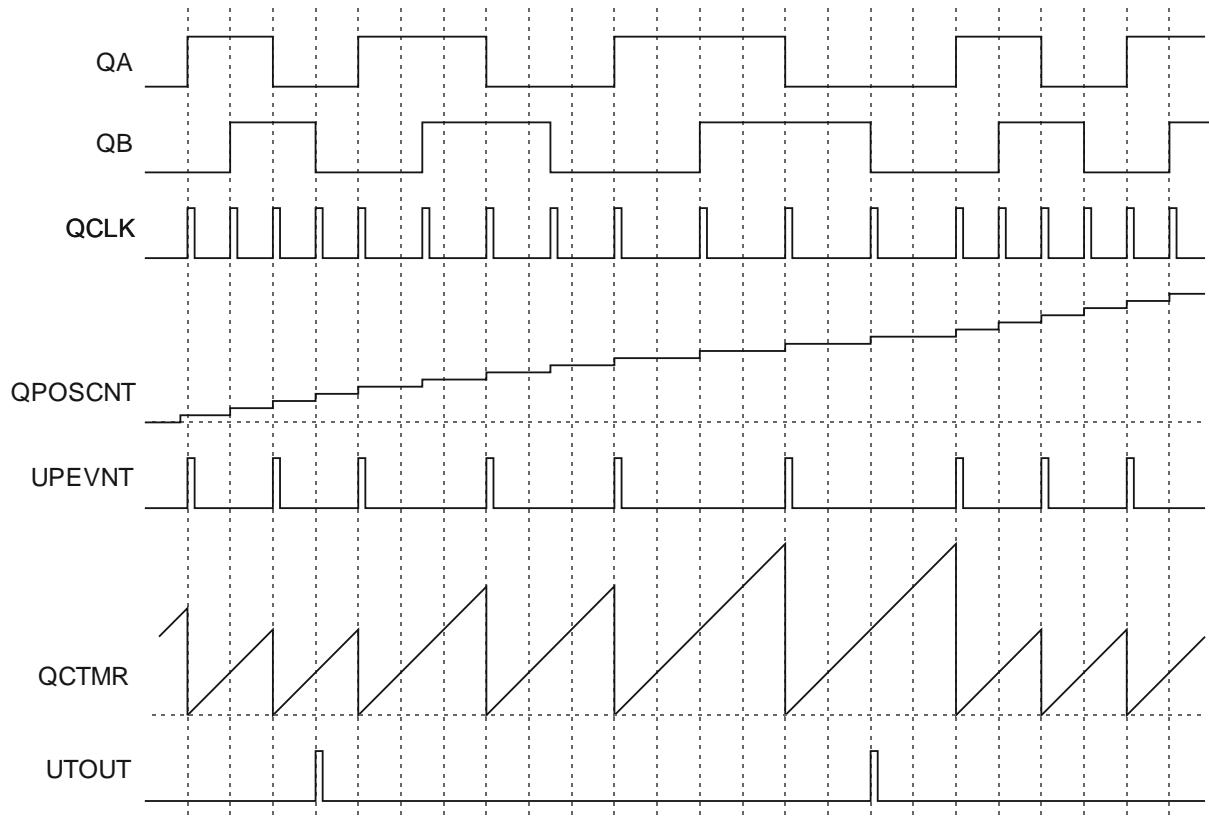

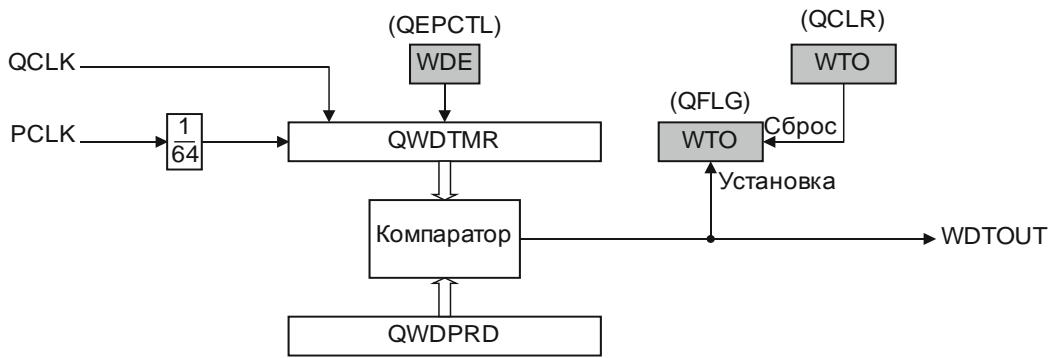

| 13.6 Сторожевой таймер блока QEP .....                 | 73 |

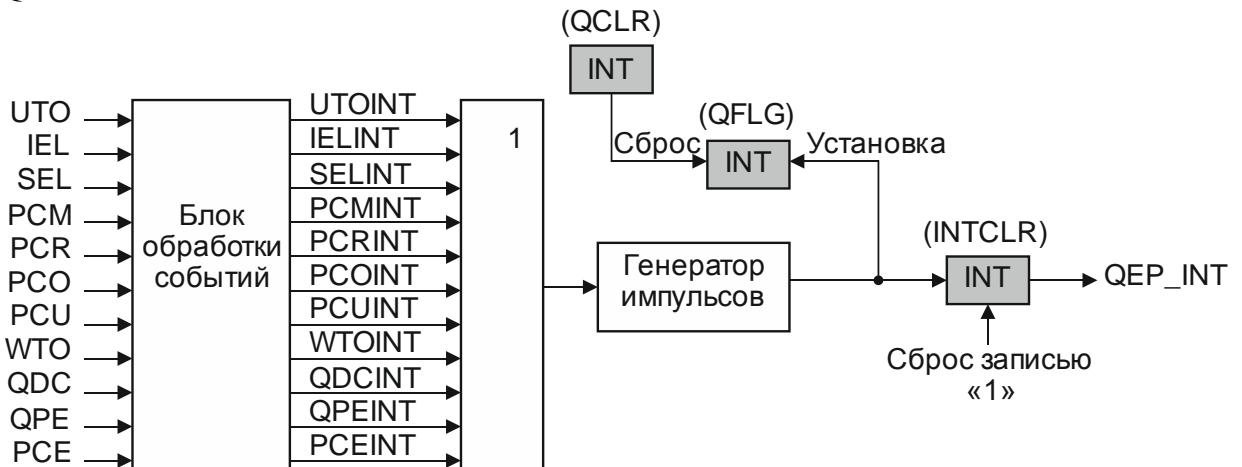

| 13.7 Прерывания .....                                  | 74 |

|                                                            |     |

|------------------------------------------------------------|-----|

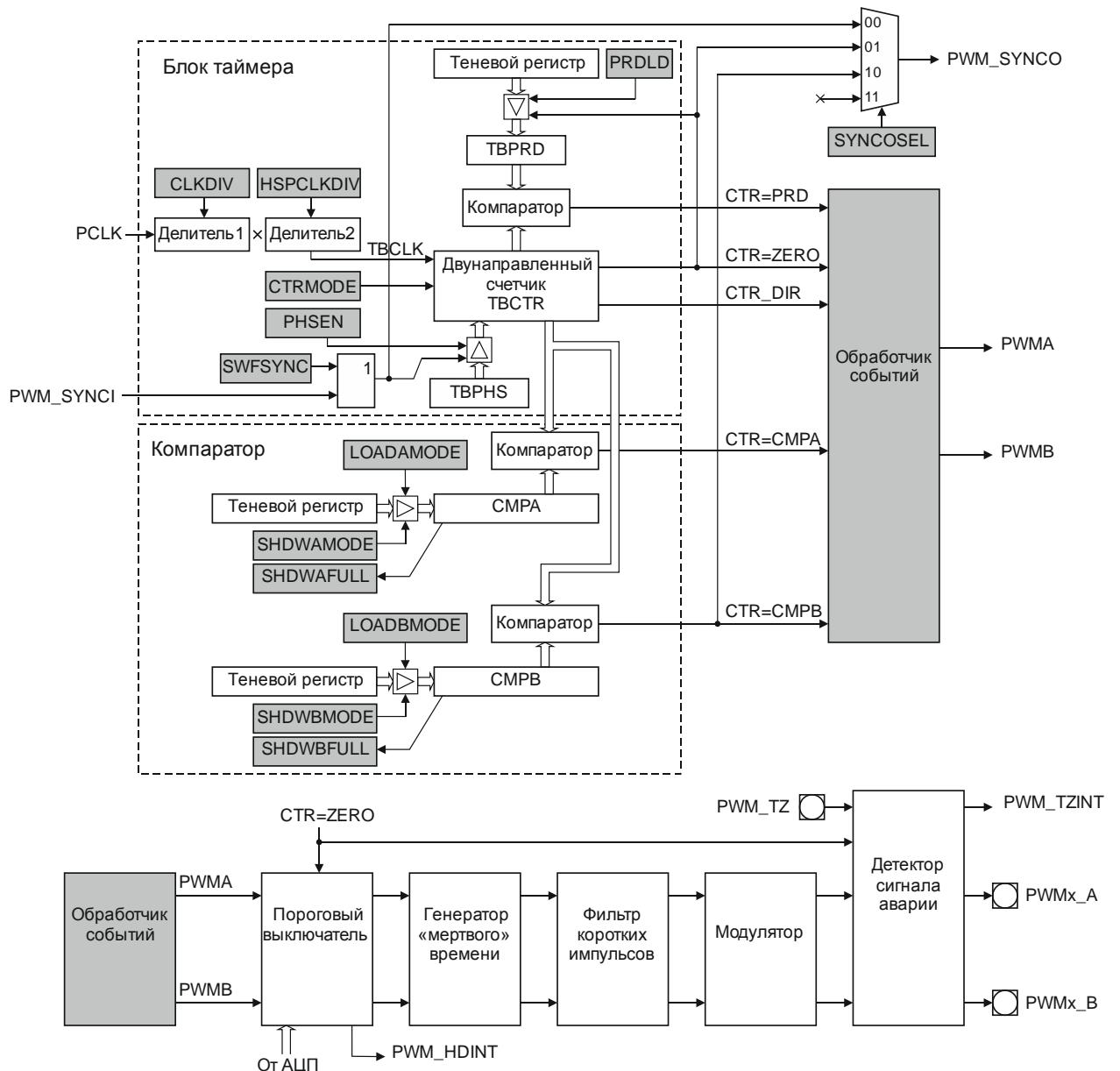

| 14 Блоки ШИМ .....                                         | 75  |

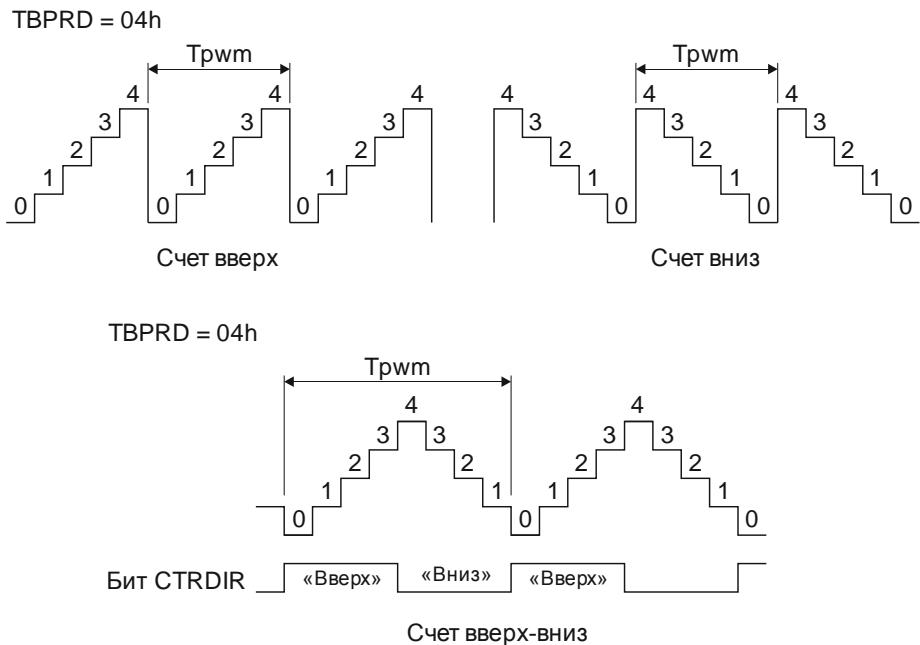

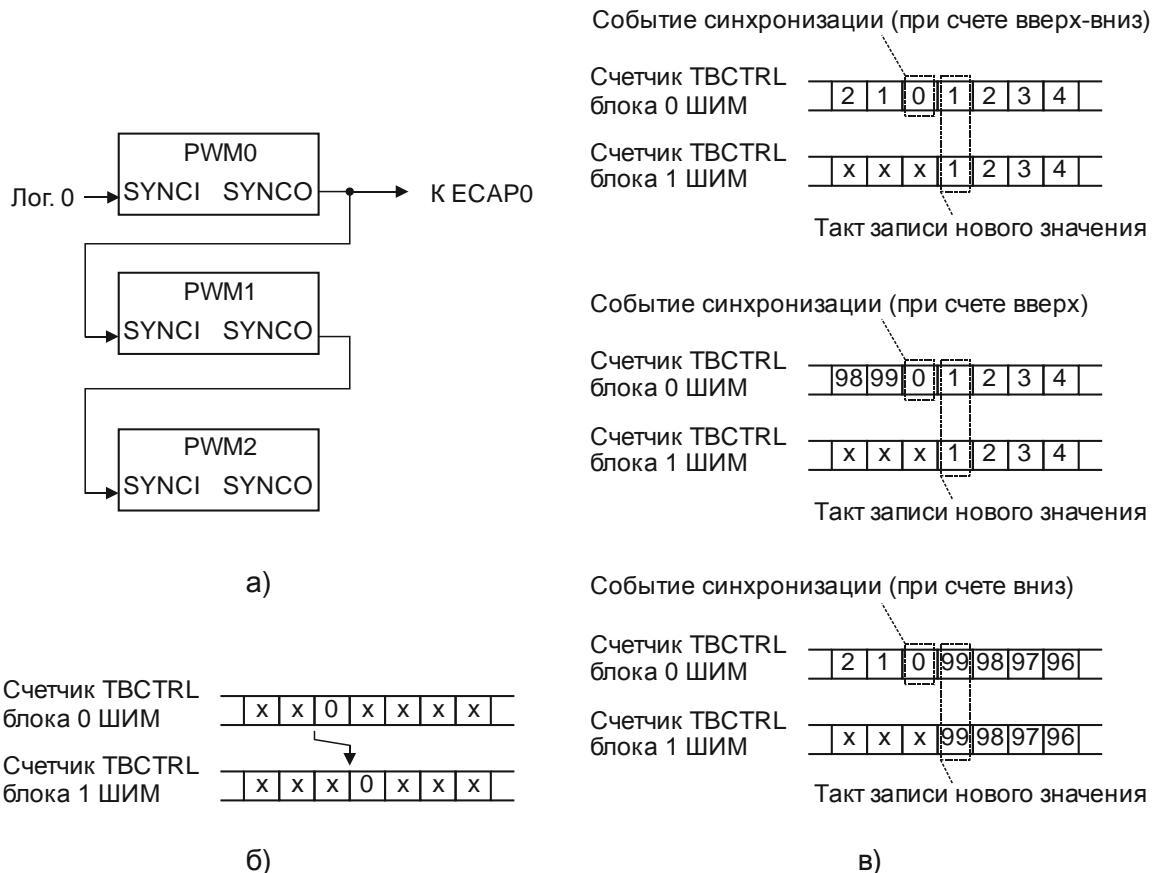

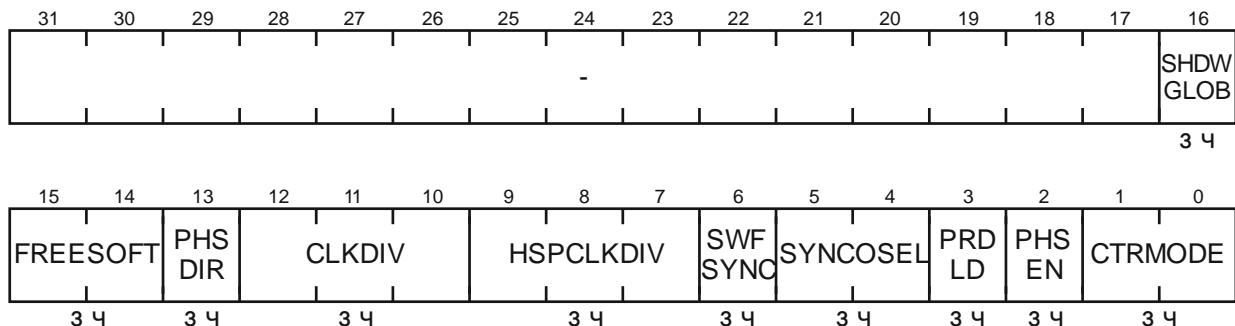

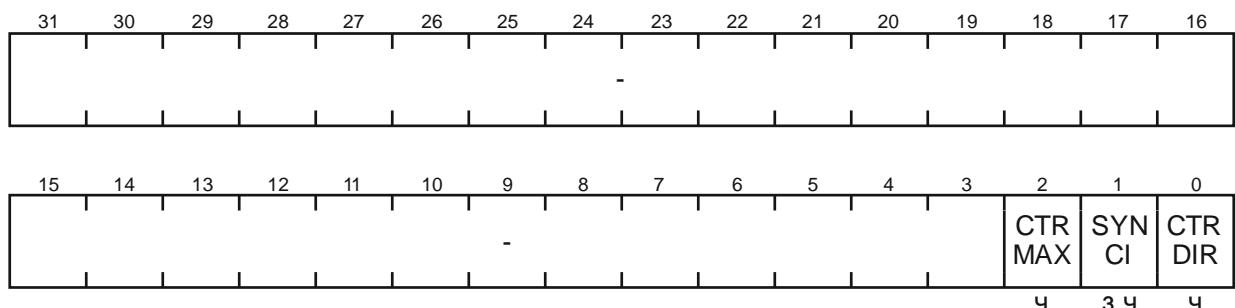

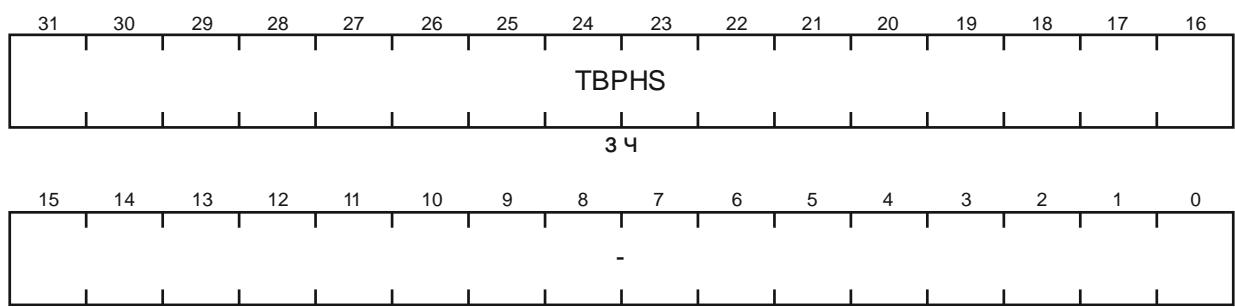

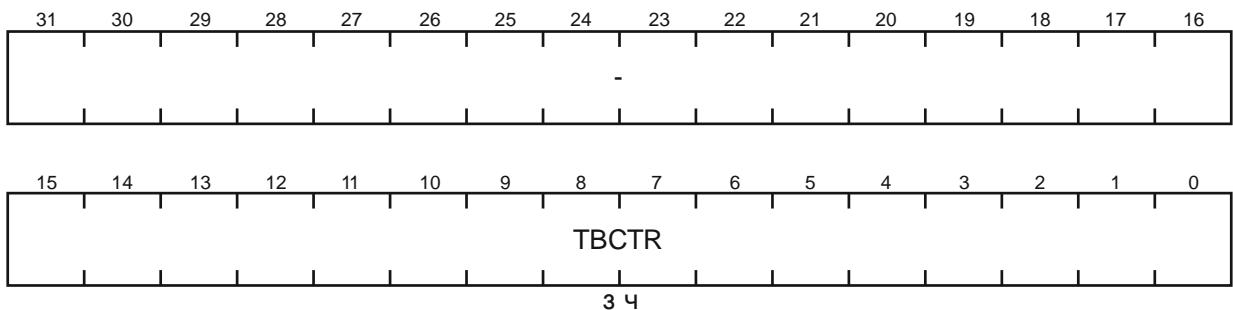

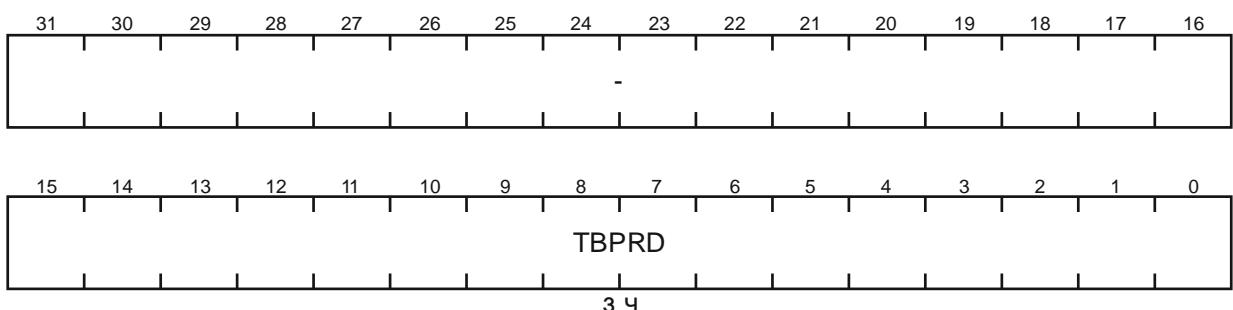

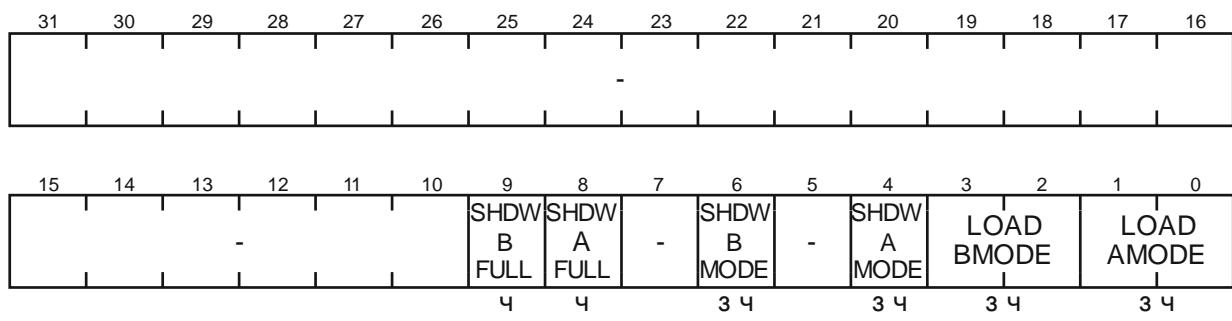

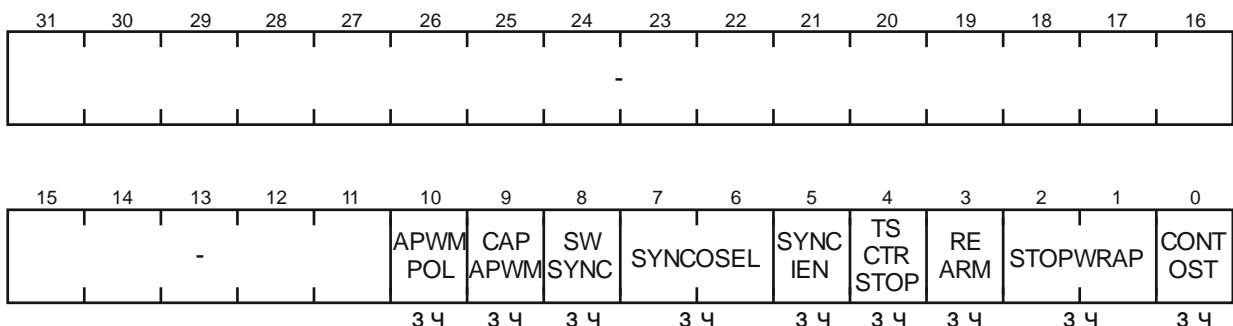

| 14.1 Таймер.....                                           | 76  |

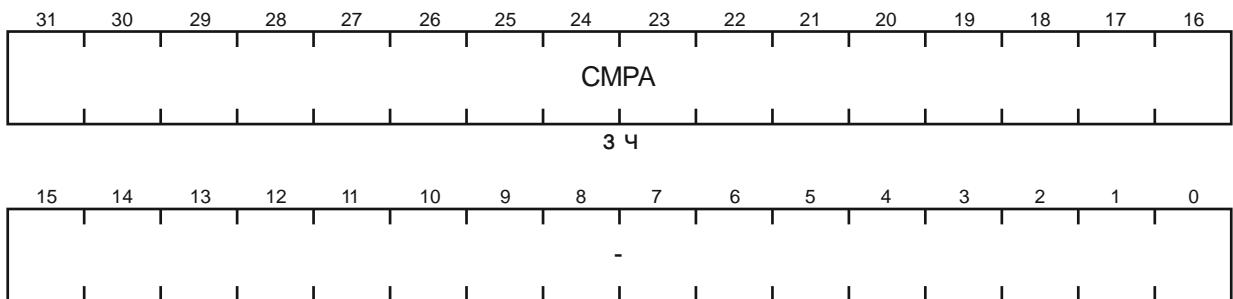

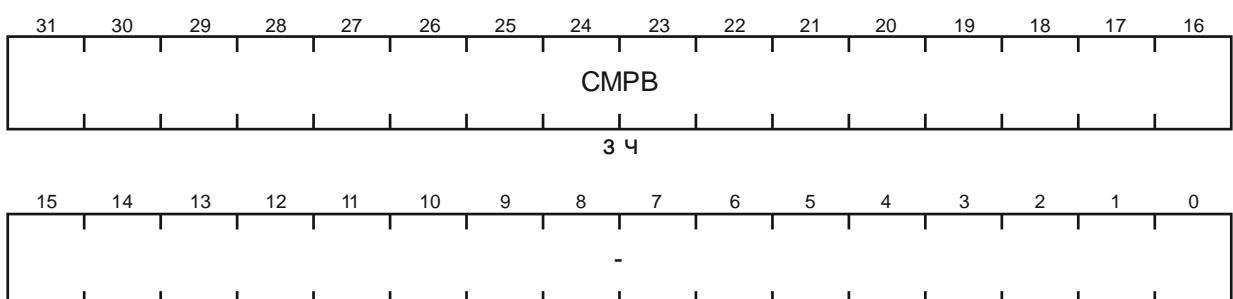

| 14.2 Компаратор.....                                       | 79  |

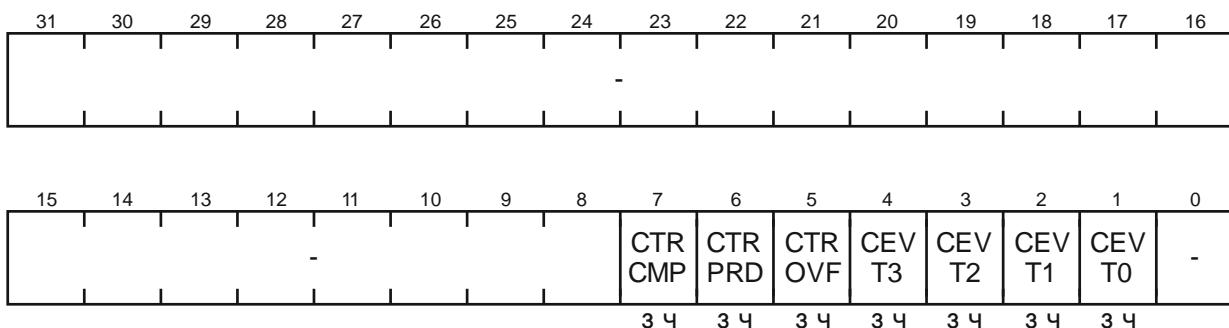

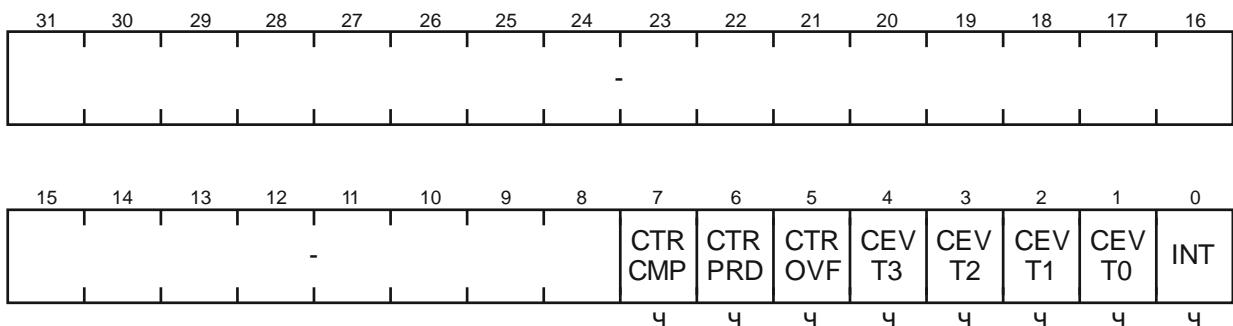

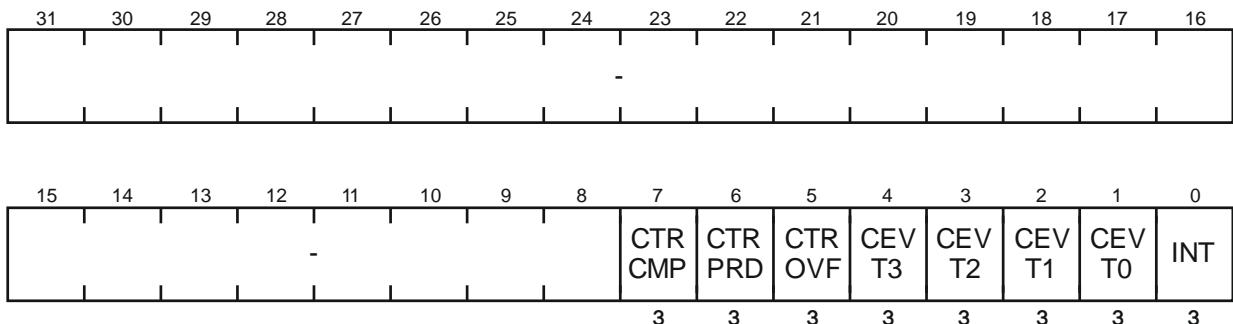

| 14.3 Обработчик событий .....                              | 80  |

| 14.4 Пороговый выключатель.....                            | 83  |

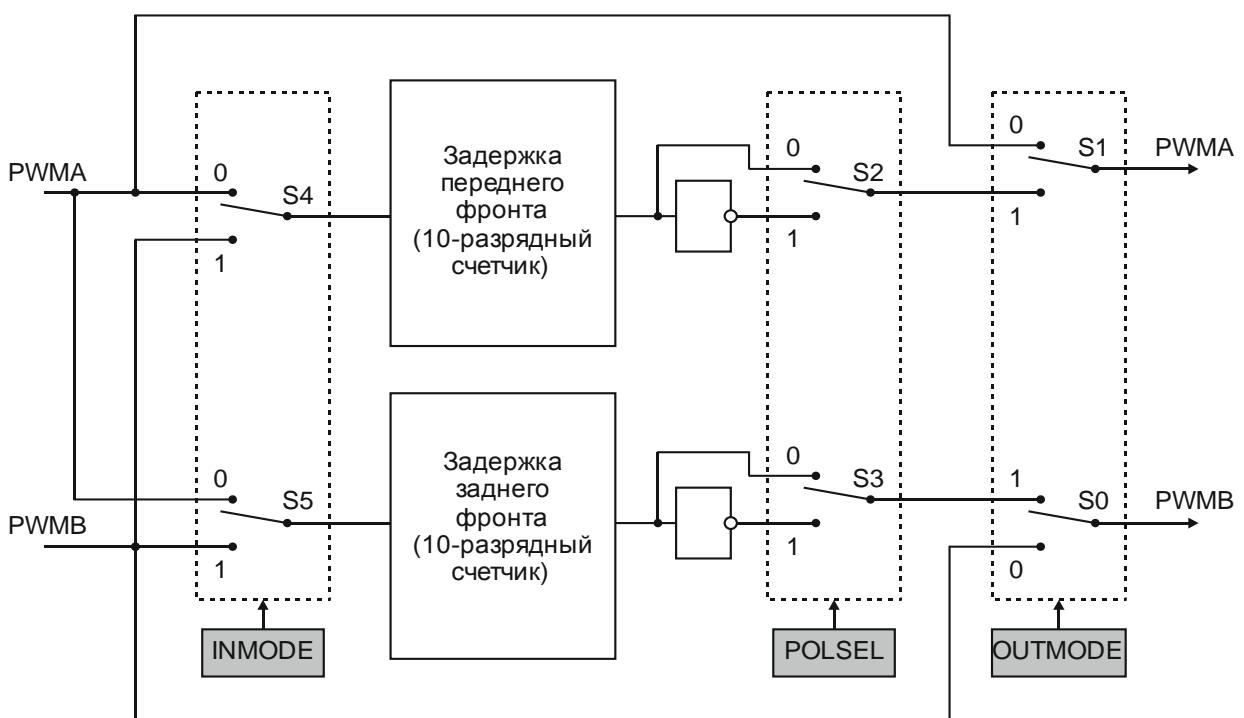

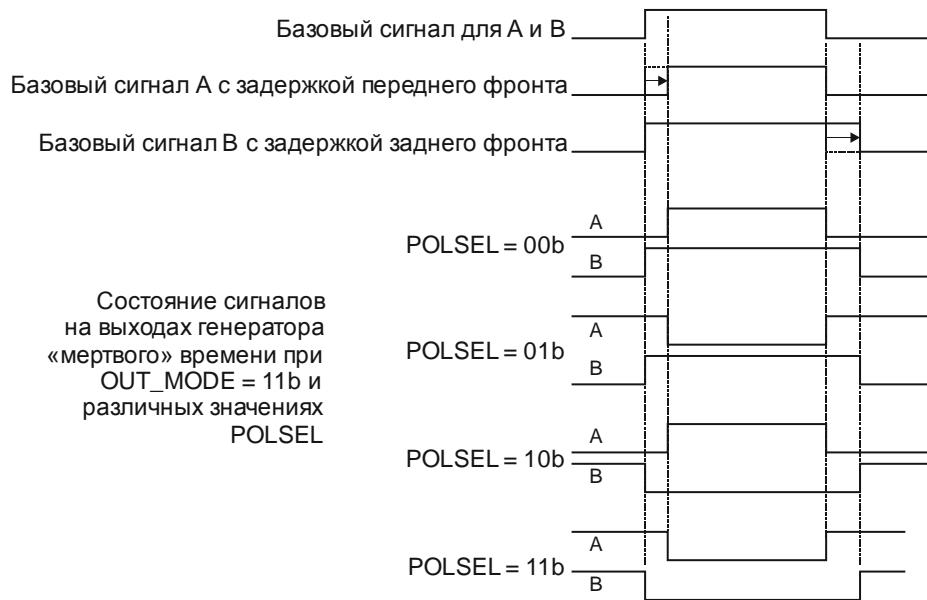

| 14.5 Генератор задержки ШИМ .....                          | 85  |

| 14.6 Фильтр коротких импульсов .....                       | 86  |

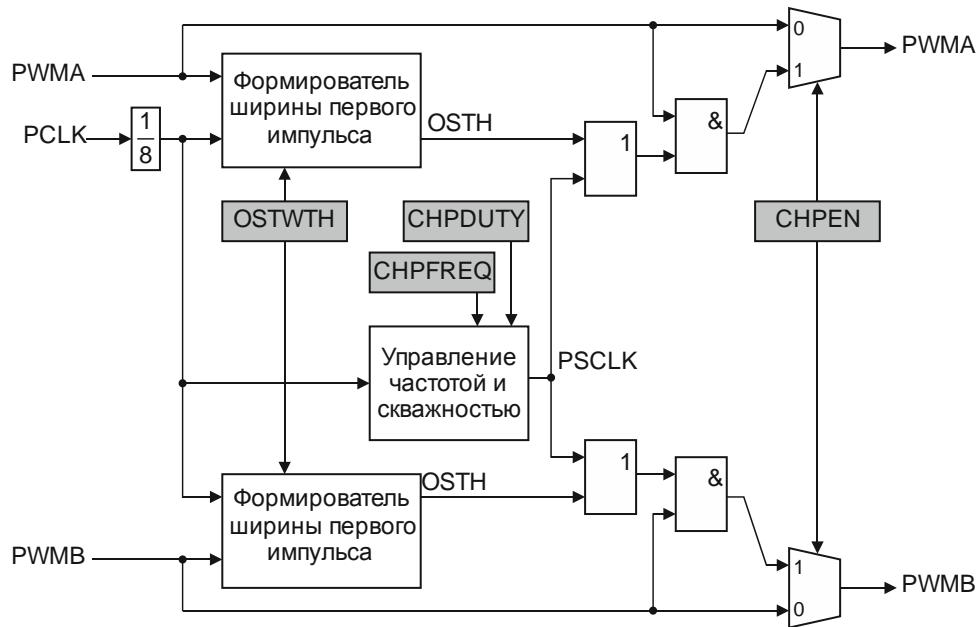

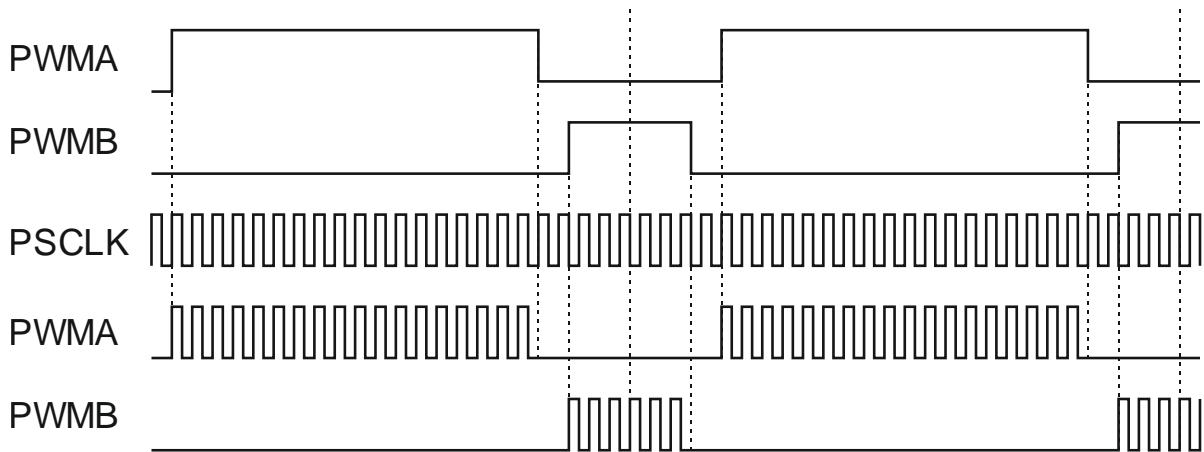

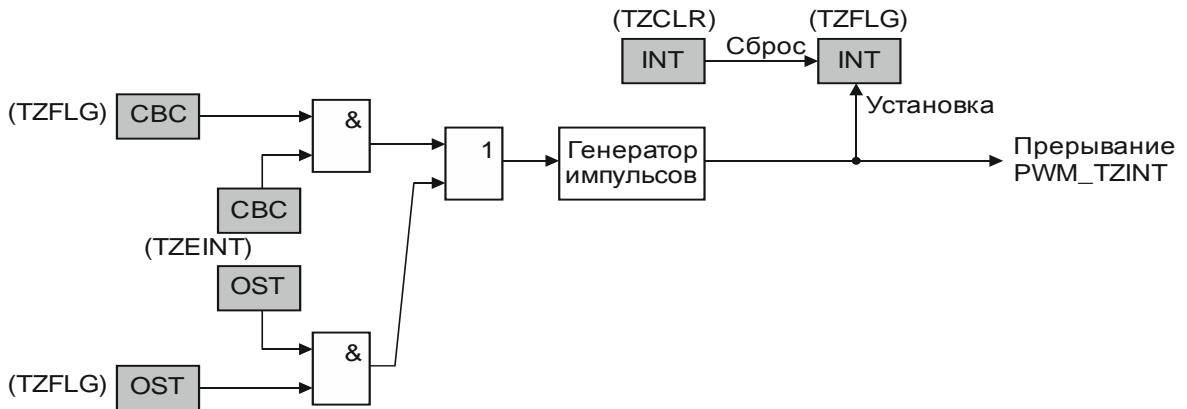

| 14.7 Модулятор .....                                       | 86  |

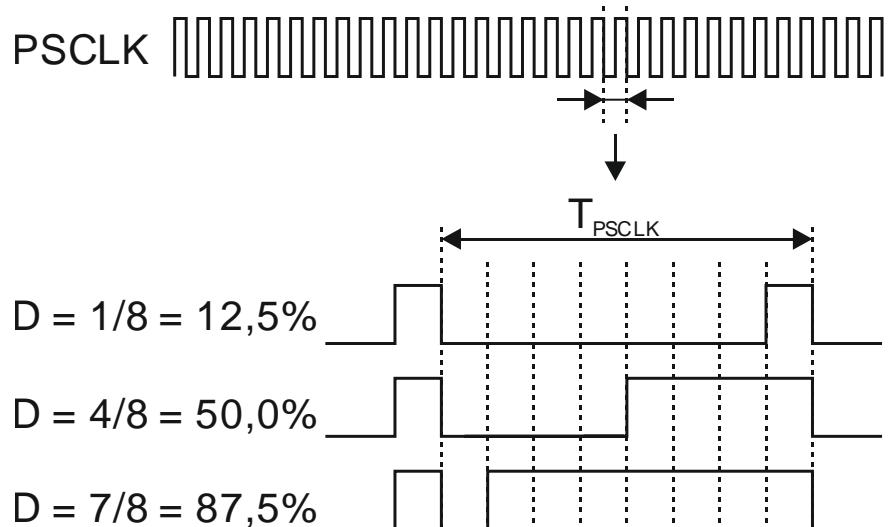

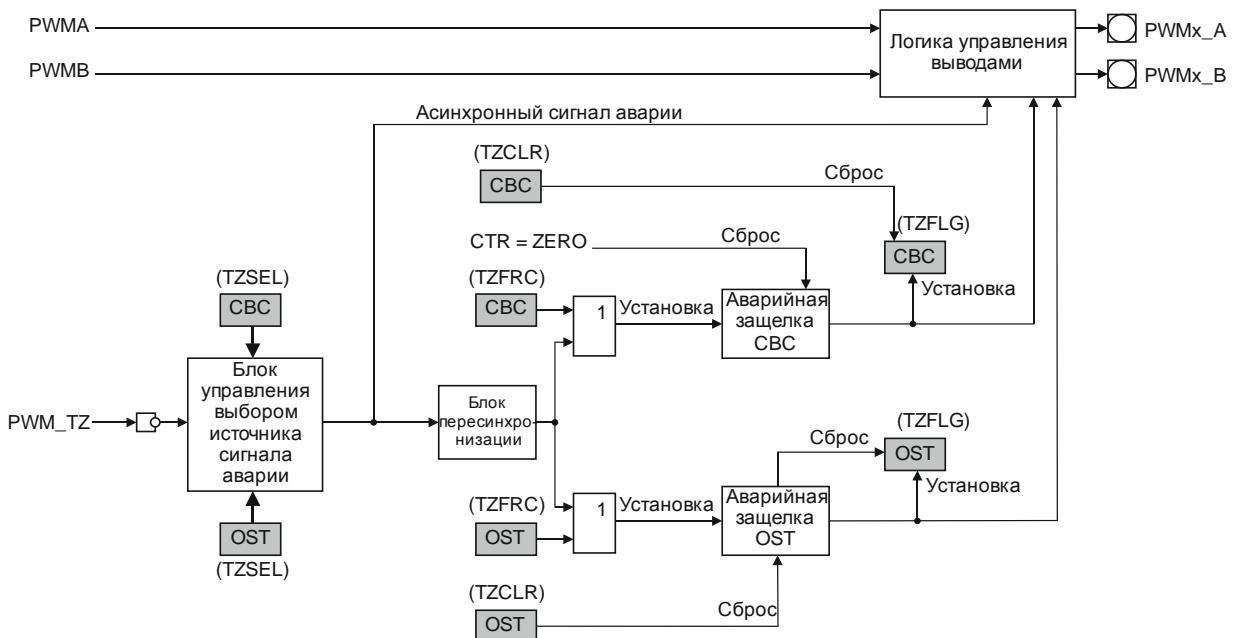

| 14.8 Детектор сигнала аварии.....                          | 89  |

| 14.9 Триггер событий .....                                 | 90  |

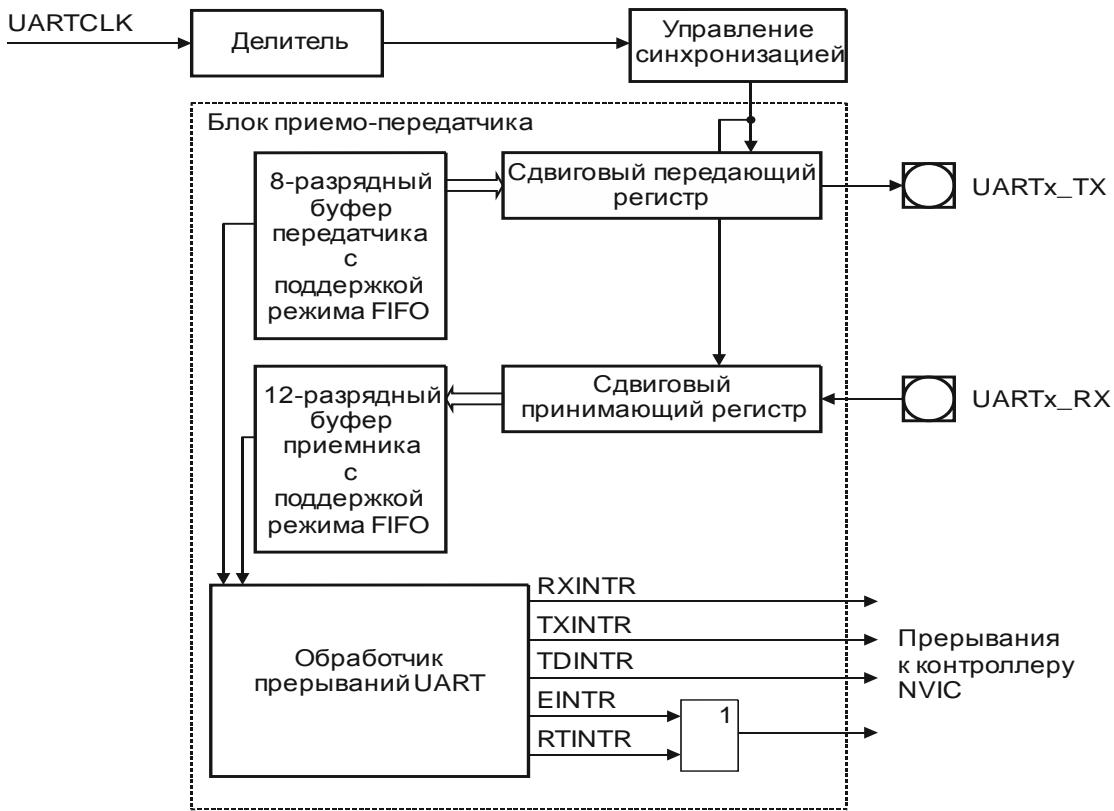

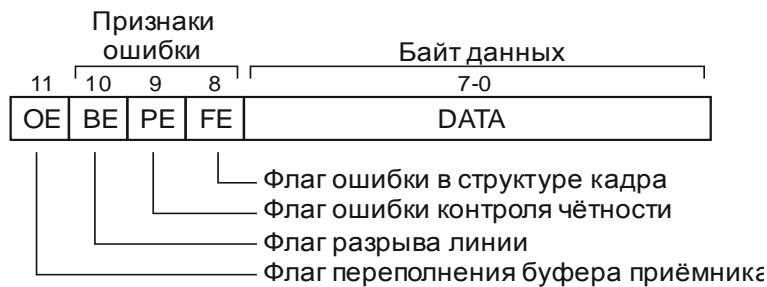

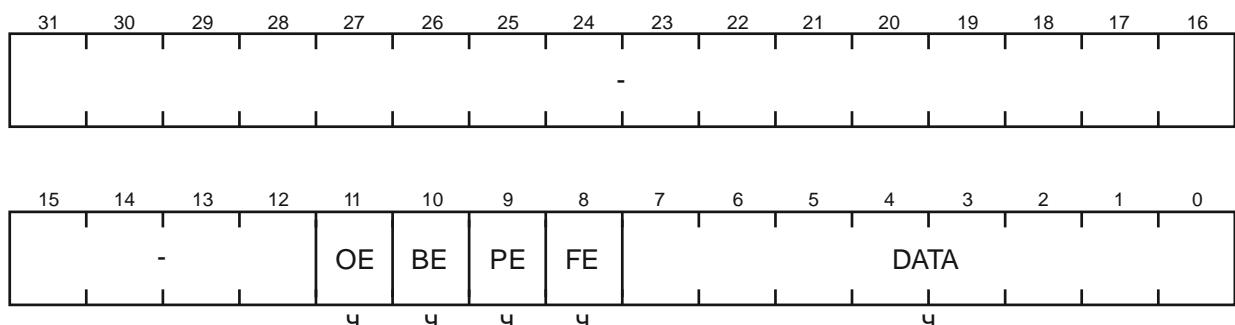

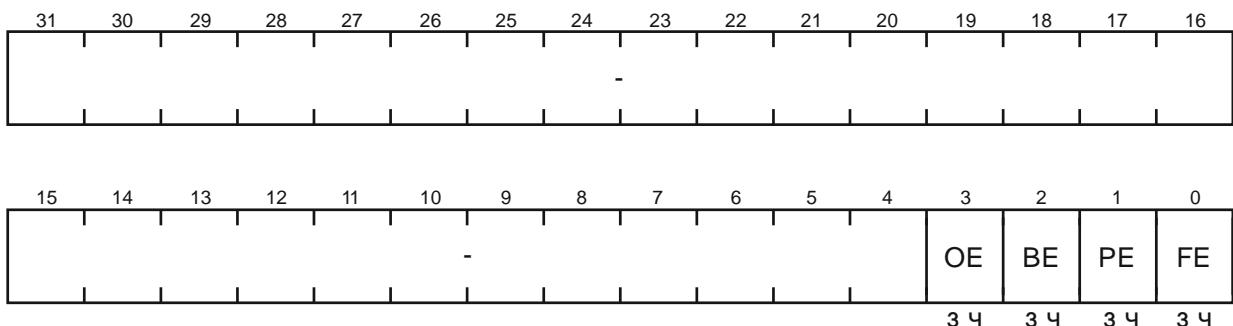

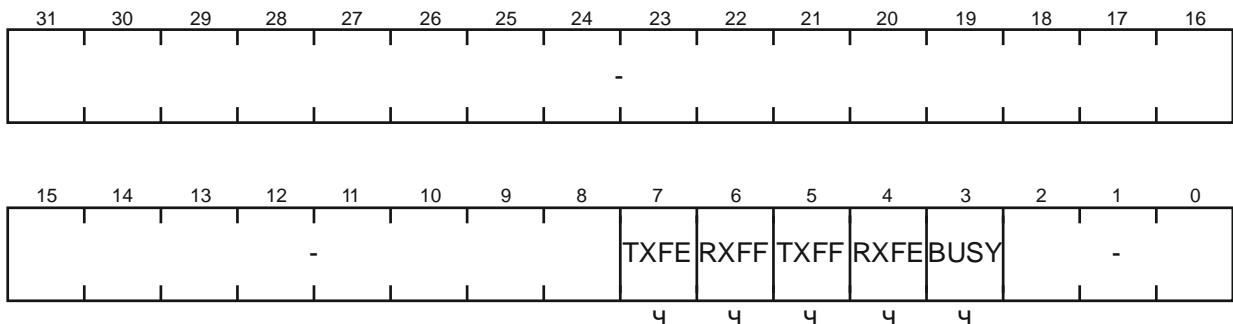

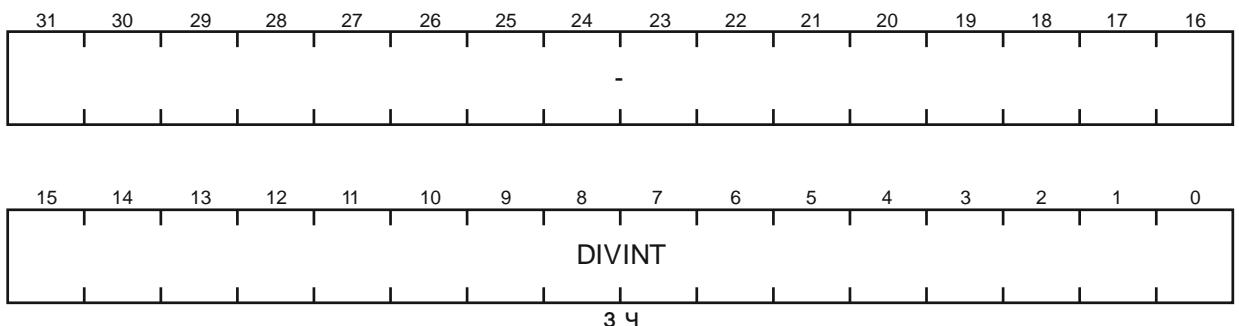

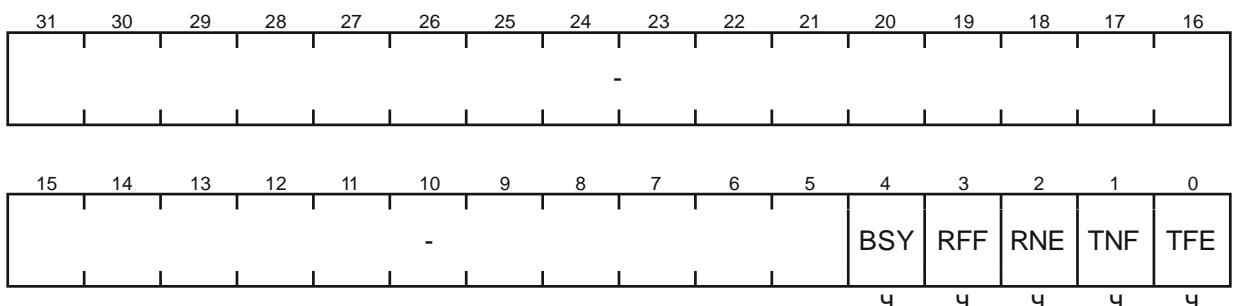

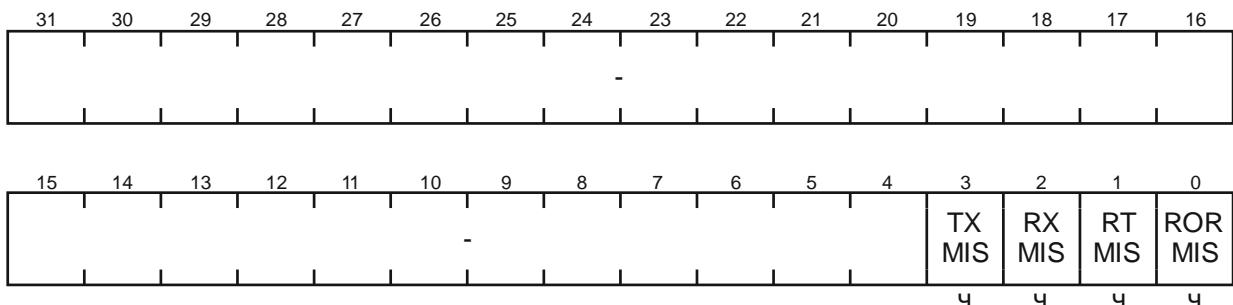

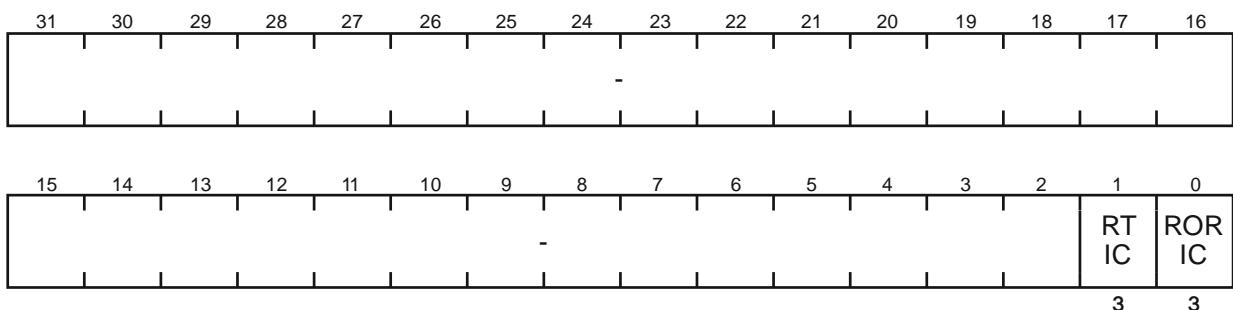

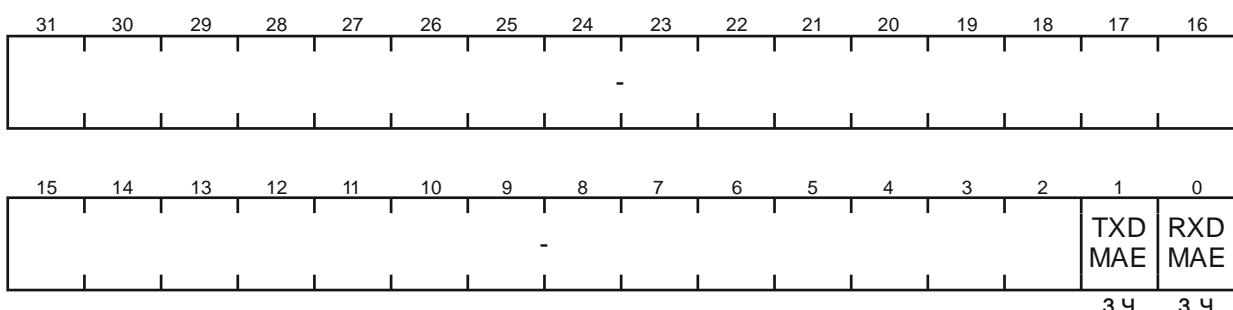

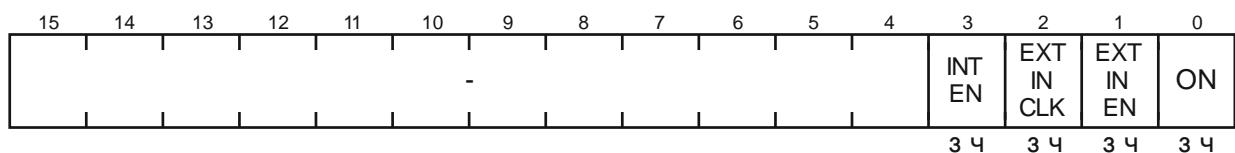

| 15 Приемопередатчик UART.....                              | 93  |

| 15.1 Функционирование блока UART .....                     | 93  |

| 15.2 Интерфейс прямого доступа к памяти .....              | 97  |

| 15.3 Прерывания .....                                      | 98  |

| 15.4 Программирование .....                                | 99  |

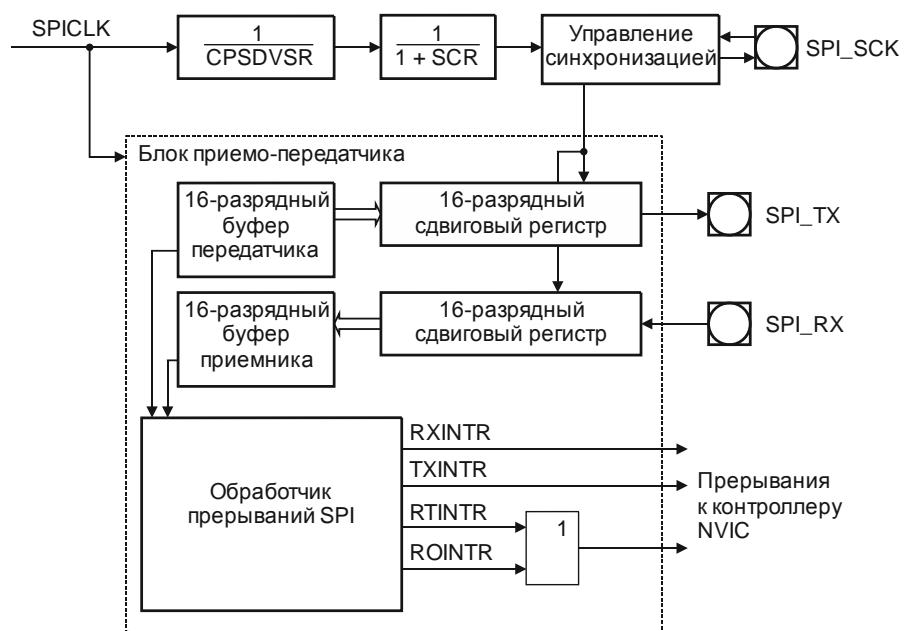

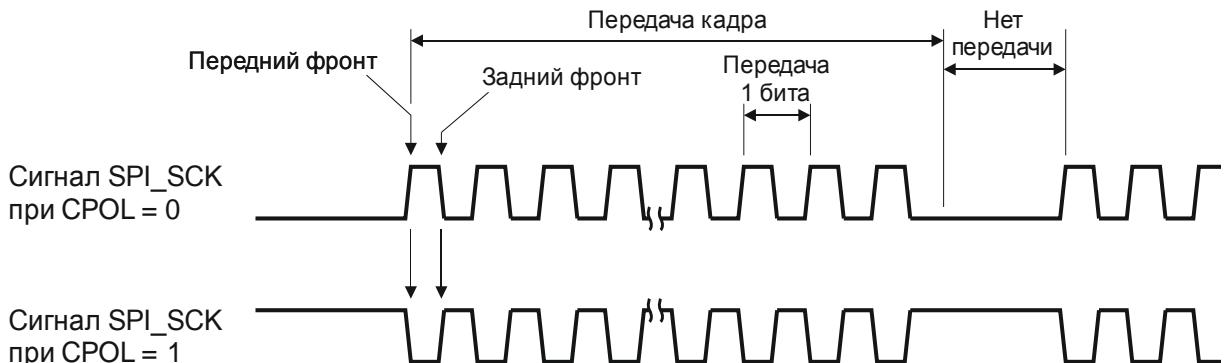

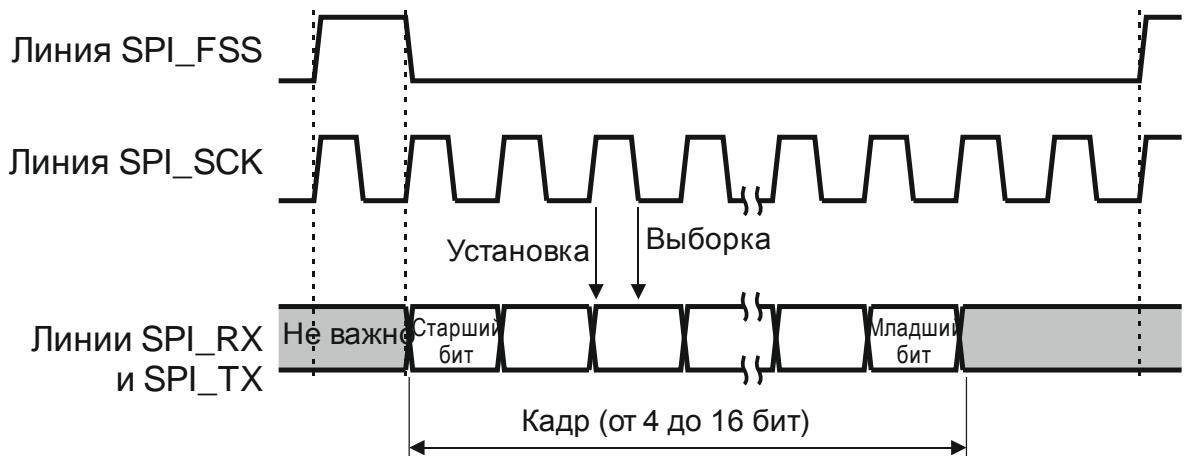

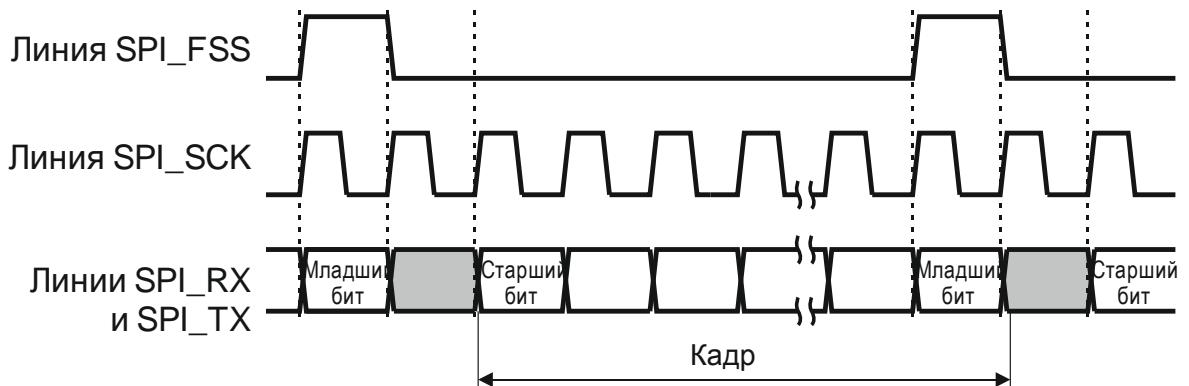

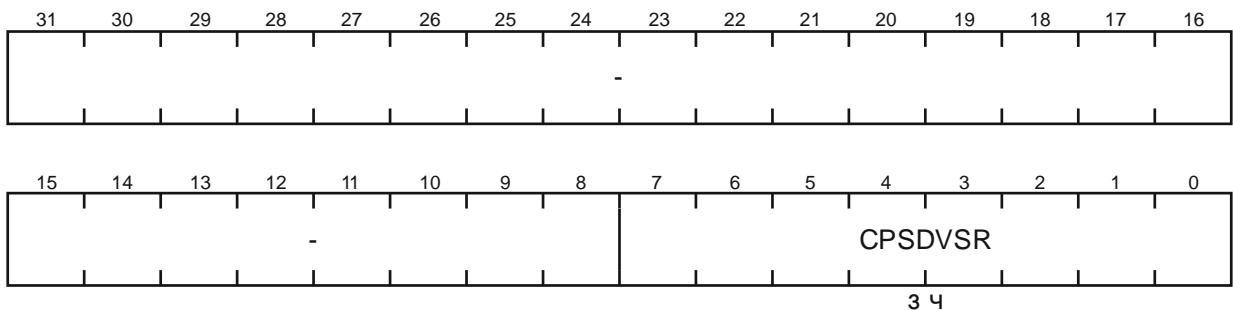

| 16 Контроллер интерфейса SPI .....                         | 100 |

| 16.1 Структура контроллера SPI .....                       | 100 |

| 16.2 Интерфейс прямого доступа к памяти .....              | 102 |

| 16.3 Функционирование .....                                | 102 |

| 16.4 Прерывания .....                                      | 106 |

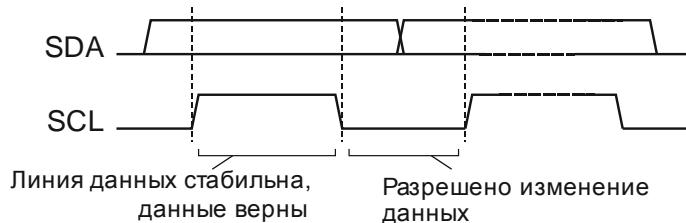

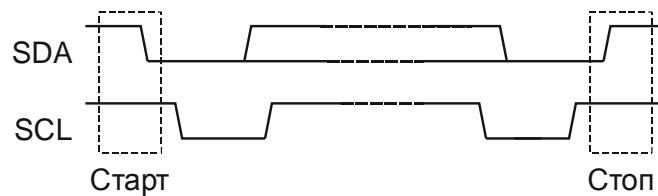

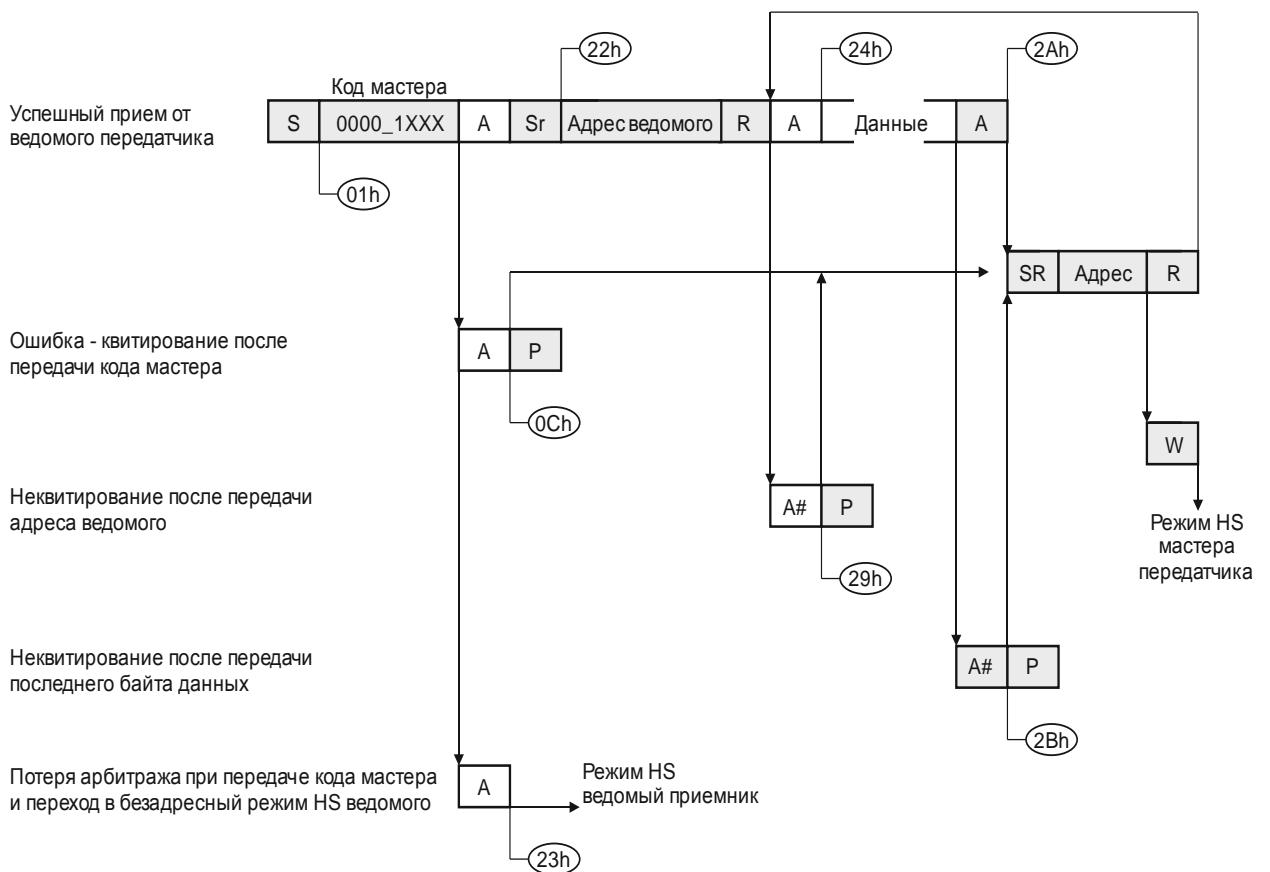

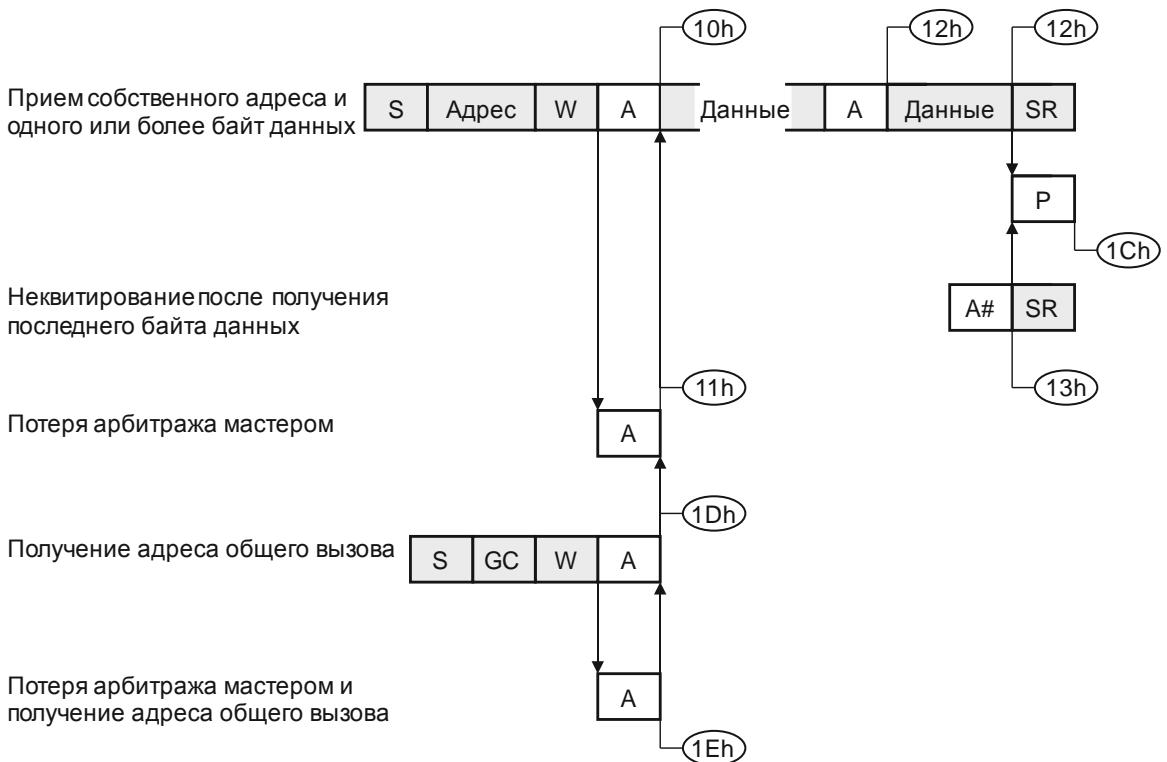

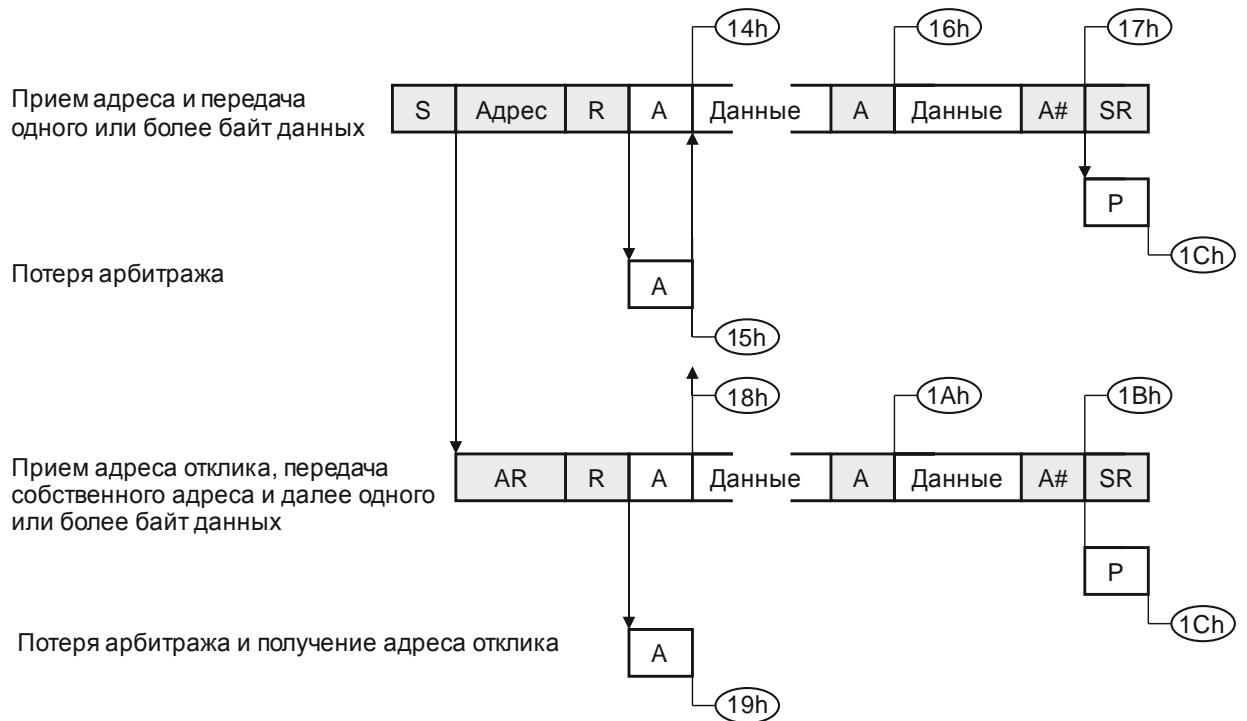

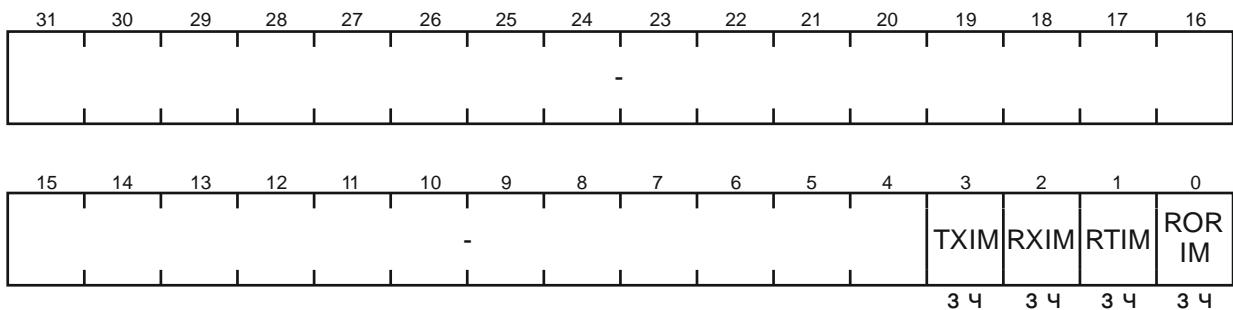

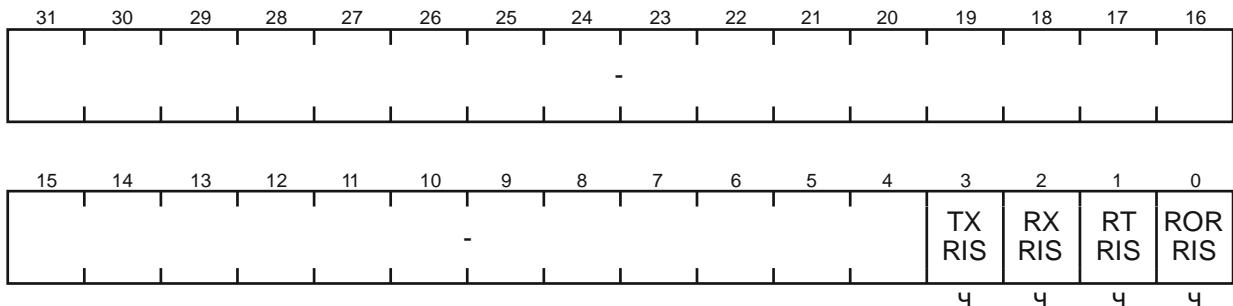

| 17 Контроллер интерфейса I2C .....                         | 108 |

| 17.1 Протокол шины.....                                    | 108 |

| 17.2 Функциональное описание .....                         | 115 |

| 17.3 Инициализация и функционирование .....                | 118 |

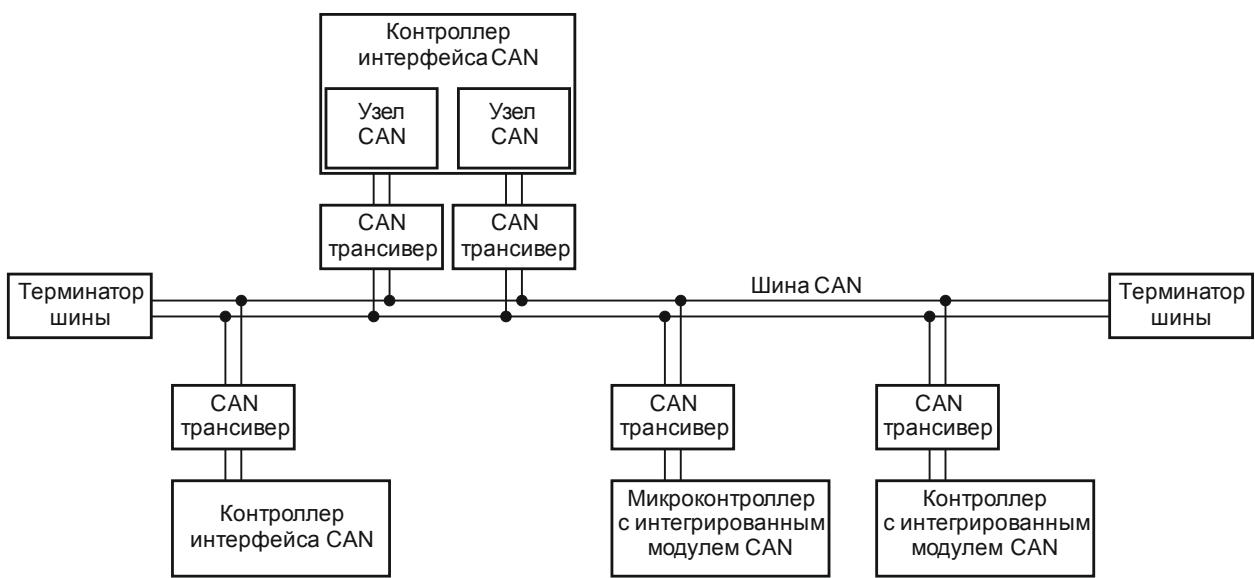

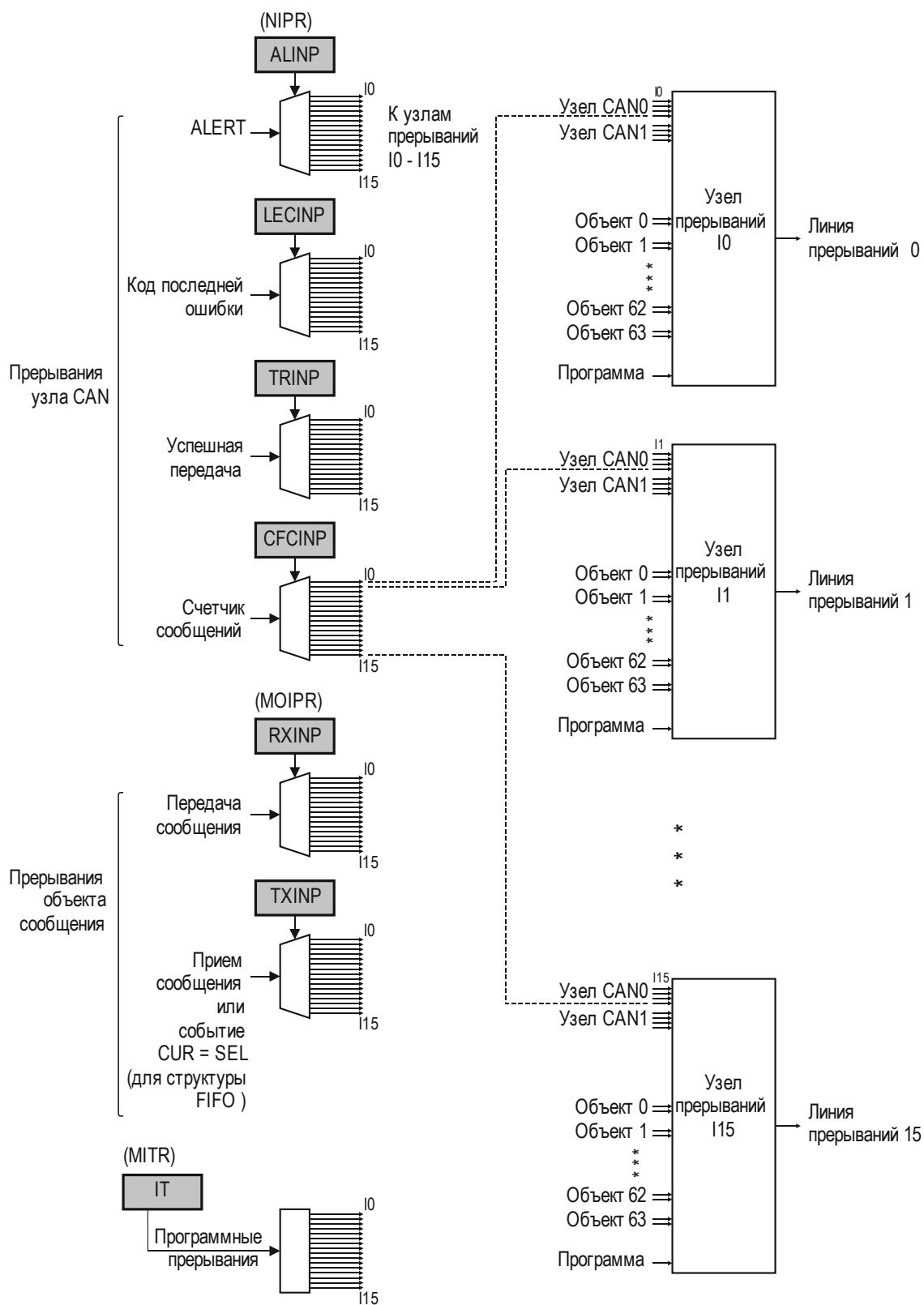

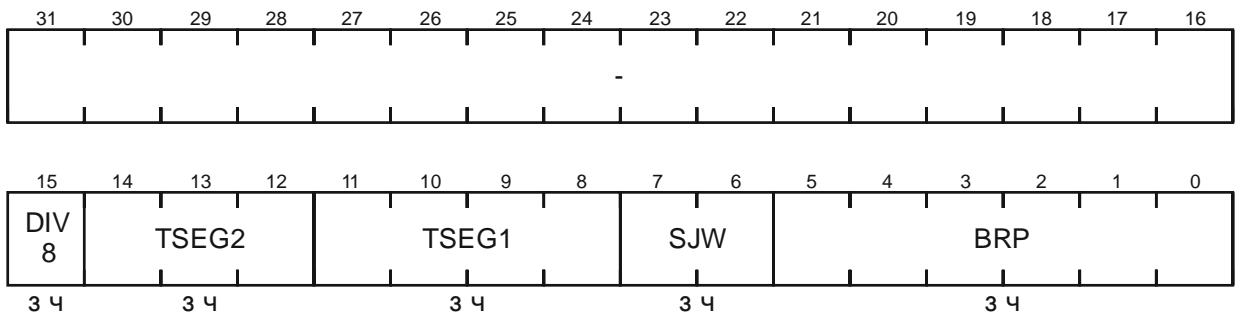

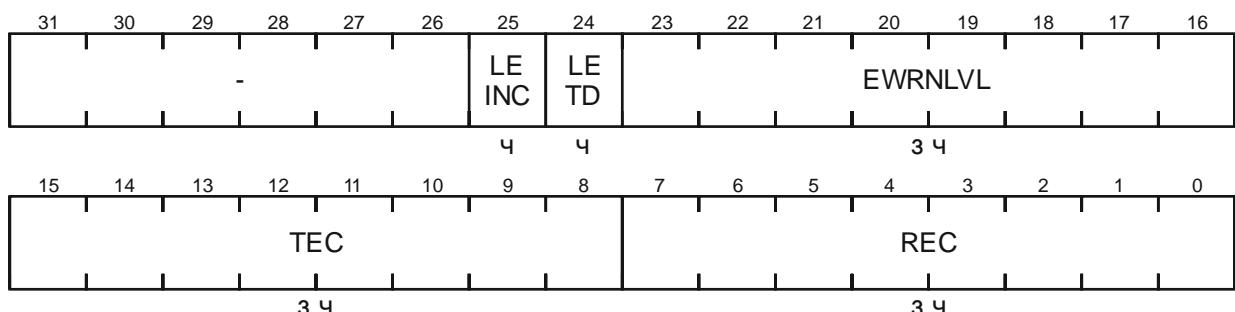

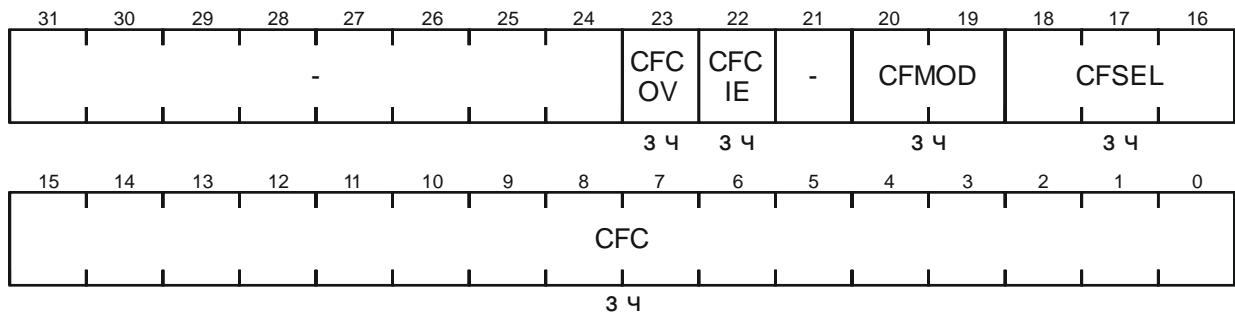

| 18 Контроллер интерфейса CAN.....                          | 132 |

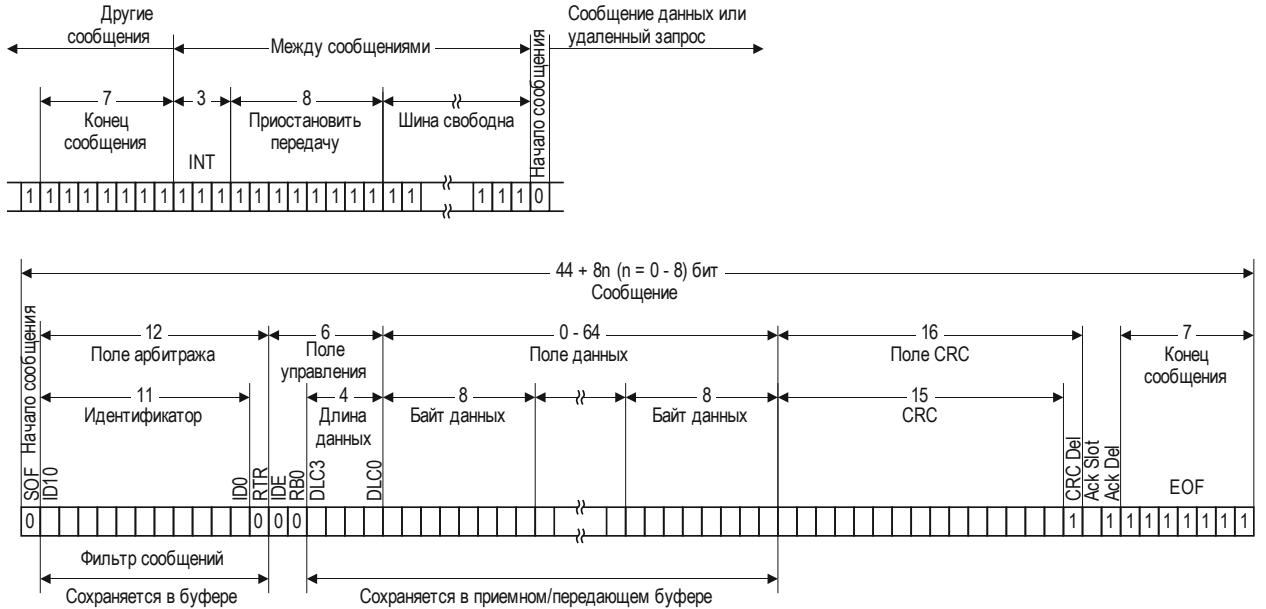

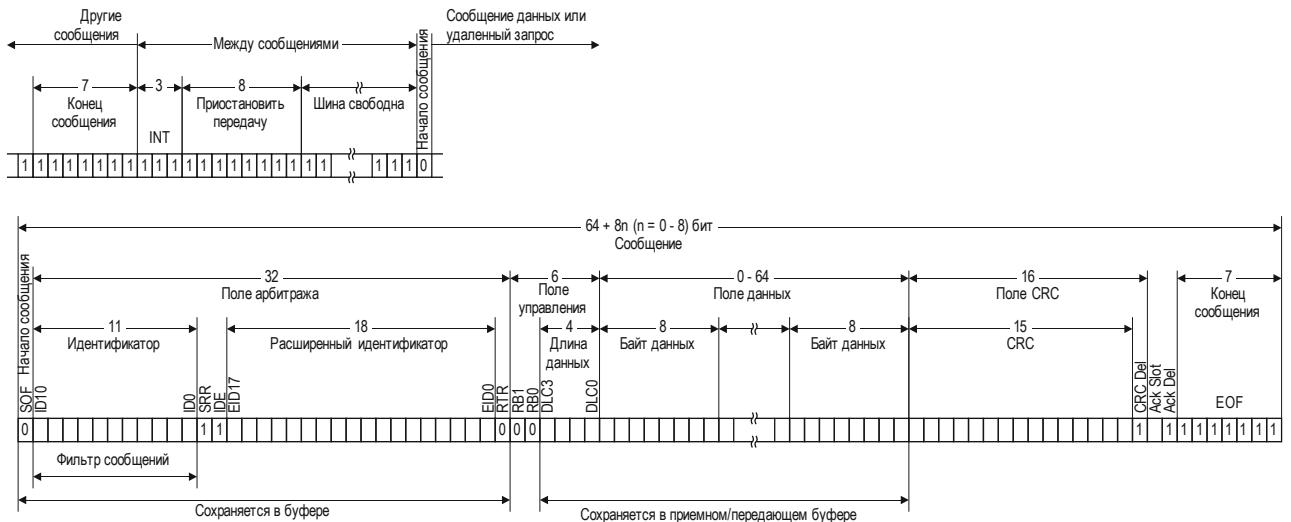

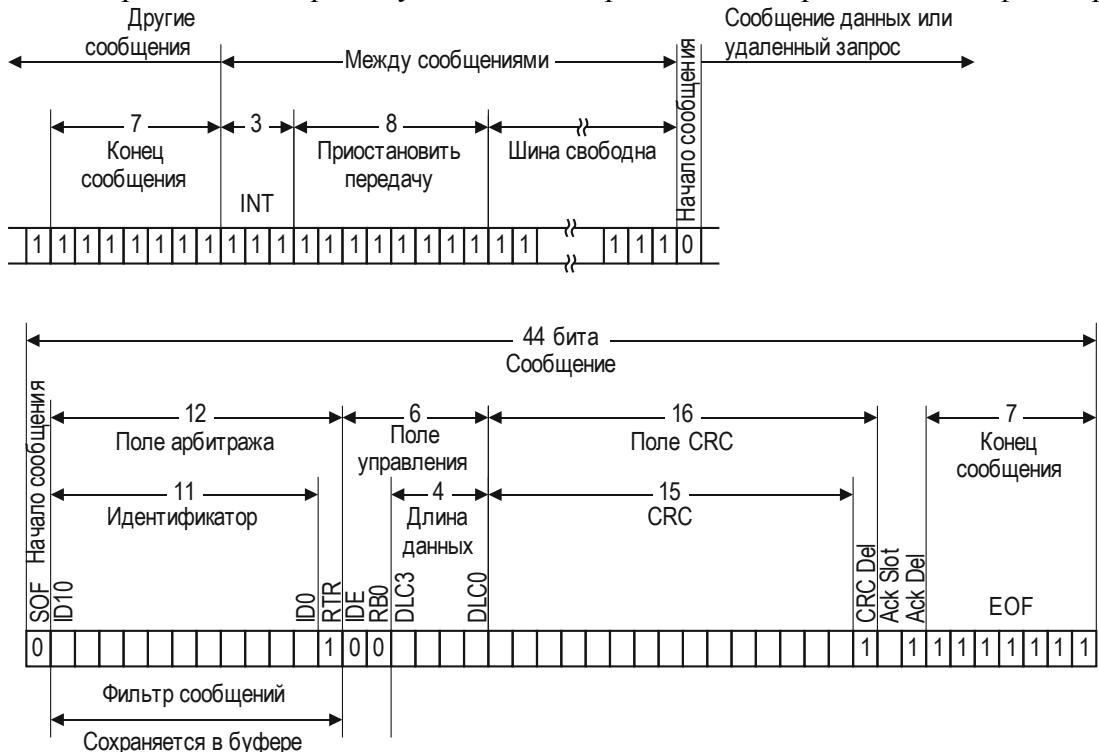

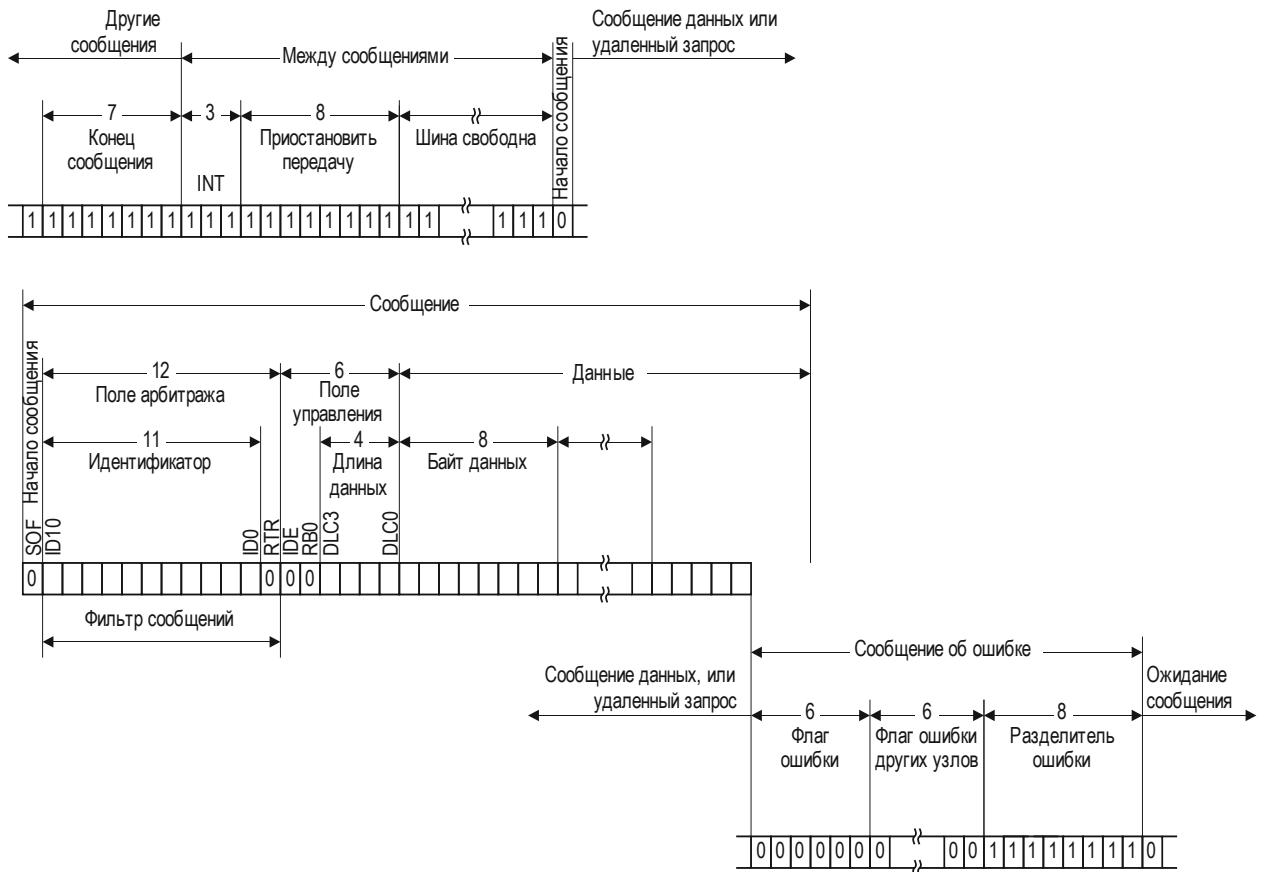

| 18.1 Протокол CAN .....                                    | 132 |

| 18.2 Структура и функционирование контроллера CAN.....     | 138 |

| 18.3 Узел CAN.....                                         | 144 |

| 18.4 Объекты сообщений .....                               | 150 |

| 18.5 Прием и передача сообщений.....                       | 153 |

| 18.6 Фильтрация сообщений.....                             | 156 |

| 18.7 Удаленные запросы .....                               | 157 |

| 18.8 Дополнительные режимы передачи .....                  | 158 |

| 18.9 FIFO структура объектов сообщений .....               | 159 |

| 18.10 Режим шлюза.....                                     | 162 |

| 18.11 Прерывания объектов сообщений.....                   | 164 |

| 18.12 Программирование контроллера CAN .....               | 167 |

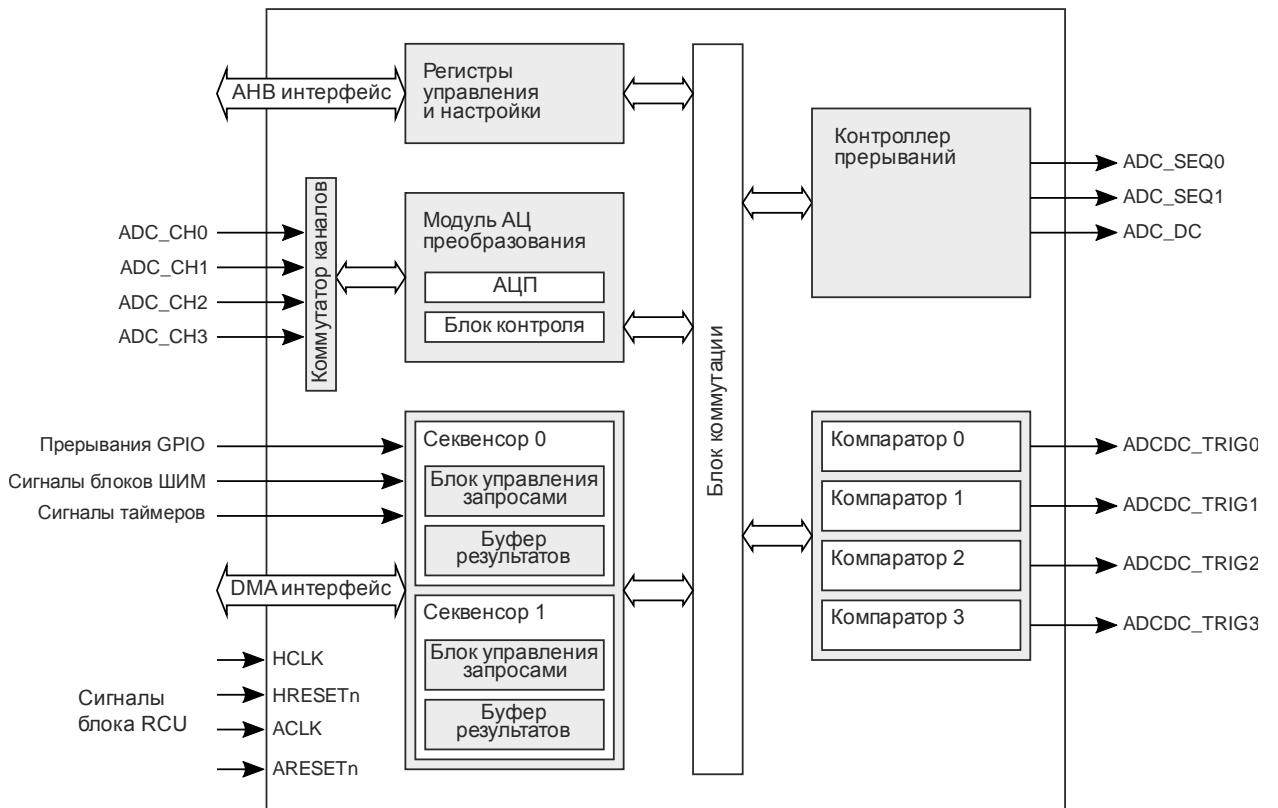

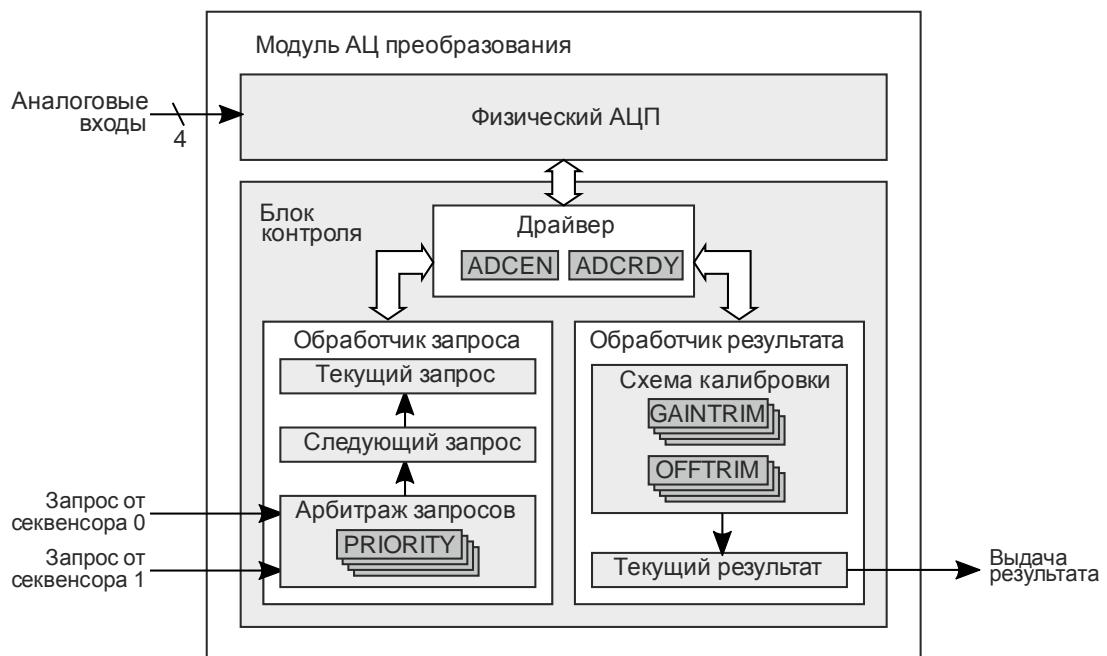

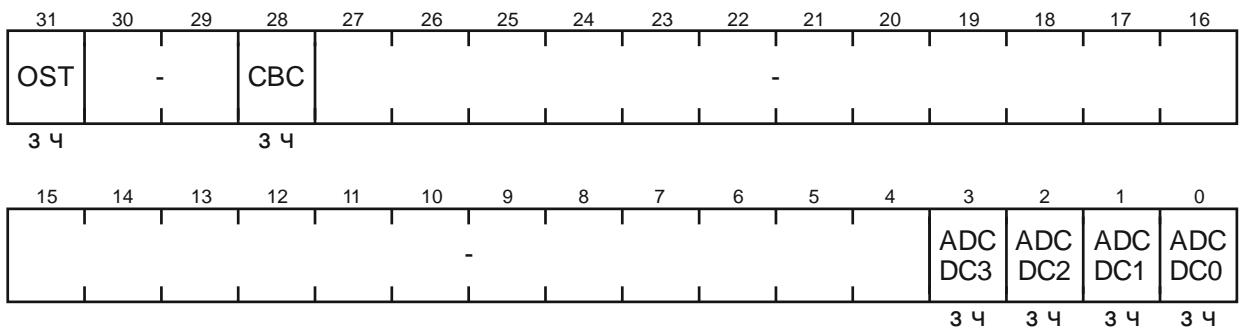

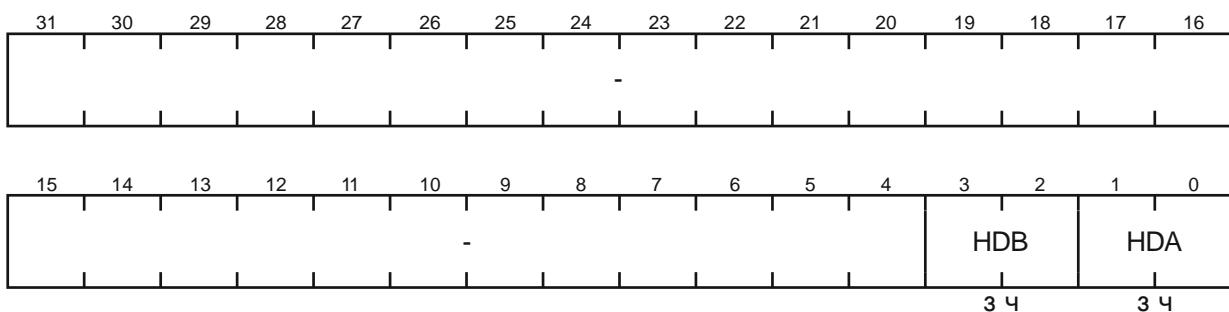

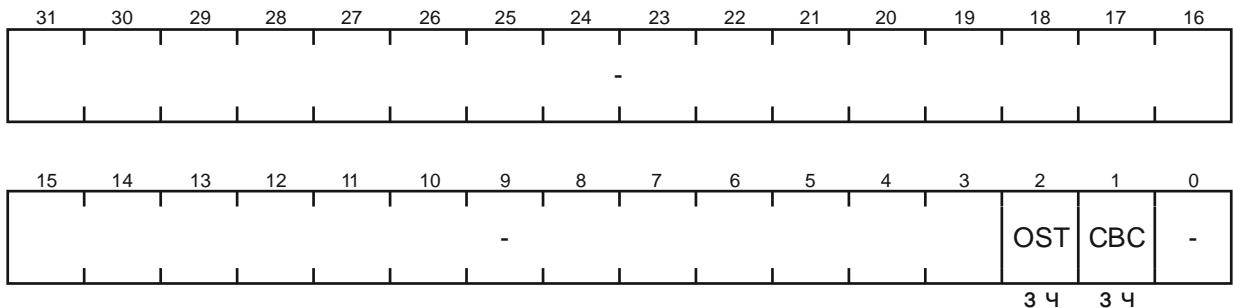

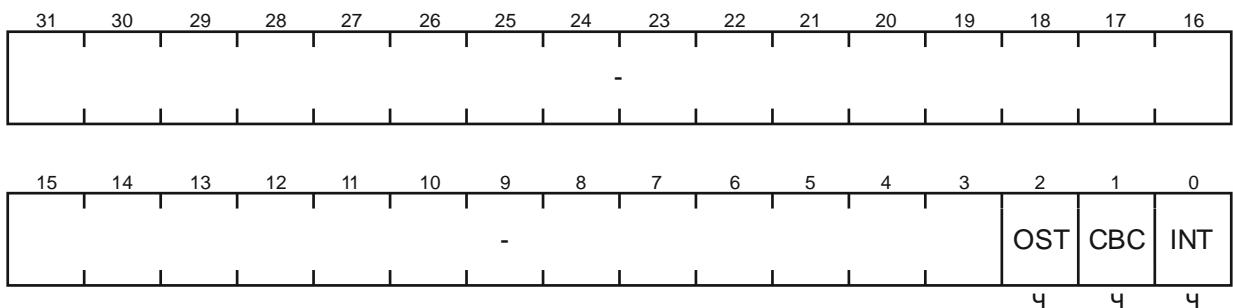

| 19 Блок АЦП .....                                          | 168 |

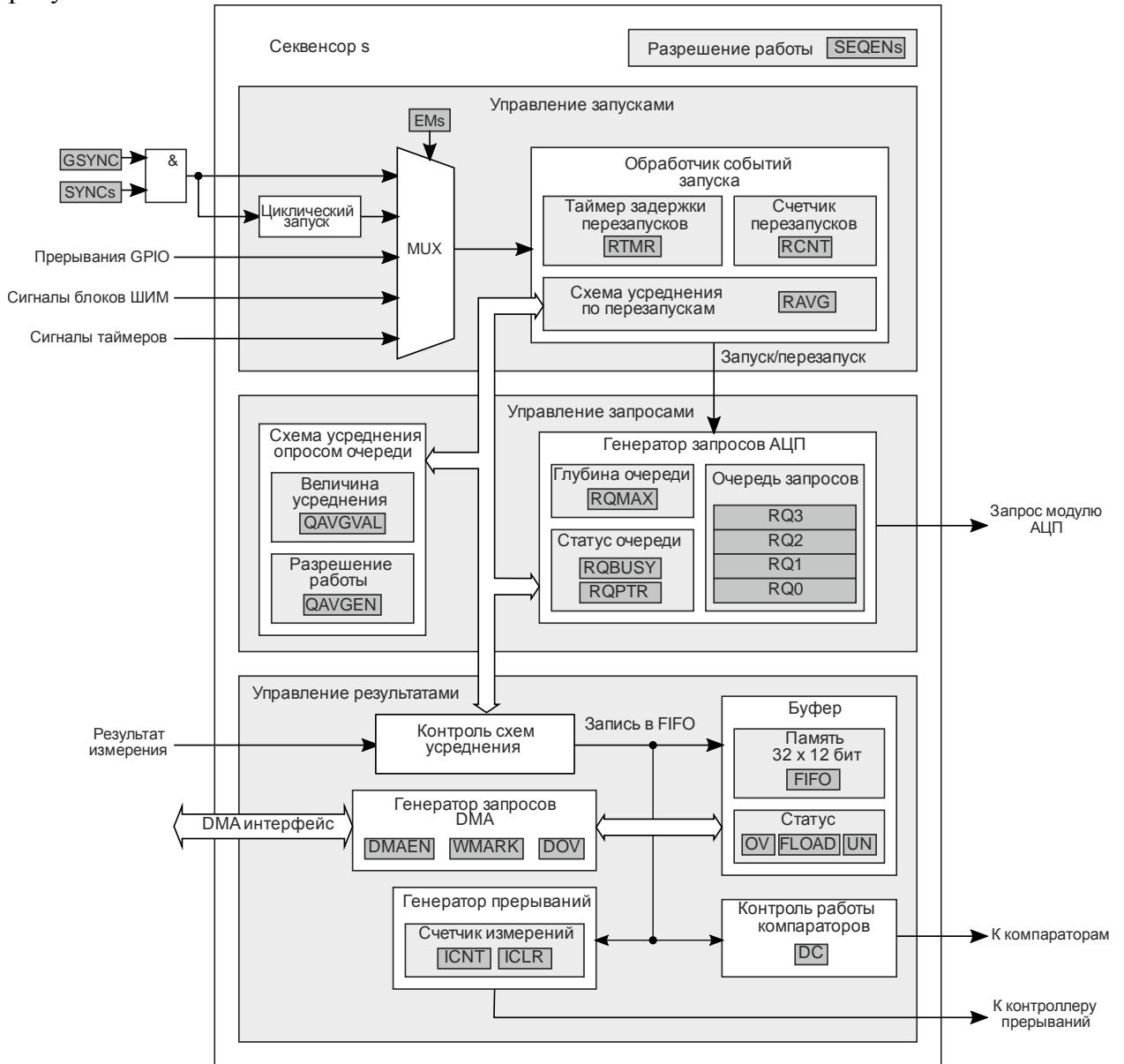

| 19.1 Секвенсор .....                                       | 169 |

| 19.2 Модуль АЦП .....                                      | 176 |

| 19.3 Цифровой компаратор .....                             | 178 |

| 19.4 Прерывания .....                                      | 181 |

| 19.5 Примеры работы блока АЦП .....                        | 182 |

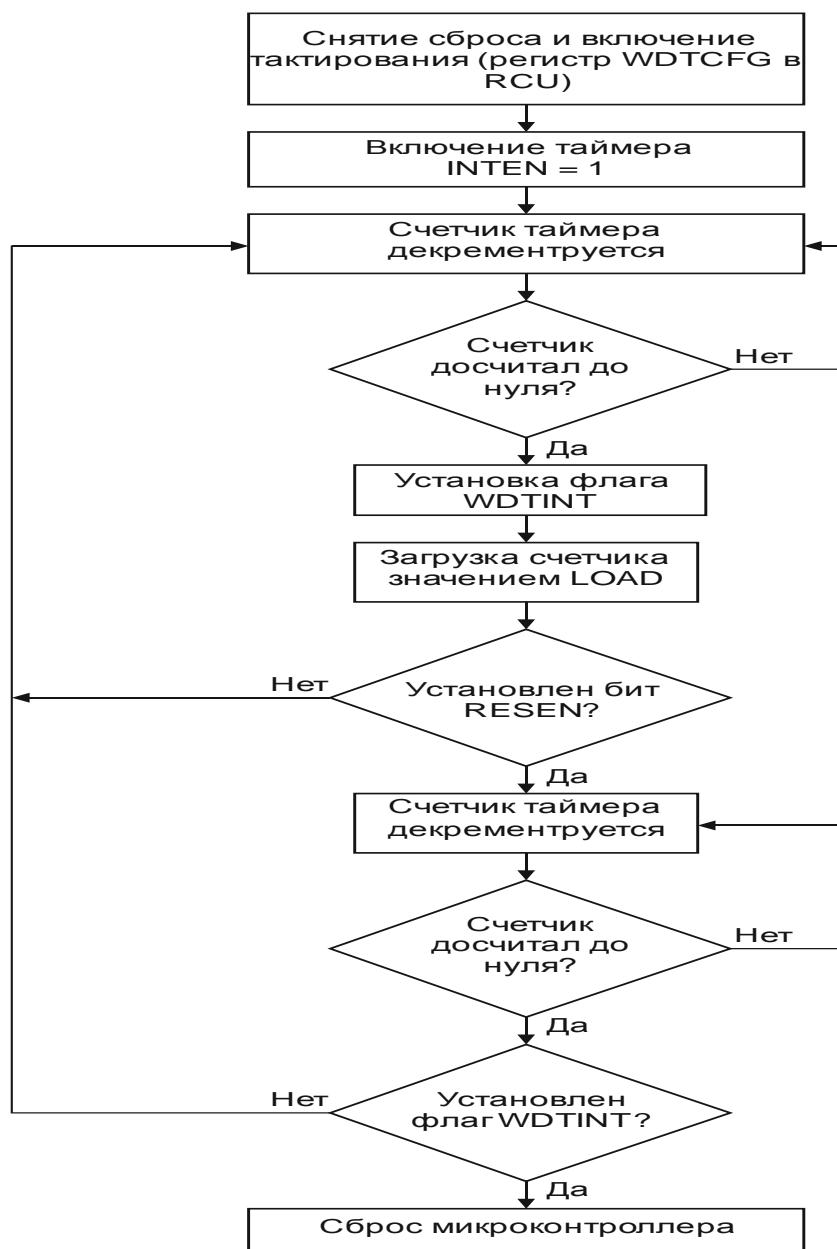

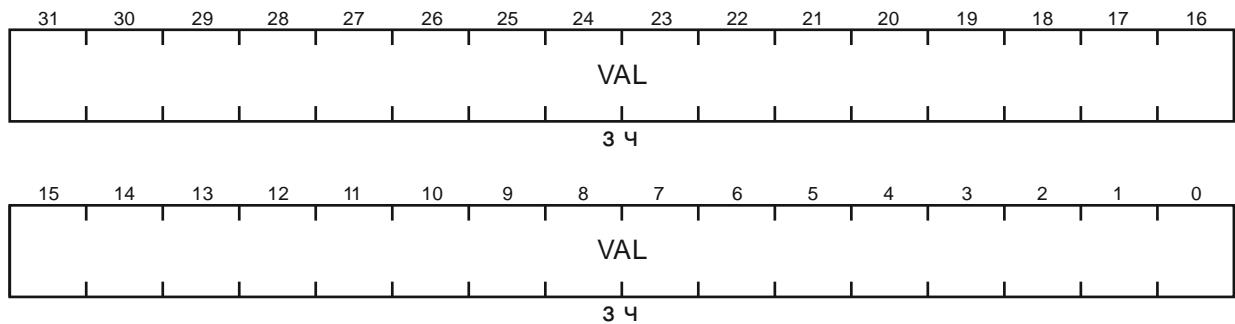

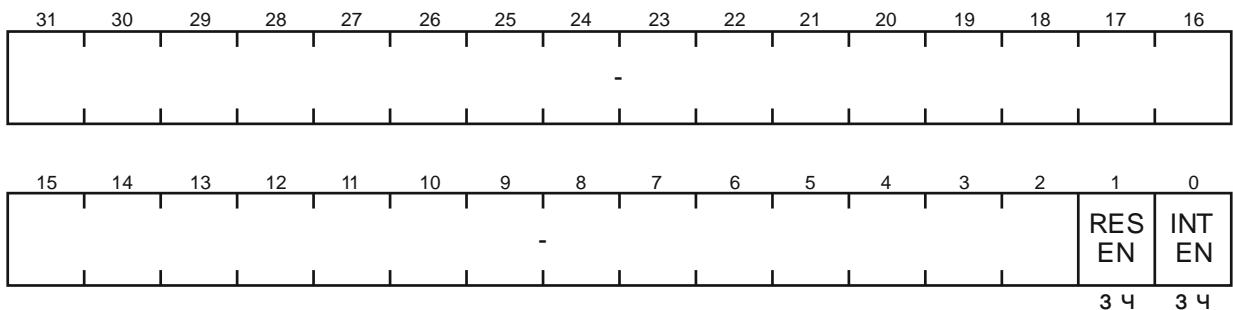

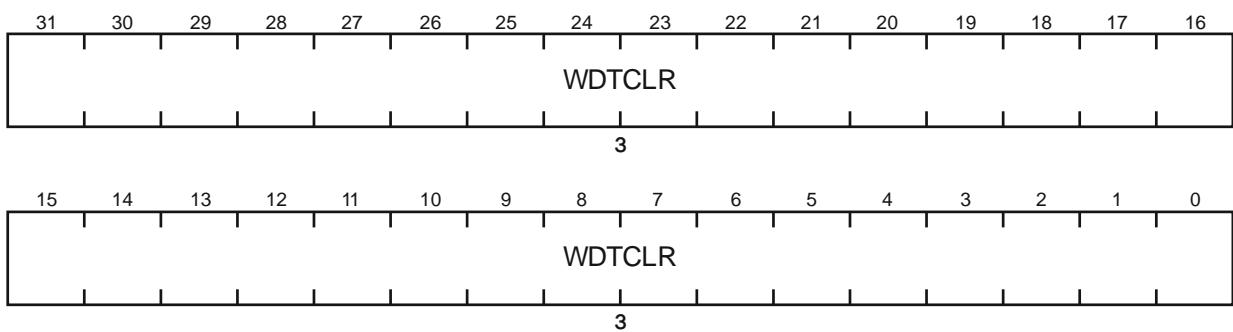

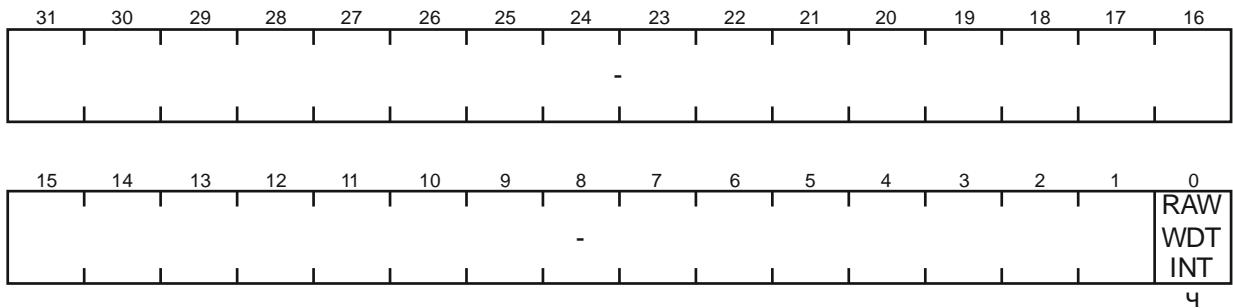

| 20 Сторожевой таймер .....                                 | 191 |

| 21 Программно-аппаратные средства отладки .....            | 192 |

| Заключение.....                                            | 193 |

| Приложение А (обязательное) Регистры микроконтроллера..... | 194 |

| A.1 Регистры контроллера АЦП.....                          | 194 |

| A.2 Регистры портов (GPIO).....                            | 211 |

| A.3 Регистры контроллера CAN .....                         | 238 |

| A.4 Регистры контроллера Flash-памяти .....                | 265 |

| A.5 Регистры блока управления системой .....               | 271 |

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

| A.6 Регистры системы управления тактированием и сбросом.....                | 277 |

| A.7 Регистры системы управления питанием .....                              | 292 |

| A.8 Регистры сторожевого таймера .....                                      | 294 |

| A.9 Регистры контроллера DMA .....                                          | 298 |

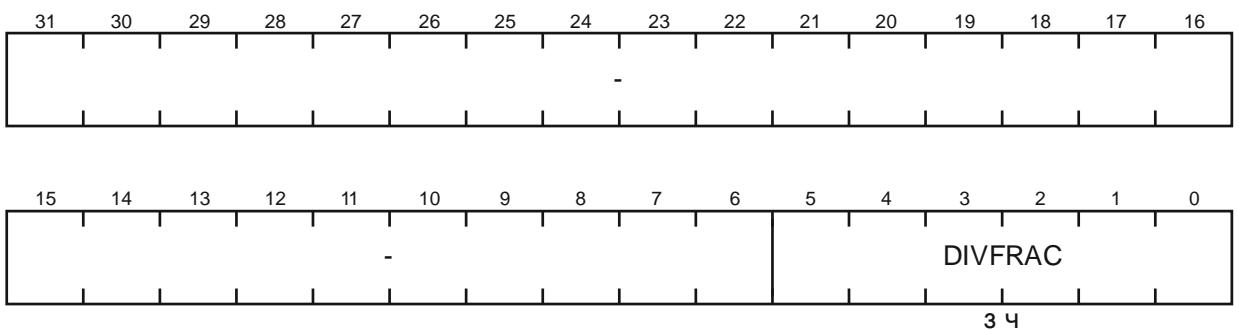

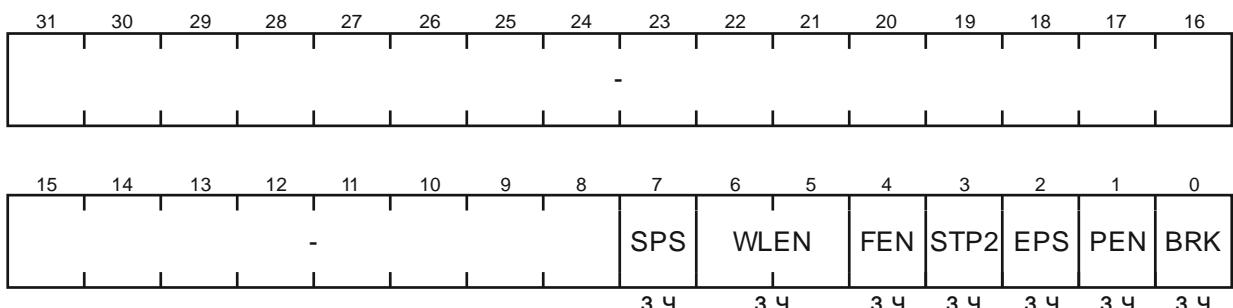

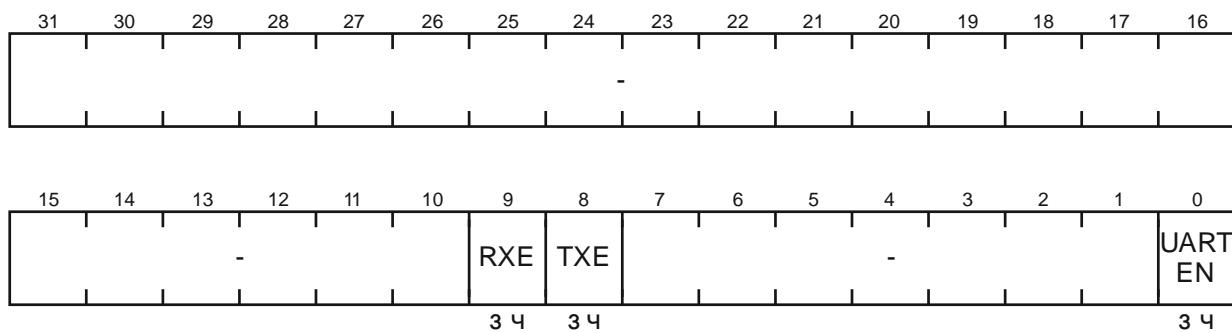

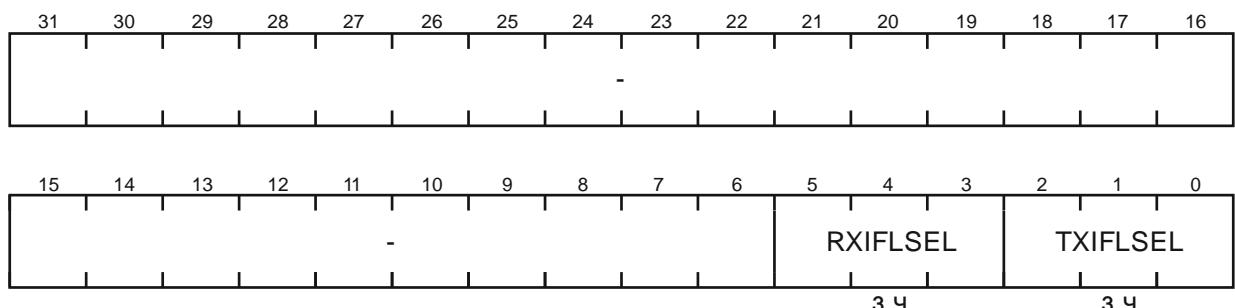

| A.10 Регистры блока UART .....                                              | 311 |

| A.11 Регистры контроллера SPI .....                                         | 320 |

| A.12 Регистры таймеров.....                                                 | 326 |

| A.13 Регистры блока ШИМ .....                                               | 330 |

| A.14 Регистры квадратурного декодера QEP .....                              | 357 |

| A.15 Регистры контроллера I2C .....                                         | 376 |

| A.16 Регистры блока захвата .....                                           | 388 |

| Приложение Б (обязательное) Коды состояний функционирования блока I2C ..... | 400 |

| Приложение В (обязательное) Регистры прерываний .....                       | 408 |

| Лист регистрации изменений .....                                            | 410 |

## **Введение**

32-разрядные микроконтроллеры с каждым днем набирают все большую популярность среди разработчиков различного оборудования и программистов. Они применяются при разработке и изготовлении электронной техники. Высокая вычислительная мощность и при этом относительно низкая стоимость делают эти устройства привлекательными для самого широкого круга разработчиков.

Микросхема К1946ВК035 представляет собой СБИС 32-разрядного микроконтроллера на базе RISC-ядра, предназначенного для промышленных и потребительских приложений, включая системы дистанционного мониторинга, контрольно-измерительные приборы, сетевые устройства, системы автоматизации производственных процессов, автомобильную электронику, системы управления электродвигателями.

В состав микроконтроллера входит широкий набор цифровой и аналоговой периферии, в связи с чем, он может применяться в различных системах цифровой обработки сигналов, в том числе требующих точных аналого-цифровых преобразований, в системах управления и сбора информации.

В настоящем руководстве пользователя приведено описание архитектуры, функционального построения и периферии микроконтроллера К1946ВК035.

## **1 Область применения и особенности ИС К1946ВК035**

Сфера применения интегральной микросхемы К1946ВК035 довольно широка: средства измерений, связи, наблюдения, безопасности, автоматизация производства, медицины, энергетики, промышленности, различных систем управления и системы электропривода.

Для эффективного управления в электромеханических системах была разработана дополнительная периферия: блоки ШИМ, блок АЦП с интерфейсом к контроллеру прямого доступа к памяти, модуль захвата/сравнения, блок импульсного квадратурного декодера, используемого для обработки сигналов датчиков положения ротора в высокопроизводительных системах для определения положения, направления и скорости вращения.

Разработанный микроконтроллер имеет встроенную Flash-память программ размером 64 Кбайт, которую можно использовать для хранения и загрузки пользовательского программного обеспечения. Во Flash-памяти существует особая защищенная область, которая может быть использована для хранения начального загрузчика.

Система тактирования микроконтроллера позволяет использовать различные источники тактового сигнала, что позволяет расширить набор применений и решаемых задач пользователя. Микроконтроллер может тактироваться от внутреннего RC-генератора с частотой 8 МГц, внутреннего осциллятора с внешним кварцевым резонатором, а также сигналом синтезатора частоты PLL. Существует возможность гибкой настройки тактовых сигналов для блоков периферии.

Для снижения энергопотребления микросхемы предусмотрена возможность отключения тактовых сигналов отдельных блоков периферии в случае, если они не используются пользователем. При переходе процессора в режим пониженного энергопотребления возможно отключение тактового сигнала ядра (команда WFI или WFE).

## 2 Краткое техническое описание микроконтроллера

### 2.1 Функциональные параметры

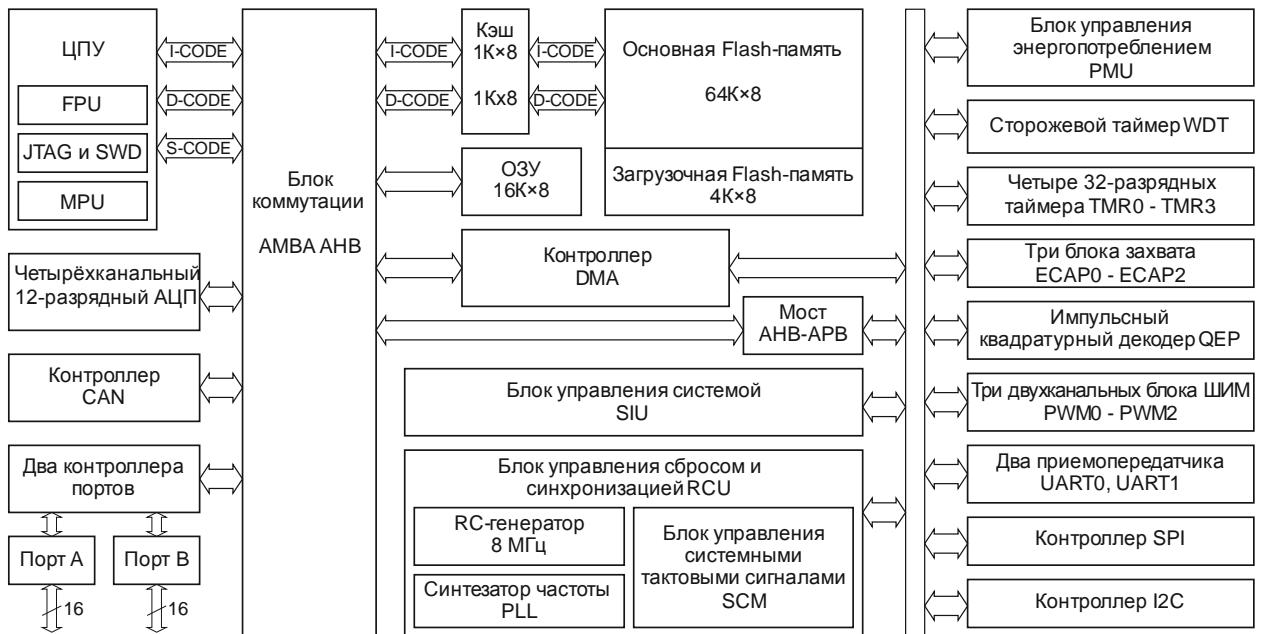

Структурная схема микроконтроллера показана на рисунке 2.1.

Рисунок 2.1 – Структурная схема микроконтроллера

В состав микроконтроллера входят функциональные элементы:

- 32-разрядное ЦПУ с поддержкой набора одноцикловых команд умножения с накоплением, команд централизованного управления потоком данных, арифметических и логических команд, встроенным модулем обработки команд с плавающей запятой с одинарной точностью FPU, поддержкой отладочных интерфейсов JTAG и SWD и модулем защиты памяти MPU;

- блок управления сбросом и синхронизацией RCU, имеющий в своем составе RC-генератор (8 Гц), синтезатор частоты PLL и блок управления системными тактовыми сигналами SCM;

- блок управления системой SIU;

- блок коммутации AMBA AHB;

- основная Flash-память объемом 64 Кбайт;

- загрузочная Flash-память емкостью 4 Кбайт;

- кэш команд и данных объемом 1 Кбайт каждый;

- ОЗУ объемом 16 Кбайт;

- 16-канальный контроллер прямого доступа к памяти DMA;

- блок управления энергопотреблением PMU, позволяющий переводить системные блоки в режим Powerdown;

- два контроллера портов А и В, управляющих 16-разрядными портами ввода-вывода;

- четырехканальный 12-разрядный АЦП с режимами цифрового компаратора для каждого из каналов (равно или больше, равно или меньше, попадание в диапазон, выход из диапазона) и функцией автоматического запуска модулей ШИМ по событию «окончание преобразования»;

- три двухканальных блока ШИМ PWM0 – PWM2;

- импульсный квадратурный декодер QEP для обработки сигналов датчиков положения ротора, позволяющий определить положение, направление и скорость вращения;

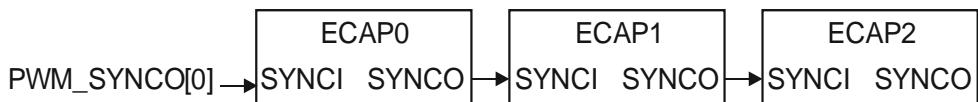

- три блока захвата ECAP0 – ECAP2;

- четыре 32-разрядных таймера TMR0 – TMR3;

- сторожевой таймер WDT;

- два приемопередатчика UART0, UART1;

- контроллер CAN (протокол 2.0b);

- контроллер I2C;

- контроллер SPI.

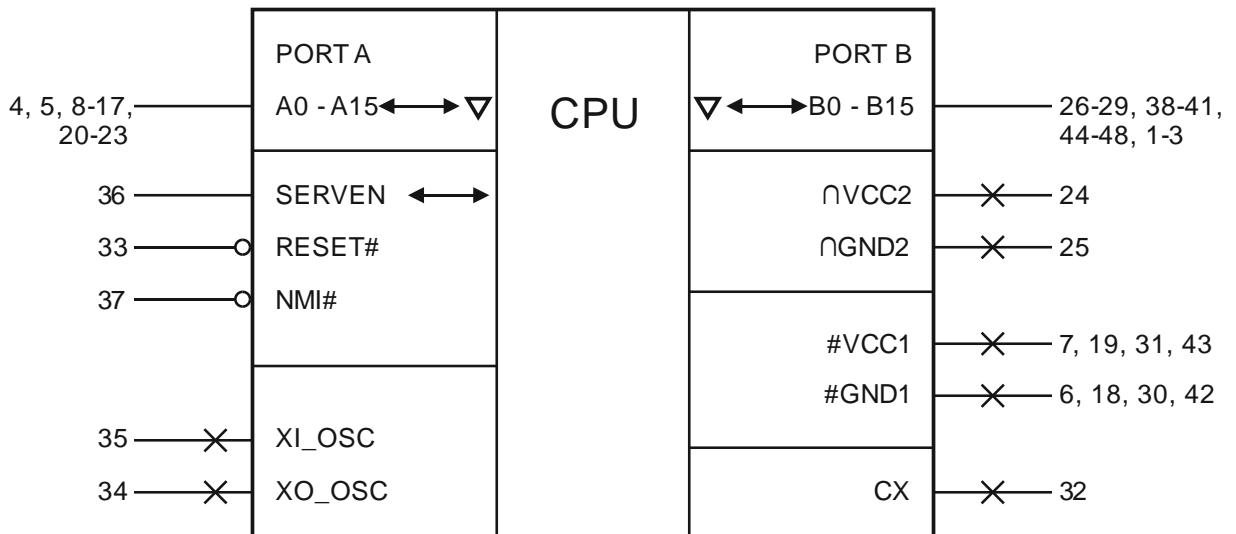

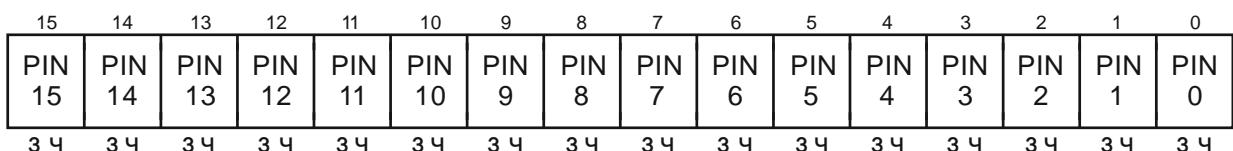

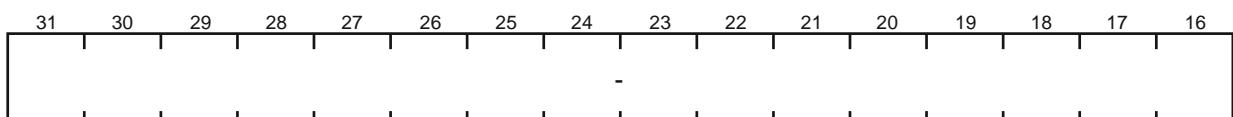

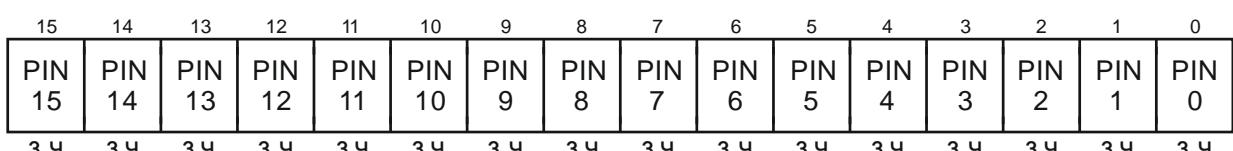

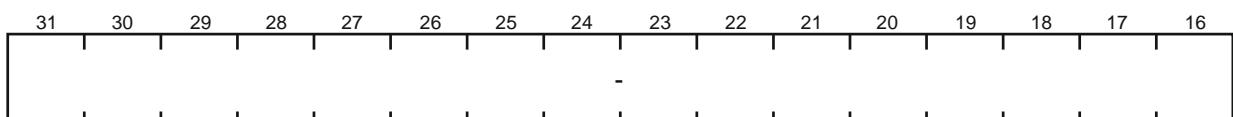

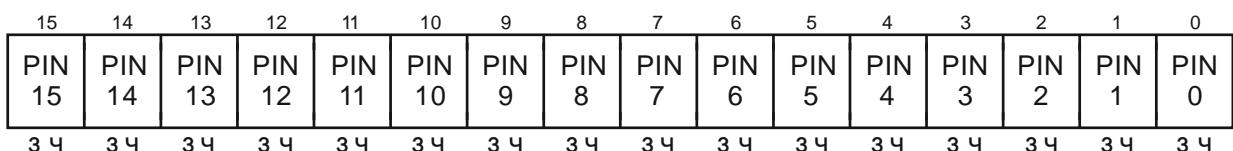

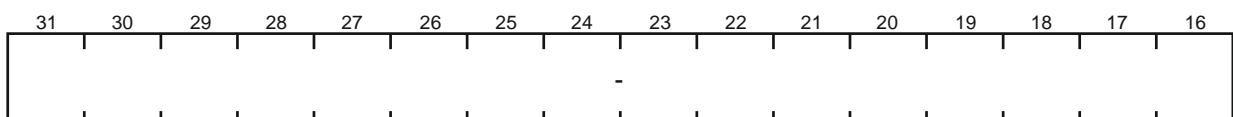

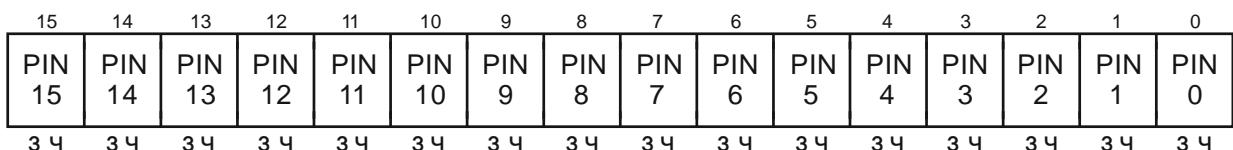

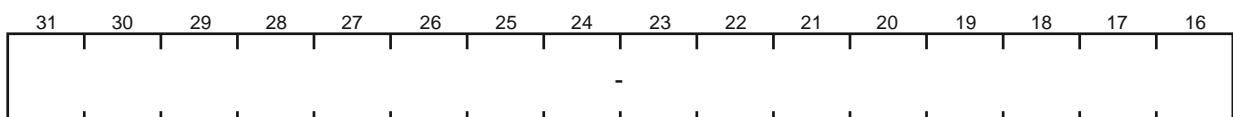

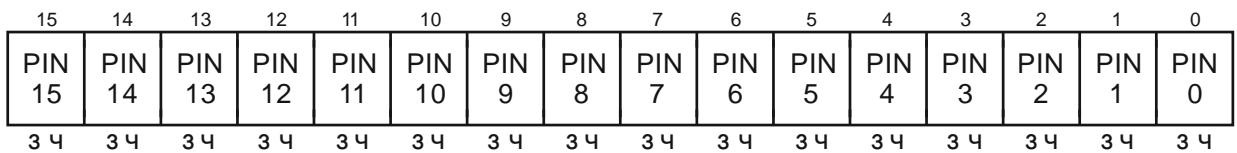

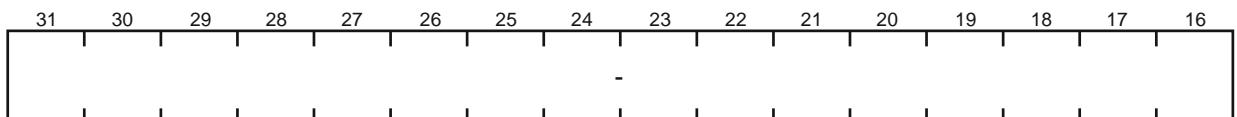

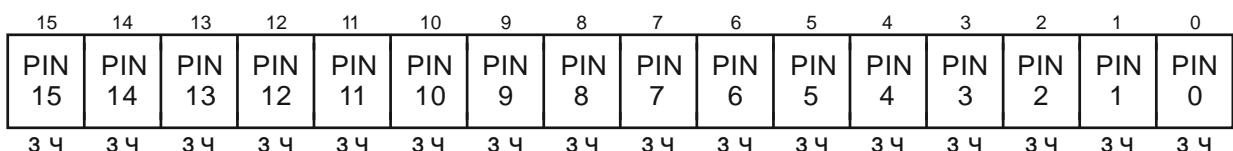

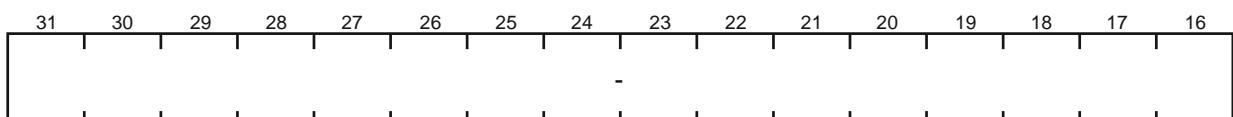

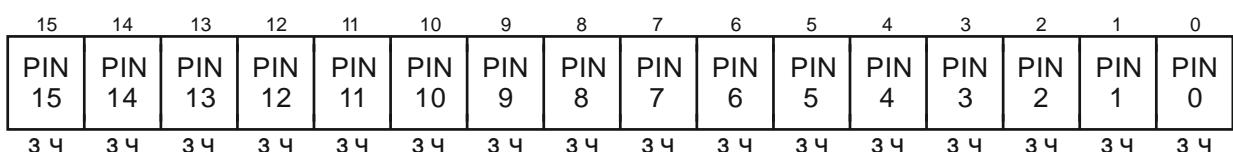

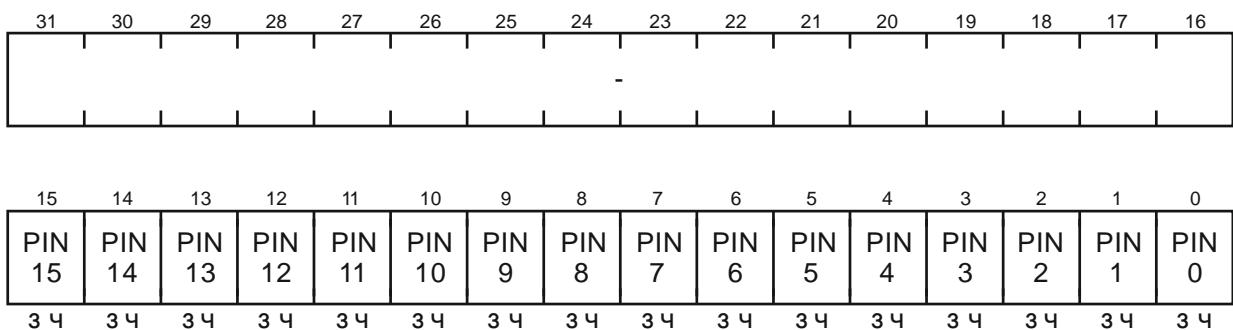

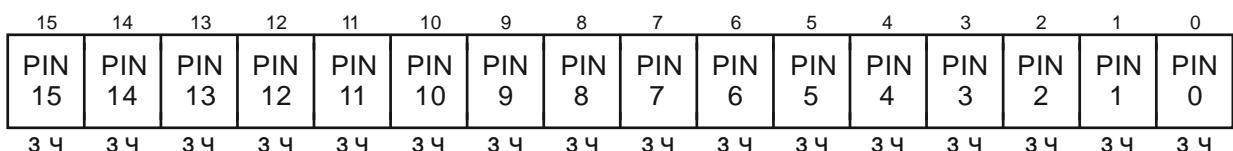

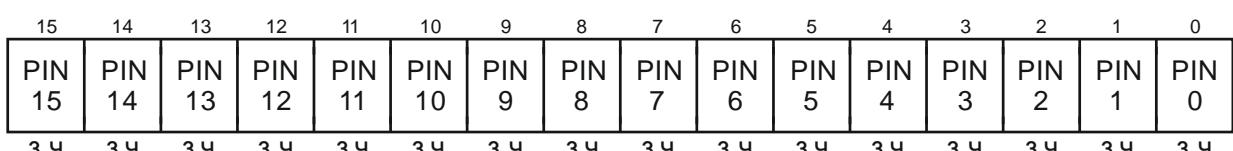

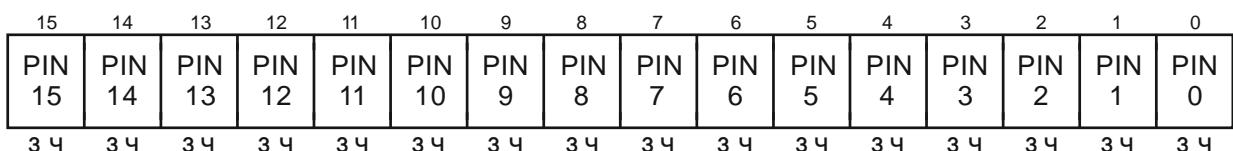

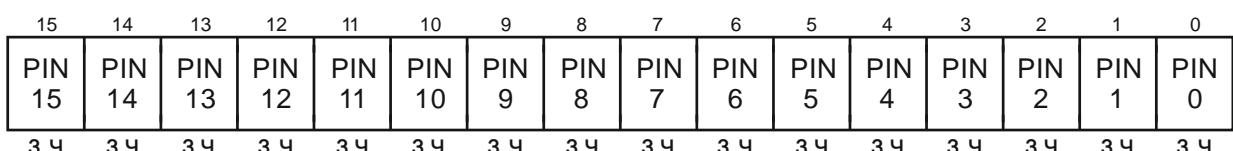

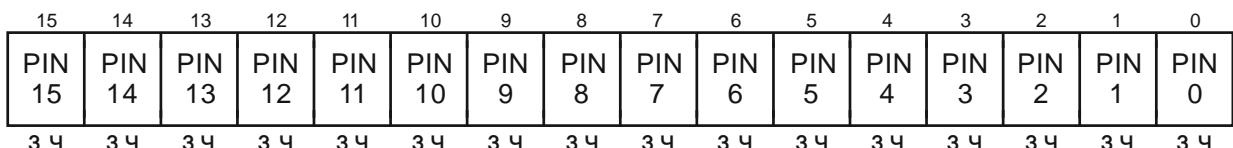

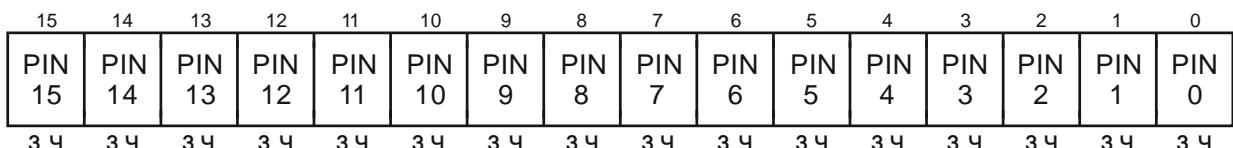

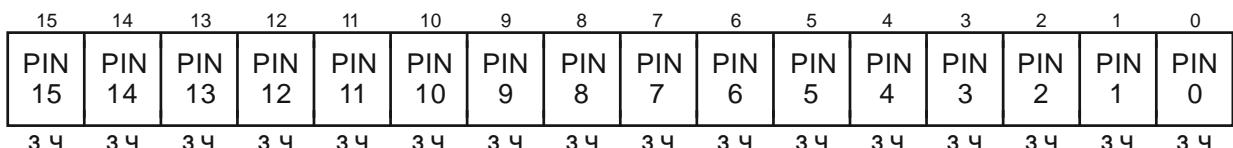

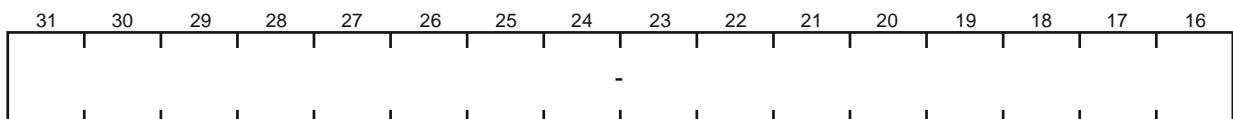

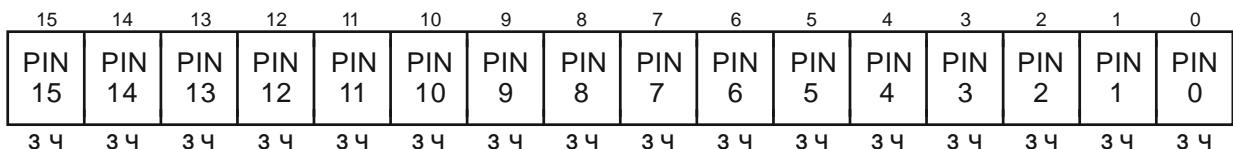

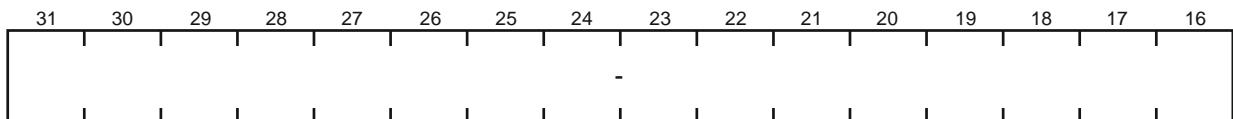

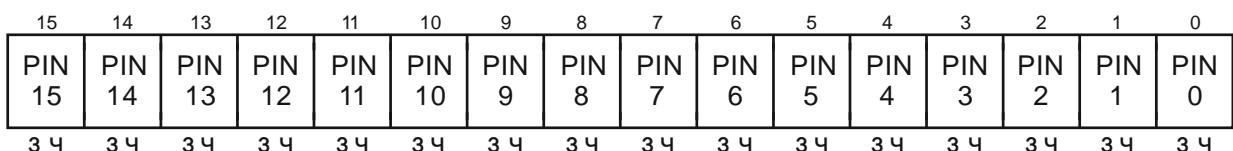

Условное графическое обозначение микроконтроллера приведено на рисунке 2.2.

Примечание – Альтернативные функции выводов порта А и порта В указаны в таблице 2.1.

Рисунок 2.2 – Условное графическое обозначение микросхемы

### Назначение выводов

Функциональное назначение выводов микроконтроллера приведено в таблице 2.1. После сброса микроконтроллера выводы портов А и В конфигурируются как выводы общего назначения и находятся в третьем состоянии. Исключение составляют выводы A2 – A6: конфигурируются как выводы отладочного интерфейса JTAG. Включение/отключение режима альтернативной функции осуществляется посредством регистров ALTFUNCSET/ALTFUNCCR блоков GPIO. Выводы портов А и В имеют схемы «pull-up» и «pull-down», подключаемые программно (регистр PULLMODE блока GPIO). Выводы NMI#, RESET# имеют постоянную схему «pull-up», вывод SERVEN – постоянную схему «pull-down». При использовании отладочного интерфейса SWD его вывод SWCLK соответствует выводу JTAG\_TCK, вывод SWDIO соответствует выводу JTAG\_TMS, а вывод блока трассировки SWO соответствует выводу JTAG\_TDO.

В таблице 2.1 используются условные обозначения: I – вход, O – выход, I/O – вход/выход, Z – третье состояние.

Микросхемы выполнены в металлополимерном корпусе LQFP48.

Масса микросхемы – не более 1,0 г.

Таблица 2.1 – Функциональное назначение выводов ИС К1946ВК035

| Обозна-<br>чение<br>вывода | Обозначение<br>альтернативно-<br>й функции<br>вывода | Номер<br>вывода | Тип<br>вывода | Функциональное назначение вывода     |

|----------------------------|------------------------------------------------------|-----------------|---------------|--------------------------------------|

| A0                         |                                                      | 4               | I/O/Z         | Вход/выход порта А, разряд 0         |

|                            | I2C_SCL                                              |                 | I/O           | Вход/выход синхросигнала I2C         |

| A1                         |                                                      | 5               | I/O/Z         | Вход/выход порта А, разряд 1         |

|                            | I2C_SDA                                              |                 | I/O           | Вход/выход данных I2C                |

| A2                         |                                                      | 8               | I/O/Z         | Вход/выход порта А, разряд 2         |

|                            | JTAG_TCK                                             |                 | I             | Вход тактового сигнала порта JTAG    |

| A3                         |                                                      | 9               | I/O/Z         | Вход/выход порта А, разряд 3         |

|                            | JTAG_TMS                                             |                 | I             | Вход режима порта JTAG               |

| A4                         |                                                      | 10              | I/O/Z         | Вход/выход порта А, разряд 4         |

|                            | JTAG_TDI                                             |                 | I             | Вход данных порта JTAG               |

|                            | ECAP0_IO                                             |                 | I/O           | Вход/выход блока захвата 0           |

| A5                         |                                                      | 11              | I/O/Z         | Вход/выход порта А, разряд 5         |

|                            | JTAG_TDO                                             |                 | O             | Выход данных порта JTAG              |

|                            | ECAP1_IO                                             |                 | I/O           | Вход/выход блока захвата 1           |

| A6                         |                                                      | 12              | I/O/Z         | Вход/выход порта А, разряд 6         |

|                            | JTAG_TRST                                            |                 | I             | Вход сброса порта JTAG               |

|                            | ECAP2_IO                                             |                 | I/O           | Вход/выход блока захвата 2           |

| A7                         |                                                      | 13              | I/O/Z         | Вход/выход порта А, разряд 7         |

|                            | PWM_TZ                                               |                 | I             | Вход сигнала аварии блоков ШИМ       |

| A8                         |                                                      | 14              | I/O/Z         | Вход/выход порта А, разряд 8         |

|                            | PWM0_A                                               |                 | O             | Выход линии А блока ШИМ0             |

| A9                         |                                                      | 15              | I/O/Z         | Вход/выход порта А, разряд 9         |

|                            | PWM0_B                                               |                 | O             | Выход линии В блока ШИМ0             |

| A10                        |                                                      | 16              | I/O/Z         | Вход/выход порта А, разряд 10        |

|                            | PWM1_A                                               |                 | O             | Выход линии А блока ШИМ1             |

| A11                        |                                                      | 17              | I/O/Z         | Вход/выход порта А, разряд 11        |

|                            | PWM1_B                                               |                 | O             | Выход линии В блока ШИМ1             |

| A12                        |                                                      | 20              | I/O/Z         | Вход/выход порта А, разряд 12        |

|                            | PWM2_A                                               |                 | O             | Выход линии А блока ШИМ2             |

| A13                        |                                                      | 21              | I/O/Z         | Вход/выход порта А, разряд 13        |

|                            | PWM2_B                                               |                 | O             | Выход линии В блока ШИМ2             |

| A14                        |                                                      | 22              | I/O/Z         | Вход/выход порта А, разряд 14        |

|                            | TMR0_IN                                              |                 | I             | Вход внешней синхронизации таймера 0 |

| A15                        |                                                      | 23              | I/O/Z         | Вход/выход порта А, разряд 15        |

|                            | TMR1_IN                                              |                 | I             | Вход внешней синхронизации таймера 1 |

| B0                         |                                                      | 26              | I/O/Z         | Вход/выход порта В, разряд 0         |

|                            | ADC_CH0                                              |                 | I             | Вход АЦП, разряд 0                   |

| B1                         |                                                      | 27              | I/O/Z         | Вход/выход порта В, разряд 1         |

|                            | ADC_CH1                                              |                 | I             | Вход АЦП, разряд 1                   |

| B2                         |                                                      | 28              | I/O/Z         | Вход/выход порта В, разряд 2         |

|                            | ADC_CH2                                              |                 | I             | Вход АЦП, разряд 2                   |

Окончание таблицы 2.1

| Обозна-<br>чение<br>вывода | Обозначение<br>альтернативной<br>функции<br>вывода | Номер<br>вывода  | Тип<br>вывода | Функциональное назначение вывода                                                  |

|----------------------------|----------------------------------------------------|------------------|---------------|-----------------------------------------------------------------------------------|

| B3                         | ADC_CH3                                            | 29               | I/O/Z         | Вход/выход порта B, разряд 3                                                      |

|                            |                                                    |                  | I             | Вход АЦП, разряд 3                                                                |

| B4                         | SPI_FSS                                            | 38               | I/O/Z         | Вход/выход порта B, разряд 4                                                      |

|                            |                                                    |                  | I/O           | Вход/выход выбора ведомого устройства SPI                                         |

| B5                         | SPI_SCK                                            | 39               | I/O/Z         | Вход/выход порта B, разряд 5                                                      |

|                            |                                                    |                  | I/O           | Вход/выход синхросигнала SPI                                                      |

| B6                         | SPI_RX                                             | 40               | I/O/Z         | Вход/выход порта B, разряд 6                                                      |

|                            |                                                    |                  | I             | Вход данных SPI                                                                   |

| B7                         | SPI_TX                                             | 41               | I/O/Z         | Вход/выход порта B, разряд 7                                                      |

|                            |                                                    |                  | O             | Выход данных SPI                                                                  |

| B8                         | UART1_TX                                           | 44               | I/O/Z         | Вход/выход порта B, разряд 8                                                      |

|                            |                                                    |                  | O             | Выход данных блока UART1                                                          |

| B9                         | UART1_RX                                           | 45               | I/O/Z         | Вход/выход порта B, разряд 9                                                      |

|                            |                                                    |                  | I             | Вход данных блока UART1                                                           |

| B10                        | UART0_TX                                           | 46               | I/O/Z         | Вход/выход порта B, разряд 10                                                     |

|                            |                                                    |                  | O             | Выход данных блока UART0                                                          |

|                            |                                                    |                  | I/O           | Вход/выход стробирования квадратурного декодера                                   |

| B11                        | UART0_RX                                           | 47               | I/O/Z         | Вход/выход порта B, разряд 11                                                     |

|                            |                                                    |                  | I             | Вход данных блока UART0                                                           |

|                            |                                                    |                  | I/O           | Индексный вход/выход квадратурного декодера                                       |

| B12                        | CAN1_RX                                            | 48               | I/O/Z         | Вход/выход порта B, разряд 12                                                     |

|                            |                                                    |                  | I             | Вход данных CAN1                                                                  |

|                            |                                                    |                  | I             | Вход B квадратурного декодера                                                     |

| B13                        | CAN1_TX                                            | 1                | I/O/Z         | Вход/выход порта B, разряд 13                                                     |

|                            |                                                    |                  | O             | Выход данных CAN1                                                                 |

|                            |                                                    |                  | I             | Вход A квадратурного декодера                                                     |

| B14                        | CAN0_RX                                            | 2                | I/O/Z         | Вход/выход порта B, разряд 14                                                     |

|                            |                                                    |                  | I             | Вход данных CAN0                                                                  |

| B15                        | CAN0_TX                                            | 3                | I/O/Z         | Вход/выход порта B, разряд 15                                                     |

|                            |                                                    |                  | O             | Выход данных CAN0                                                                 |

| CX                         | —                                                  | 32               | —             | Вывод регулятора напряжения питания для подключения внешнего конденсатора 4,7 мкФ |

| SERVEN                     | —                                                  | 36               | I/<br>O       | Вход выбора сервисного режима/<br>Выход программируемого тактового сигнала CLKOUT |

| NMI#                       | —                                                  | 37               | I             | Вход внешнего немаскируемого прерывания (активный ноль)                           |

| RESET#                     | —                                                  | 33               | I             | Вход внешнего сброса (активный ноль)                                              |

| XI_OSC                     | —                                                  | 35               | —             | Вывод внешнего тактового сигнала/<br>Вывод для подключения кварцевого резонатора  |

| XO_OSC                     | —                                                  | 34               | —             | Вывод для подключения кварцевого резонатора                                       |

| ∩VCC2                      | —                                                  | 24               | —             | Аналоговое питание 3,3 В                                                          |

| ∩GND2                      | —                                                  | 25               | —             | Аналоговая земля                                                                  |

| #VCC1                      | —                                                  | 7, 19,<br>31, 43 | —             | Цифровое питание 3,3 В                                                            |

|       |   |                  |   |                |

|-------|---|------------------|---|----------------|

| #GND1 | – | 6, 18,<br>30, 42 | – | Цифровая земля |

|-------|---|------------------|---|----------------|

### Особенности системы питания

На плате вывод питания  $\cap VCC2$  может быть объединен с выводами питания #VCC1 (при этом должны быть приняты меры для снижения помех по питанию).

Выключение питания микроконтроллера должно проводиться путем полного снятия напряжения, как с выводов питания, так и со всех остальных выводов микросхемы. Подача напряжения на функциональные выводы микросхемы при выключенном питании недопустима.

## 2.2 Электрические параметры

Номинальное значение напряжения питания по выводам #VCC1,  $\cap VCC2$  должно быть  $3,3 \text{ В} \pm 0,3\text{В}$ .

Значение суммарного максимального тока по выводам портов А и В не должно превышать 50 мА.

Допустимая максимальная разность значений напряжений питания по выводам #VCC1,  $\cap VCC2$  составляет 50 мВ.

Амплитудное значение пульсации напряжения питания должно быть не более 50 мВ.

Электрические параметры микросхем при приемке и поставке соответствуют нормам, приведенным в таблице 2.2.

Таблица 2.2 – Электрические параметры микросхем при приемке и поставке

| Наименование параметра,<br>единица измерения, режим измерения                                                                                                  | Буквенное<br>обозначение<br>параметра | Норма<br>параметра |             | Темпера-<br>тура<br>среды,<br>°C         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|-------------|------------------------------------------|

|                                                                                                                                                                |                                       | не менее           | не<br>более |                                          |

| 1                                                                                                                                                              | 2                                     | 3                  | 4           | 5                                        |

| 1 Выходное напряжение низкого уровня по выводам A0 – A15, B0 – B15, B,<br>$U_{CC1} = 3,0 \text{ В}$ , $I_{OL} = 6 \text{ мА}$                                  | $U_{OL}$                              | –                  | 0,4         | $-45 \pm 3$<br>$25 \pm 10$<br>$85 \pm 3$ |

| 2 Выходное напряжение высокого уровня по выводам A0 – A15, B0 – B15, B,<br>$U_{CC1} = 3,0 \text{ В}$ , $I_{OH} = -6 \text{ мА}$                                | $U_{OH}$                              | 2,1                | –           |                                          |

| 3 Ток утечки низкого уровня по входам A0 – A15, B0 – B15 с отключенными «pull-up» и «pull-down»,<br>мкА,<br>$U_{CC1} = 3,6 \text{ В}$ , $U_{IL} = 0 \text{ В}$ | $I_{ILL}$                             | –10                | –           |                                          |

| 4 Ток утечки высокого уровня по входам A0 – A15<br>B0 – B15 с отключенными «pull-up» и «pull-down»,<br>мкА,<br>$U_{CC1} = 3,6 \text{ В}$ , $U_{IH} = U_{CC1}$  | $I_{ILH}$                             | –                  | 10          |                                          |

| 5 Входной ток низкого уровня по выводам<br>«pull-up» A0 – A15, B0 – B15, NMI#, RESET#,<br>мкА,<br>$U_{CC1} = 3,6 \text{ В}$ , $U_{IL} = 0 \text{ В}$           | $I_{IL1}$                             | –200               | –           |                                          |

| 6 Входной ток высокого уровня по выводам<br>«pull-up» NMI#, RESET#, мкА,<br>$U_{CC1} = 3,6 \text{ В}$ , $U_{IH} = U_{CC1}$                                     | $I_{IH1}$                             | –                  | 10          |                                          |

| 7 Входной ток низкого уровня по выводу<br>«pull-down» SERVEN, мкА,<br>$U_{CC1} = 3,6 \text{ В}$ , $U_{IL} = 0 \text{ В}$                                       | $I_{IL2}$                             | –10                | –           |                                          |

| 8 Входной ток высокого уровня по выводам<br>«pull-down» A0 – A15, B0 – B15, SERVEN, мкА,<br>$U_{CC1} = 3,6 \text{ В}$ , $U_{IH} = U_{CC1}$                     | $I_{IH2}$                             | –                  | 200         |                                          |

|                                                                                          |           |     |   |  |

|------------------------------------------------------------------------------------------|-----------|-----|---|--|

| 9 Входной ток низкого уровня по выводу XI_OSC, мкА,<br>$U_{CC1} = 3,6$ В, $U_{IL} = 0$ В | $I_{IL3}$ | -40 | - |  |

|------------------------------------------------------------------------------------------|-----------|-----|---|--|

Окончание таблицы 2.2

| 1                                                                                                                                                                | 2          | 3  | 4   | 5           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|-----|-------------|

| 10 Входной ток высокого уровня по выводу XI_OSC, мкА,<br>$U_{CC1} = 3,6$ В, $U_{IH} = U_{CC1}$                                                                   | $I_{IH3}$  | -  | 40  |             |

| 11 Динамический ток потребления по выводам #VCC1 в активном режиме, мА,<br>$U_{CC1} = 3,6$ В, $U_{CC2} = 3,6$ В, $f_{CI} = 100$ МГц                              | $I_{OCC1}$ | -  | 150 | $-45 \pm 3$ |

| 12 Интегральная нелинейность АЦП, ЕМР,<br>$U_{CC1} = 3,6$ В, $U_{CC2} = 3,6$ В                                                                                   | $E_L$      | -3 | 3   | $25 \pm 10$ |

| 13 Дифференциальная нелинейность АЦП, ЕМР,<br>$U_{CC1} = 3,6$ В, $U_{CC2} = 3,6$ В                                                                               | $E_{LD}$   | -2 | 2   | $85 \pm 5$  |

| 14 Функциональный контроль,<br>$U_{CC1} = (3,0; 3,6)$ В, $U_{CC2} = (3,0; 3,6)$ В,<br>$f_{CI} = (1; 100)$ МГц                                                    | ФК         | -  | -   |             |

| Примечания                                                                                                                                                       |            |    |     |             |

| 1 Параметры $I_{ILL}$ , $I_{ILH}$ , $I_{IH1}$ , $I_{IL2}$ при температуре минус 45 °С не измеряются, а гарантируются нормами при температуре ( $25 \pm 10$ ) °С. |            |    |     |             |

| 2 При функциональном контроле АЦП значения напряжений питания изменяются синхронно.                                                                              |            |    |     |             |

Значения предельно допустимых электрических режимов эксплуатации в диапазоне рабочих температур среды соответствуют нормам, приведенным в таблице 2.3.

Таблица 2.3 – Значения предельно допустимых электрических режимов эксплуатации микросхем в диапазоне температур среды

| Наименование параметра режима, единица измерения                         | Буквенное обозначение параметра           | Предельно допустимый режим |           | Предельный режим |                 |

|--------------------------------------------------------------------------|-------------------------------------------|----------------------------|-----------|------------------|-----------------|

|                                                                          |                                           | не менее                   | не более  | не менее         | не более        |

| 1 Напряжение питания цифровой части, В <sup>1)</sup>                     | $U_{CC1}$                                 | 3,0                        | 3,6       | -0,3             | 5,2             |

| 2 Напряжение питания аналоговой части, В <sup>1)</sup>                   | $U_{CC2}$                                 | 3,0                        | 3,6       | -0,3             | 5,2             |

| 3 Входное напряжение низкого уровня, В <sup>1)</sup>                     | $U_{IL}$                                  | -0,5                       | 0,8       | -0,6             | -               |

| 4 Входное напряжение высокого уровня, В <sup>1)</sup>                    | $U_{IH}$                                  | 2,1                        | $U_{CC1}$ | -                | $U_{CC1} + 0,6$ |

| 5 Входное напряжение высокого уровня по выводу XI_OSC, В <sup>1)</sup>   | $U_{IHC}$                                 | 2,1                        | $U_{CC1}$ | -                | $U_{CC1} + 0,6$ |

| 6 Выходной ток низкого уровня, мА <sup>1)</sup>                          | $I_{OL}$                                  | -                          | 6         | -                | 10              |

| 7 Выходной ток высокого уровня, мА <sup>1)</sup>                         | $I_{OH}$                                  | -6                         | -         | -10              | -               |

| 8 Частота следования импульсов тактового сигнала процессорного ядра, МГц | $f_{CI}$                                  | 1                          | 100       | -                | -               |

| 9 Частота следования импульсов тактового сигнала по выводу XI_OSC, МГц   | при работе с внешним тактовым генератором | $f_C$                      | 1         | 40               | -               |

|                                                                          | при работе с кристаллическим резонатором  |                            | 8         | 24               | -               |

| 10 Емкость нагрузки, пФ                                                  | $C_L$                                     | -                          | 40        | -                | -               |

| Наименование параметра режима, единица измерения                                   | Буквенное обозначение параметра | Предельно допустимый режим |          | Предельный режим |          |

|------------------------------------------------------------------------------------|---------------------------------|----------------------------|----------|------------------|----------|

|                                                                                    |                                 | не менее                   | не более | не менее         | не более |

| <sup>1)</sup> Время работы в одном из предельных режимов должно быть не более 5 с. |                                 |                            |          |                  |          |

### 3 Архитектура изделия

Микроконтроллер K1946BK035 структурно представляет собой мультистадийный RISC процессор. Ядро полностью реализует наборы команд Thumb и Thumb2.

Поддержка DSP-инструкций и наличие модуля операций с плавающей запятой существенно ускоряет обработку потоковых данных, что в свою очередь делает микроконтроллер весьма привлекательным для использования в системах управления и обработки информации.

Микроконтроллер способен параллельно выполнять четыре операции сложения/вычитания с 8-разрядными operandами или две операции сложения/вычитания с 16-разрядными operandами. Также реализовано умножение за один цикл, при этом для 16-разрядных чисел возможно параллельное выполнение двух операций. Из особенностей следует отметить аппаратное умножение 32-разрядных чисел за 1 цикл, а также деление 32-разрядных чисел, занимающее от 2 до 12 циклов.

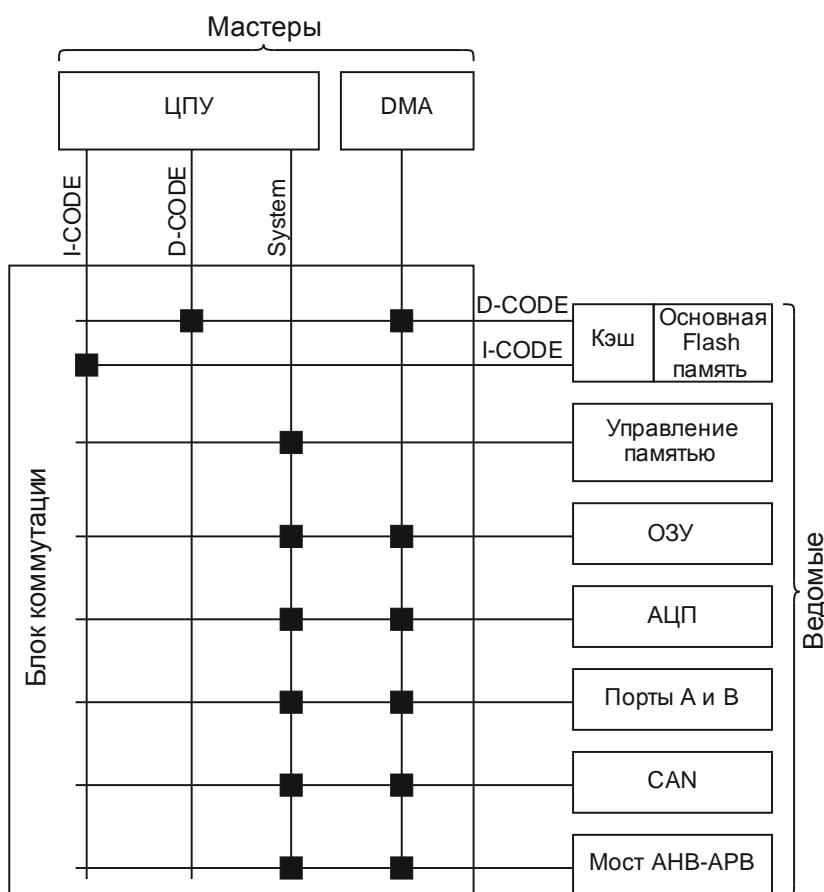

#### Блок коммутации микроконтроллера

Все устройства микроконтроллера соединены между собой через блок коммутации. На рисунке 3.1 приведена схема соединения основных и периферийных блоков микроконтроллера внутри блока коммутации.

Рисунок 3.1 – Схема соединения блоков внутри блока коммутации

## 4 Блок управления сбросом и синхронизацией RCU

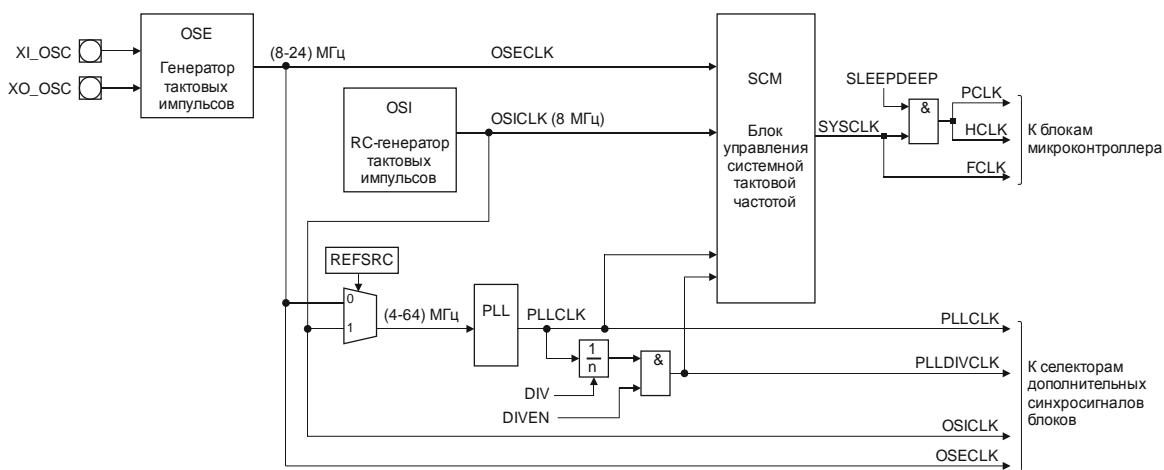

### 4.1 Общая система тактирования

В микроконтроллере предусмотрена развитая подсистема управления тактовыми сигналами и сигналами сброса, см. рисунок 4.1.

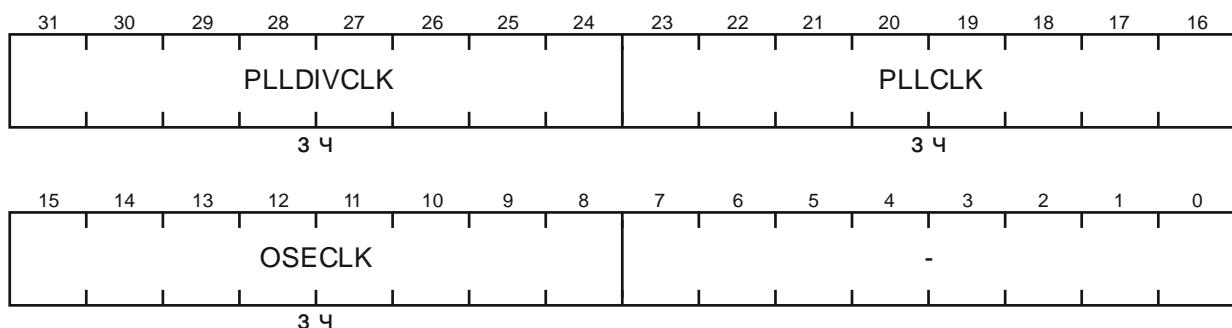

Основными тактовыми сигналами, которые используются в микросхеме, являются:

- OSICLK – тактовый сигнал внутреннего RC-генератора;

- OSECLK – внешний тактовый сигнал по выводам XI\_OSC и XO\_OSC;

- PLLCLK – тактовый сигнал с выхода PLL;

- PLLDIVCLK – тактовый сигнал с выхода PLL, прошедший через дополнительный делитель;

- SYSCLK – системный тактовый сигнал, определяющий частоту работы процессорного ядра ( $f_{SYSCLK} = f_{CI}$ );

- PCLK – периферийный тактовый сигнал АРВ шины;

- HCLK – системный тактовый сигнал АНВ шины;

- FCLK – неотключаемый системный тактовый сигнал.

Рисунок 4.1 – Схема синхронизации

### 4.2 Синтезатор частоты PLL

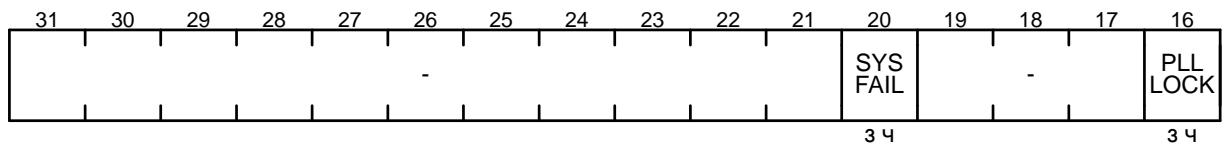

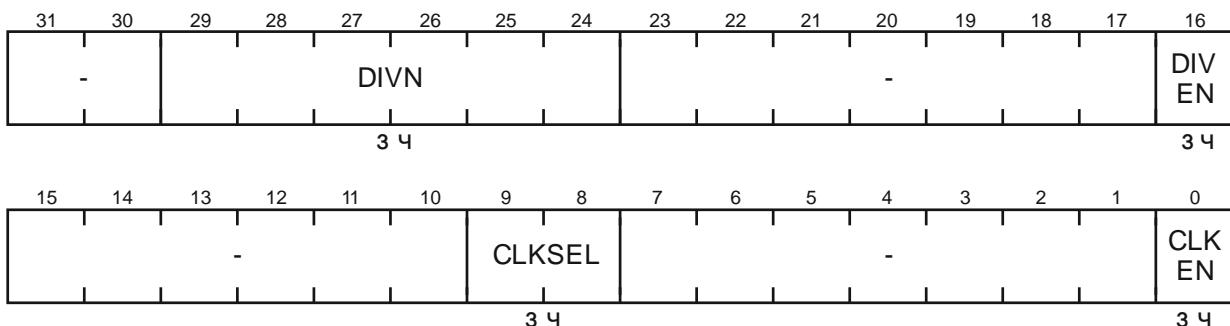

В качестве опорного сигнала блока PLL можно выбрать один из источников, выбор осуществляется полем REFSRC регистра PLLCFG.

Выходная частота блока PLL определяется согласно формуле

$$f_{OUT} = f_{IN} \times \frac{M}{N} \times \frac{1}{2^{OD}} \quad (4.1)$$

Коэффициенты N, M, OD задаются соответствующими полями регистра PLLCFG. Существуют следующие ограничения параметров:

- коэффициент деления  $1 \leq N \leq 63$ ;

- коэффициент деления  $2 \leq M \leq 63$ ;

- входная частота должна находиться в диапазоне (4 – 64) МГц;

- значение частоты  $f_{IN}/N$  должно быть в диапазоне (4 – 20) МГц;

- значение частоты  $f_{IN} \times M/N$  должно быть в диапазоне (120 – 200) МГц;

- значение выходной частоты  $f_{OUT}$  должно быть в диапазоне (15 – 200) МГц.

Настройку блока PLL необходимо делать до того, как его тактовый сигнал будет выбран в качестве рабочей частоты системы или одного из блоков. При правильной установке всех значений и выходе блока PLL на рабочий режим, будет установлен бит LOCK в регистре PLLCFG. После установления рабочего режима можно разрешить выход частоты из блока PLL битом OUTEN. Также есть возможность прохождения сигнала сквозь блок PLL без изменений (bypass режим), для установления которого можно воспользоваться битом BYPASS.

Также присутствует внешний делитель частоты, управляемый битами регистра PLLDIV. Для тактирования различных блоков и модулей микроконтроллера можно выбрать как сигнал PLLCLK, так и PLLDIVCLK, независимо друг от друга.

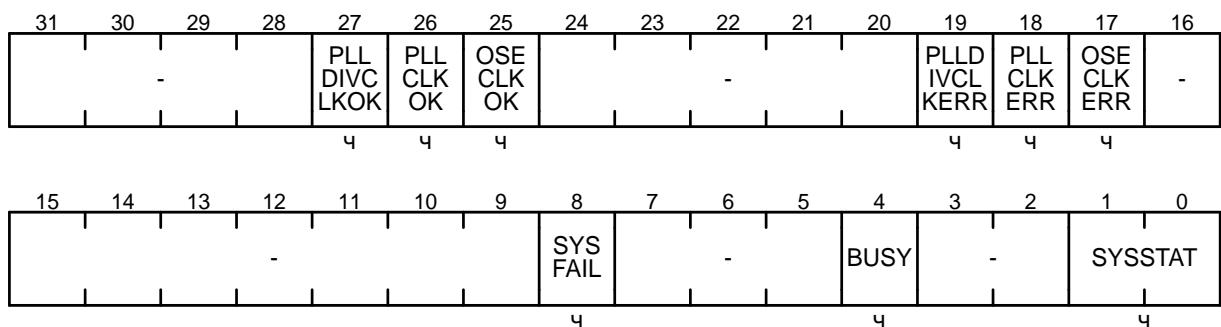

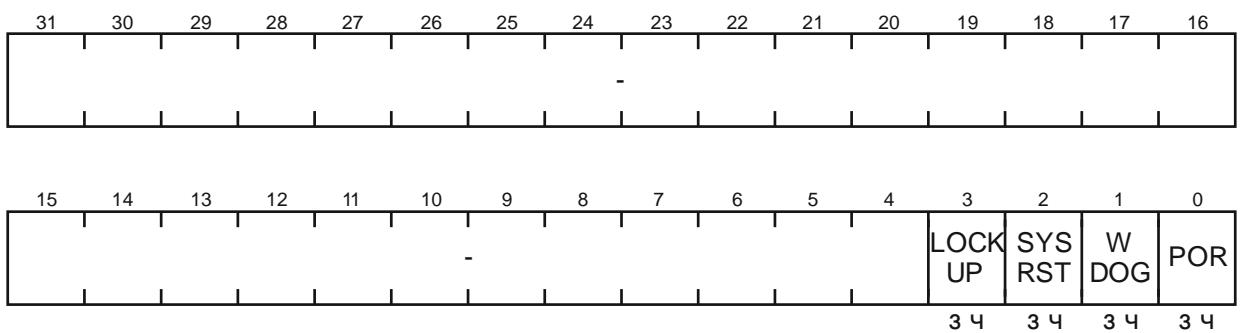

#### 4.3 Система слежения за тактовыми сигналами

Система слежения осуществляет контроль источников тактовых сигналов и позволяет обрабатывать исключительные ситуации, связанные с их пропаданием (срыв генерации блока PLL, ненадежный контакт с внешним резонатором и т. п.).

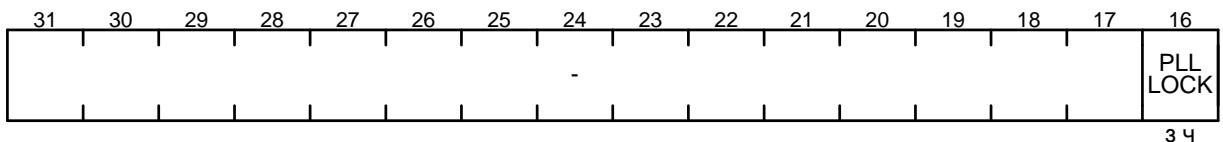

Текущий статус тактовых сигналов можно установить, прочитав соответствующие биты xOK и xERR регистра SYSCLKSTAT, где x – OSECLK, PLLCLK, PLLDIVCLK. Бит xOK будет установлен, если соответствующий тактовый сигнал стабильно работает и будет сброшен при его сбое. Бит xERR имеет обратное поведение – при сбое устанавливается, сбрасывается при нормальной работе тактового сигнала.

Время реакции системы слежения на исчезновение тактового сигнала настраивается с помощью полей регистра SECPRD и по умолчанию равно 256 тактам сигнала OSICLK. Реакция на любое пропадание тактового сигнала на меньшее время будет отсутствовать.

Минимальная частота, за которой может осуществляться слежение – 20 кГц.

Значение минимально возможного времени реакции вычисляется по формуле (4.2) (результат округляется до целого в большую сторону).

$$\text{SECPRD\_MIN} = (4 \times T_{\text{REF}} + 6 \times T_{\text{CLK}}) / T_{\text{REF}}, \quad (4.2)$$

где  $T_{\text{REF}}$  – период опорной тактовой частоты сигнала OSICLK;

$T_{\text{CLK}}$  – период контролируемой тактовой частоты.

Например, если необходима максимально быстрая реакция на пропадание частоты 100 МГц на выходе блока PLL ( $T_{\text{CLK}} = 10$  нс) при сигнале OSICLK 8 МГц ( $T_{\text{REF}} = 125$  нс), то необходимо в поле PLLCLK регистра SECPRD0 записать значение SECPRD\_MIN = 5, вычисленное по формуле (4.2).

Стоит отметить, что SECPRD\_MIN является лишь временем детектирования сбоя. Сам переход в аварийный режим (переключение системной частоты на сигнал OSICLK) займет дополнительно не более 14 тактов сигнала OSICLK.

Кроме слежения за каждым из источников тактового сигнала по отдельности, система отслеживания позволяет контролировать текущий системный тактовый сигнал SYSCLK.

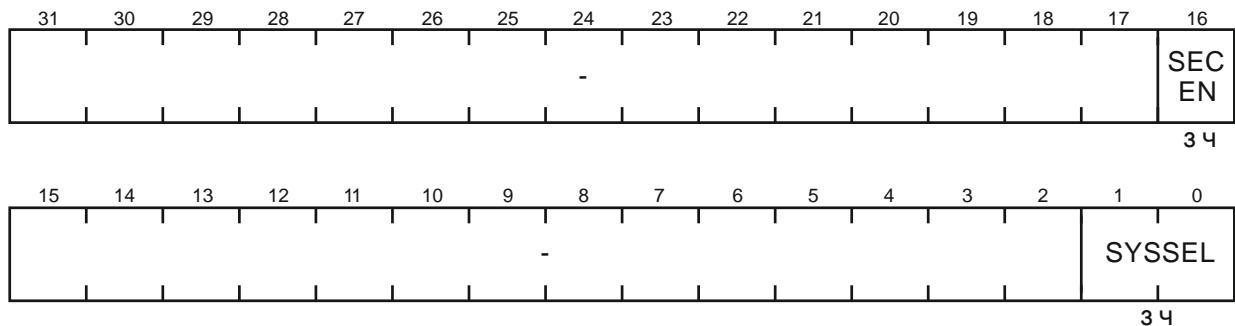

Включение контроля сигнала SYSCLK осуществляется установкой бита SECEN регистра SYSCLKCFG.

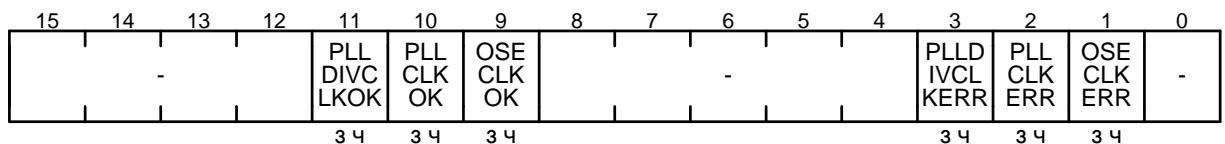

При сбое будет осуществлен аварийный переход системной частоты на сигнал OSICLK, и будет выработано немаскируемое прерывание NMI# совместно с установкой флага прерывания SYSFAIL в регистре INTSTAT (флаг сбрасывается записью единицы).

Текущий статус системного тактового сигнала доступен в бите SYSFAIL регистра SYSCLKSTAT: при сбое этот бит устанавливается и будет держаться установленным, пока пользователь вручную не перейдет на любой из доступных стабильных источников, записав в поле SYSSEL регистра SYSCLKCFG новое значение (при сбое поле сохраняет старое значение источника системной частоты). В том числе возможен переход и на сигнал OSICLK, несмотря на то, что в аварийном режиме схема уже тактируется этим сигналом – это позволит сбросить бит SYSFAIL регистра SYSCLKSTAT.

Прямой переход из аварийного состояния к тактированию от вызвавшего сбой, но уже восстановившегося источника – невозможен. Если это необходимо сделать, то сначала нужно перейти на один из стабильных источников (например, сигнал OSICLK), и лишь затем начать переход на бывший «сбойным», но восстановившийся источник.

При переходе микроконтроллера в аварийное состояние по тактированию требуется обязательно перейти на стабильный источник тактирования (бит xOK для него будет установлен), например, на сигнал OSICLK (SYSSEL = 0). Если аварийный источник возобновил тактирование, то снова перейти на него можно, записав поле SYSSEL регистра SYSCLKCFG на номер соответствующего источника.

## 4.4 Сигналы сброса

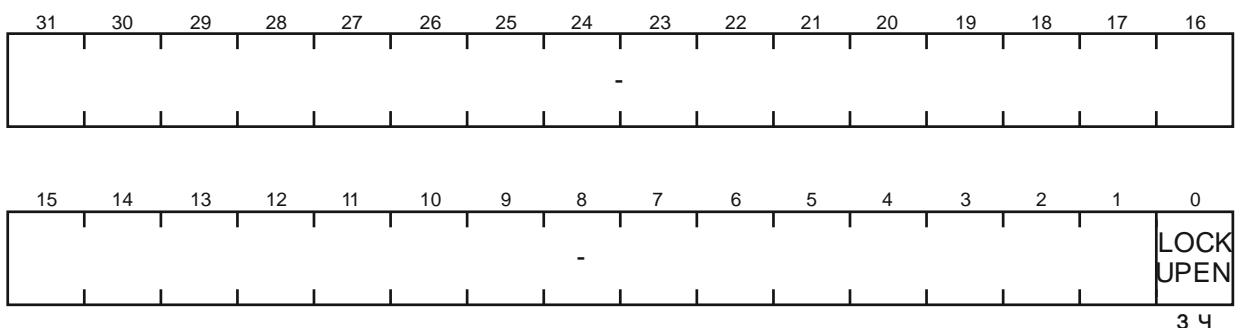

Сброс может осуществляться как внешним сигналом с вывода RESET# (активный уровень сигнала сброса – низкий), так и с помощью внутренних источников – по запросу процессора и по переполнению сторожевого таймера.

Также в микроконтроллере есть возможность сброса по получению сигнала LOCKUP от ядра. Данный сигнал возникает в случае невосстановимого системного исключения (Unrecoverable exception), если микроконтроллер не может из него выйти. Установка бита LOCKUPEN в регистре SYSRSTCFG разрешит автоматический сброс после получения от ядра сигнала LOCKUP.

В регистре SYSRSTSTAT содержится набор флагов, по которым можно установить причину последнего произошедшего сброса. В случае нормальной загрузки после подачи питания будет установлен флаг POR, так как сброс вызван внешним сигналом.

## 4.5 Прерывания

В микроконтроллере есть два прерывания, связанных с работой блока RCU.

Первое прерывание – непосредственно RCU Interrupt. Выбрать источники, влияющие на него можно в регистре INTEN – события появления или пропадания одного из тактовых сигналов, выход блока PLL в рабочий режим. Все события сопровождаются флагами в регистре INTSTAT.

Второе прерывание связано с пропаданием текущего системного тактового сигнала SYSCLK. В случае если была включена система слежения за тактовым сигналом (бит SECEN регистра SYSLKCFG) возникнет прерывание, соответствующее вектору немаскируемого прерывания NMI#, и будет установлен соответствующий флаг в регистре INTSTAT.

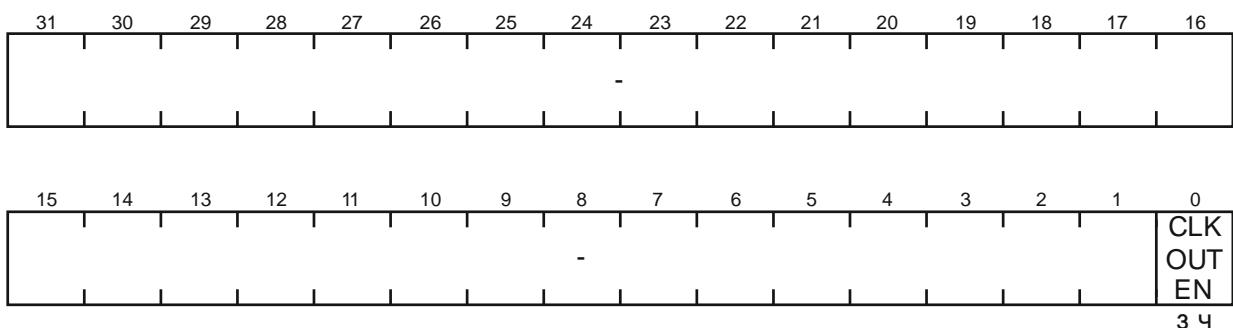

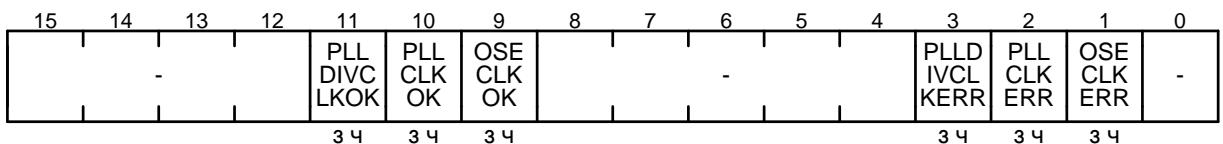

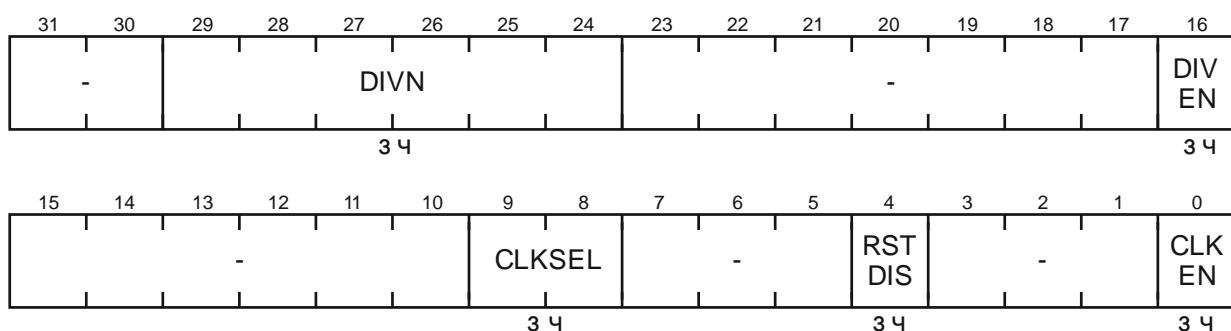

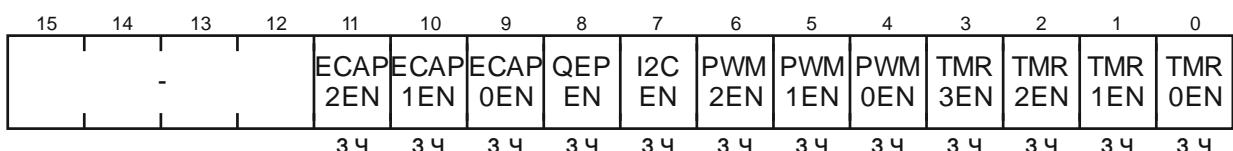

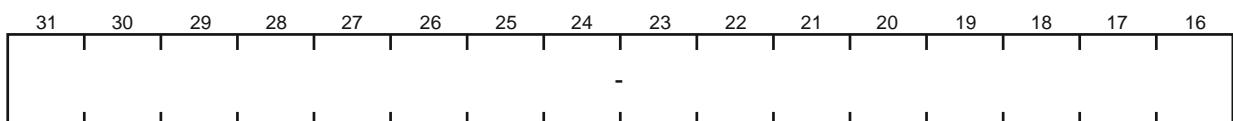

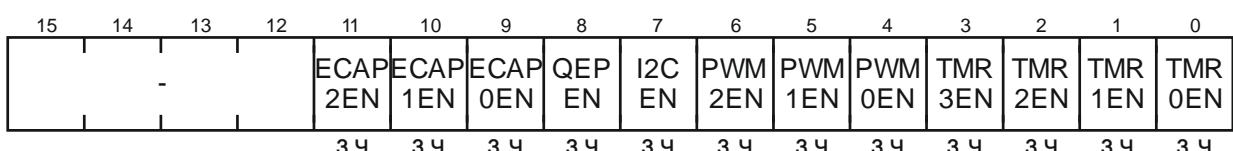

## 4.6 Тактирование и сброс периферийных блоков

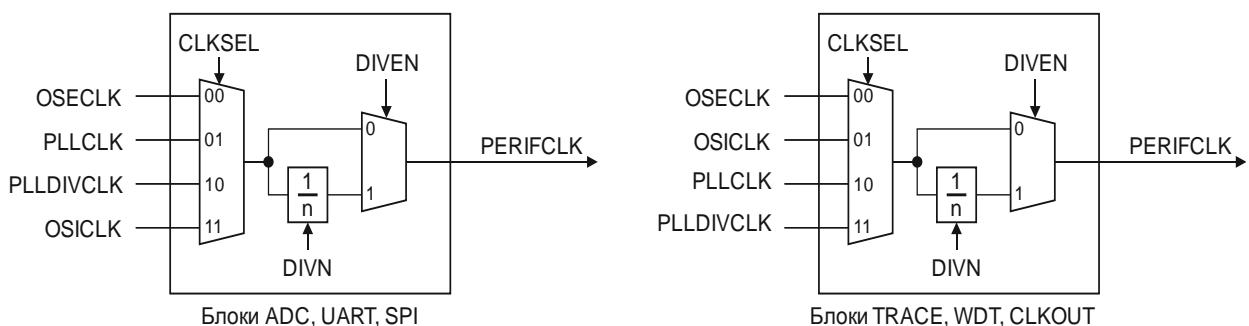

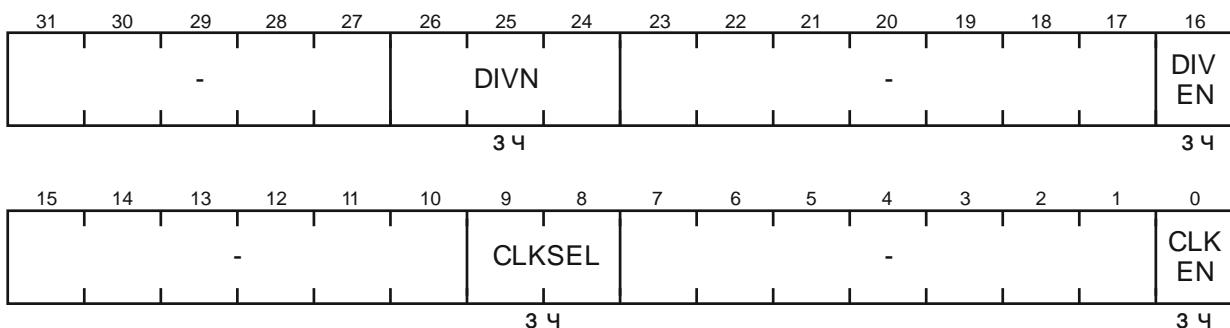

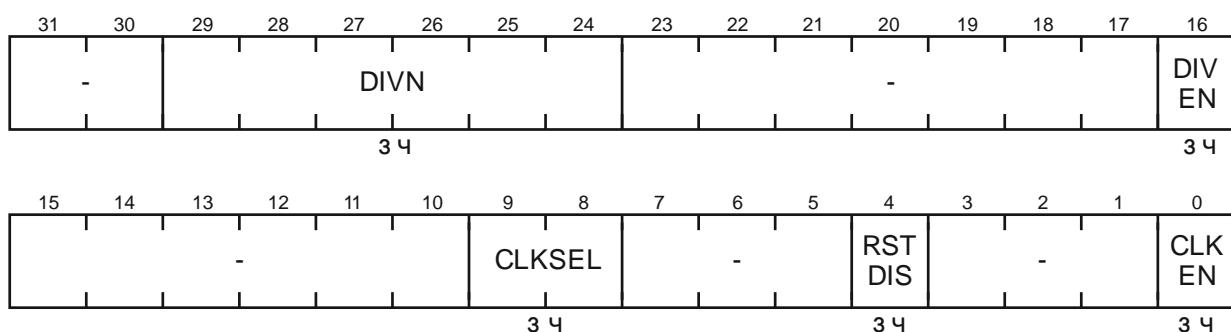

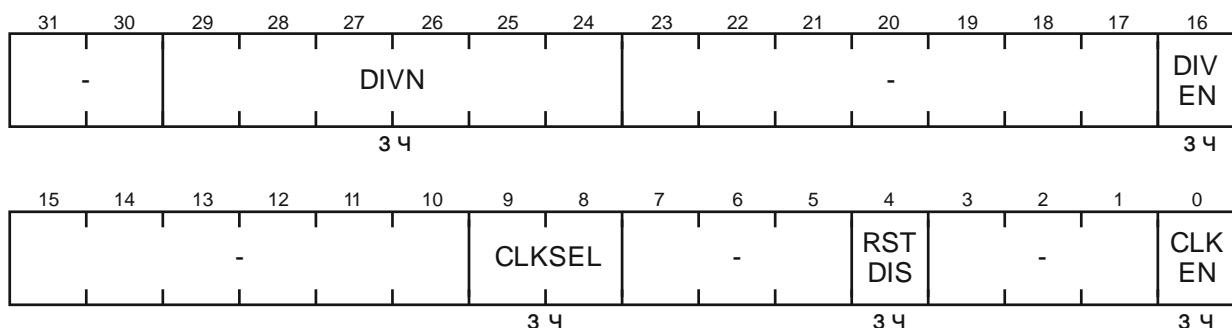

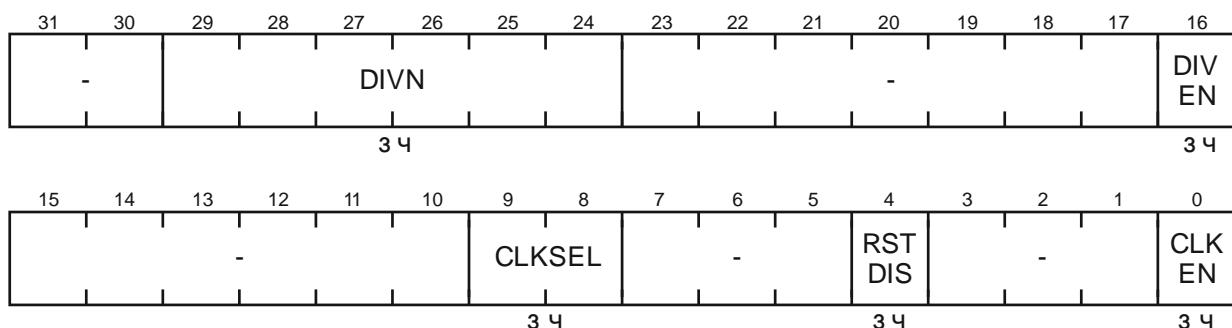

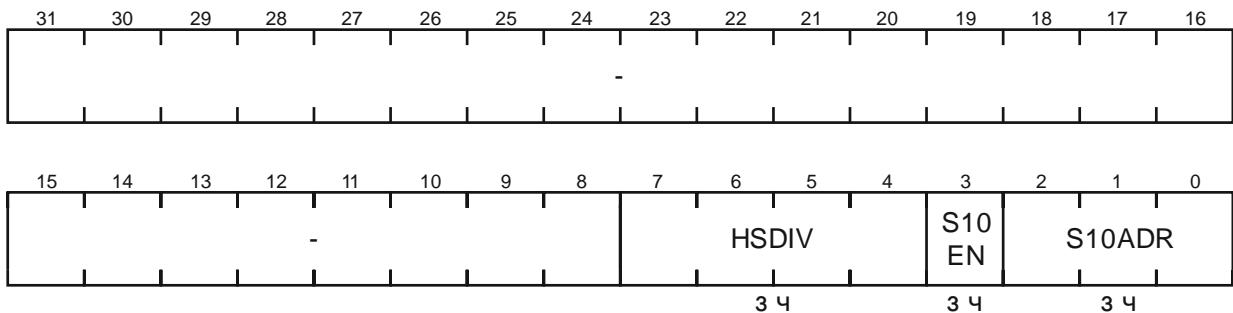

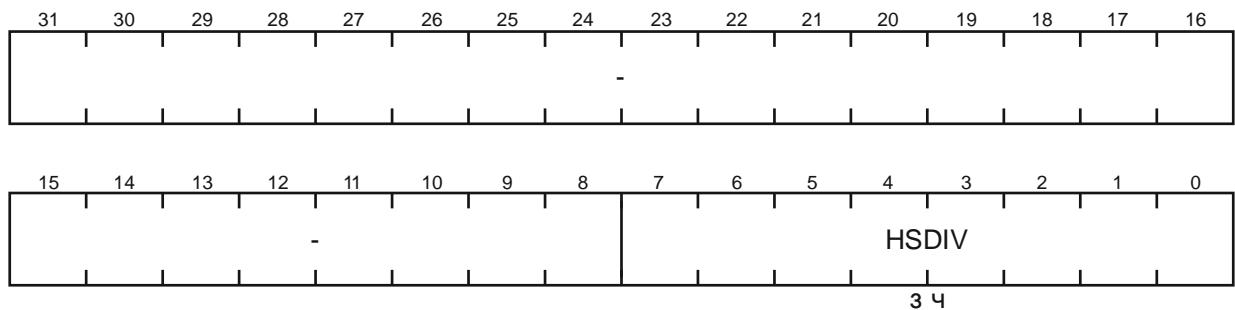

Для некоторых периферийных блоков система тактирования предусматривает выбор независимого тактового источника. У блоков WATCHDOG, TRACE, UART, SPI, ADC и блока формирования внешнего сигнала CLKOUT есть соответствующие регистры, в которых можно включать тактирование, выбирать его источник и настраивать отключаемый делитель. Источник тактирования выбирается независимо для каждого из блоков с помощью его собственного селектора, показанного на рисунке 4.2.

Рисунок 4.2 – Схемы селекторов дополнительных синхросигналов блоков

Для остальных блоков, а именно: CAP, TMR, I2C, QEP, PWM, и для блоков, относящихся к АНВ периферии (GPIO, CAN), тактирование подается установкой соответствующего бита в CLKCFG, см. таблицу 4.1.

Таблица 4.1 – Тактовые сигналы периферийных блоков

| Периферийный блок | Тактовый сигнал | Делитель | Управляющий регистр |

|-------------------|-----------------|----------|---------------------|

| ADC               | ACLK            | 1-63     | ADCCFG              |

| SPI               | SPICLK          | 1-63     | SPICFG              |

| UART              | UARTCLK         | 1-63     | UARTCFG             |

| WATCHDOG          | WDTCLK          | 1-63     | WDTCFG              |

| CLOCKOUT          | CLKOUT          | 1-7      | CLKOUTCFG           |

| TRACE             | TRACECLK        | 1-63     | TRACECFG            |

| TIMER             | PCLK            | -        | PCLKCFG, PRSTCFG    |

| PWM               | PCLK            | -        | PCLKCFG, PRSTCFG    |

| I2C               | PCLK            | -        | PCLKCFG, PRSTCFG    |

| QEP               | PCLK            | -        | PCLKCFG, PRSTCFG    |

| CAP               | PCLK            | -        | PCLKCFG, PRSTCFG    |

| GPIO              | HCLK            | -        | HCLKCFG, HRSTCFG    |

| CAN               | HCLK            | -        | HCLKCFG, HRSTCFG    |

По умолчанию на всех периферийных блоках отключено тактирование, и все они находятся в состоянии сброса. Для начала работы нужно подать тактовый сигнал, а также вывести блок из состояния сброса, осуществив запись единиц в соответствующие биты регистров управления.

## **5 Блок управления энергопотреблением PMU**

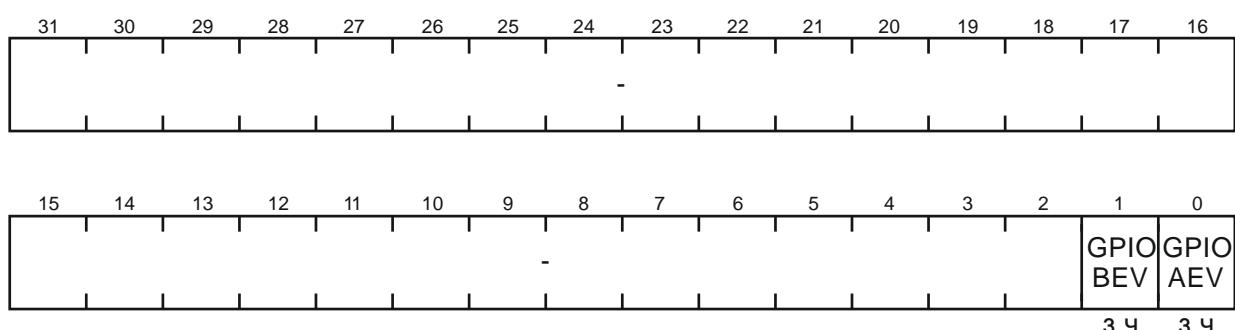

В микроконтроллере предусмотрены несколько режимов функционирования для уменьшения потребляемой энергии в тех задачах, где ядро не должно постоянно работать, например, во время ожидания прихода внешнего события. К ним относятся:

- режим Sleep (ядро остановлено, периферия работает);

- режим Deepsleep (ядро остановлено, периферия переведена в режим Powerdown).

Контроль режимов энергопотребления осуществляется с помощью блока управления энергопотреблением PMU.

### **5.1 Режим Sleep**

Вход в режим Sleep производится при выполнении инструкции WFI (Wait For Interrupt) или WFE (Wait For Event) при сброшенном бите SLEEPDEEP регистра SCR блока SCB ядра. В этом режиме прекращается тактирование ядра, но вся периферия продолжает полностью функционировать.

В зависимости от состояния бита SLEEPONEXIT (регистр SCR блока SCB ядра) возможны два режима входа в этот режим:

- SLEEPONEXIT = 0 – вход в режим Sleep производится, как только была выполнена инструкция WFI или WFE, при выходе продолжает исполняться программа, прерванная одной из инструкций выше;

- SLEEPONEXIT = 1 – вход в режим Sleep осуществляется не только при выполнении соответствующих инструкций, но и каждый раз при выходе из последнего активного обработчика прерываний (ядро «просыпается» только для обработки прерываний).

Выход из режима Sleep производится различными путями, в зависимости от того, какая инструкция была использована для входа.

Если для входа в режим Sleep была использована инструкция WFI, то приход любого разрешенного прерывания в NVIC вызовет выход из режима, одновременно с переходом в соответствующий обработчик.

Если была использована инструкция WFE, то выход произойдет либо по разрешенному прерыванию NVIC (аналогично WFI), либо по событию, которое может быть сгенерировано несколькими путями.

Если установлен бит SEVONPEND регистра SCR блока SCB ядра, то событием будет являться приход любого запрещенного прерывания в NVIC (разрешенного лишь в периферийном модуле, а не в NVIC). При этом по выходе необходимо будет сбрасывать соответствующие флаги прерывания, как в периферийном модуле, так и в регистрах NVIC (регистры ICPR).

Также событием для выхода из режима Sleep является сигнал RXEV, который может быть сгенерирован в GPIOA или GPIOB. Дополнительно сигнал RXEV от необходимого порта должен быть разрешен установкой бита GPIOAEV или GPIOBEV в регистре RXEVEN блока PMU. В этом случае выход из режима Sleep будет произведен наиболее быстро, так как время на вход/выход в прерывание тратиться не будет.

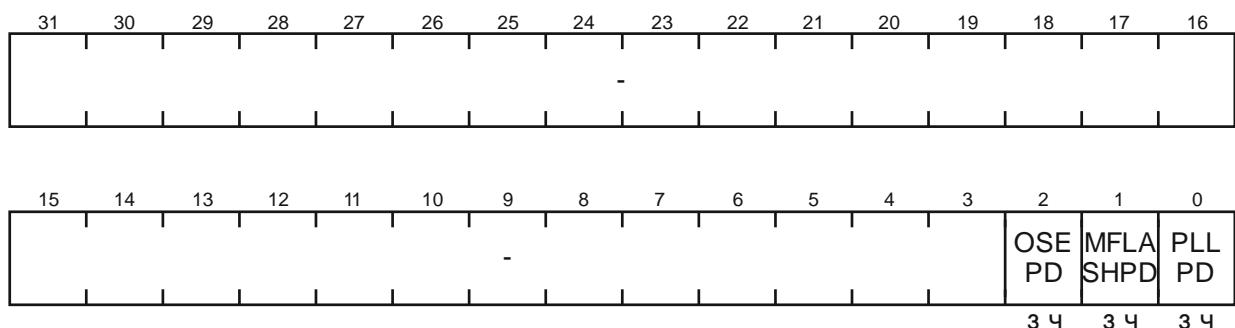

### **5.2 Режим Deepsleep**

В режиме Deepsleep тактирование ядра останавливается, а также происходит переход в режим Powerdown следующих периферийных блоков (по умолчанию): MFLASH, PLL, EXTOSC.

Вход в режим Deepsleep производится при выполнении инструкции WFI (Wait For Interrupt) или WFE (Wait For Event) при установленном бите SLEEPDEEP регистра SCR блока SCB ядра.

Если для входа в режим Deepsleep была использована инструкция WFI, то приход любого разрешенного прерывания в NVIC вызовет выход из режима, одновременно с переходом в соответствующий обработчик.

Если для входа в режим Deepsleep была использована инструкция WFE, то приход любого разрешенного события RXEV от портов ввода-вывода вызовет выход из режима.

Перед тем как осуществить вход в этот режим необходимо провести некоторые подготовительные операции.

Необходимо включить PMU, установив бит EN в регистре CFG блока PMU. В противном случае переход в режим Deepsleep будет невозможен.

С помощью сброса битов PLLPD, MFLASHPD, EXTOSCPD в регистре PDEN блока PMU можно отключить перевод соответствующих блоков в режим Powerdown при входе в режим Deepsleep – они продолжат свое функционирование. Например, если оставить активным внешний осциллятор, периферия, использующая его в качестве тактового сигнала, продолжит функционировать.

Необходимо настроить значение длительности выхода из режима Deepsleep – выход периферийных блоков из режима Powerdown требует некоторого времени (для каждого блока разное), поэтому в регистр PUDEL блока PMU должно быть внесено значение большее либо равное самой большой величине задержки среди блоков, для которых активен режим Powerdown. Значение вносится в тактах тактового сигнала OSICLK. В таблице 5.1 представлены типовые величины задержек. По умолчанию регистр PUDEL содержит значение 1680, т. к. возможность активации режима Powerdown включена для блока PLL.

Таблица 5.1 – Настройка времени выхода из режима Powerdown для указанных блоков

| Периферийный блок | Время выхода из режима Powerdown, мкс | Значение регистра PUDEL в тактах сигнала OSICLK ( $f_{OSICLK} = 8 \text{ МГц}$ ) |

|-------------------|---------------------------------------|----------------------------------------------------------------------------------|

| PLL               | 210                                   | 1680                                                                             |

| MFLASH            | 15                                    | 120                                                                              |

| EXTOSC            | 0                                     | 0                                                                                |

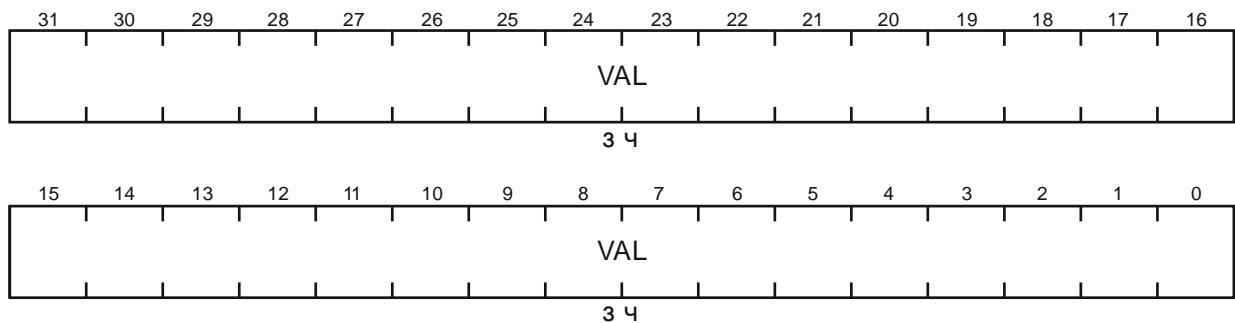

## 6 Организация памяти

Память микроконтроллера имеет предопределенное 32-разрядное адресное пространство с областями: программ, данных, периферии и внутренних ресурсов, жестко соединенных с процессором. Адресное пространство разбито на четыре основные области, см. таблицу 6.1.

Таблица 6.1 – Общая организация памяти микроконтроллера

| Адресное пространство   | Описание                                                              |

|-------------------------|-----------------------------------------------------------------------|

| E000_0000h – FFFF_FFFFh | Системная область                                                     |

| 4000_0000h – 400F_FFFFh | Регистры управления периферийными блоками                             |

| 2000_0000h – 2000_3FFFh | Внутреннее ОЗУ 16 Кбайт                                               |

| 0000_0000h – 0000_FFFFh | Flash-память<br>(шина выборки инструкций I-Code + шина данных D-Code) |

Системная область делится на две части. Первая часть, объемом 1 Мбайт, занимает диапазон адресов E000\_0000h – E007\_FFFFh и зарезервирована для «личной» периферийной шины PPB (Private Peripheral Bus). Шина PPB используется для выборки/записи данных и отладочного доступа – для периферии. Эта область рассматривается как строго упорядоченная память. Часть ее адресов (E000\_E000h – E000\_EFFFh) занимает пространство управления системы SCS, в котором находятся регистры блока управления системой SCB, контроллера прерываний NVIC, системного таймера SysTick, средств отладки и другие. Байты регистров SCS всегда располагаются в порядке «младший – старший» независимо от того, какой формат представления данных принят для остальной памяти. Доступ к большинству регистров возможен только полными двойными словами (32 бита), все исключения из этого правила оговариваются специально. Попытка кода обратиться к области PPB обычно вызывает прерывание по ошибке шины; исключениями являются возможность доступа к регистру STIR, если это разрешено соответствующим битом регистра CCR, и доступность отладочных регистров. Вторая часть является памятью устройств, занимает область E010\_0000h – FFFF\_FFFFh и является системным регионом ядра.

Регистры периферийных блоков микроконтроллера доступны в адресном пространстве 4000\_0000h – 4000\_FFFFh. Карта размещения блоков микроконтроллера в памяти представлена в таблице 6.2.

Таблица 6.2 – Регистры периферийных блоков

| Адресное пространство   | Название блока | Описание                       |

|-------------------------|----------------|--------------------------------|

| 4005_3000h – 4005_3FFFh | ECAP2          | Блок захвата 2                 |

| 4005_2000h – 4005_2FFFh | ECAP1          | Блок захвата 1                 |

| 4005_1000h – 4005_1FFFh | ECAP0          | Блок захвата 0                 |

| 4005_0000h – 4005_0FFFh | I2C            | Последовательный интерфейс I2C |

| 4004_F000h – 4004_FFFFh | QEP            | Квадратурный декодер QEP       |

| 4004_E000h – 4004_EFFFh | PWM2           | Блок ШИМ2                      |

| 4004_D000h – 4004_DFFFh | PWM1           | Блок ШИМ1                      |

| 4004_C000h – 4004_CFFFh | PWM0           | Блок ШИМ0                      |

| 4004_B000h – 4004_BFFFh | TMR3           | Блок таймера 3                 |

| 4004_A000h – 4004_AFFFh | TMR2           | Блок таймера 2                 |

*Окончание таблицы 6.2*

| Адресное пространство   | Название блока | Описание                                    |

|-------------------------|----------------|---------------------------------------------|

| 4004_9000h – 4004_9FFFh | TMR1           | Блок таймера 1                              |

| 4004_8000h – 4004_8FFFh | TMR0           | Блок таймера 0                              |

| 4004_7000h – 4004_7FFFh | SPI            | Последовательный интерфейс SPI              |

| 4004_6000h – 4004_6FFFh | UART1          | Последовательный приемопередатчик UART1     |

| 4004_5000h – 4004_5FFFh | UART0          | Последовательный приемопередатчик UART0     |

| 4004_4000h – 4004_4FFFh | DMA            | Контроллер прямого доступа к памяти DMA     |

| 4004_3000h – 4004_3FFFh | WDT            | Сторожевой таймер WDT                       |

| 4004_2000h – 4004_2FFFh | PMU            | Блок управления питанием PMU                |

| 4004_1000h – 4004_1FFFh | RCU            | Блок управления тактированием и сбросом RCU |

| 4004_0000h – 4004_0FFFh | SIU            | Блок системных функций                      |

| 4003_0000h – 4003_FFFFh | MFLASH         | Flash-память                                |

| 4002_0000h – 4002_FFFFh | CAN            | Контроллер CAN                              |

| 4001_1000h – 4001_1FFFh | GPIOB          | Порт В                                      |

| 4001_0000h – 4001_0FFFh | GPIOA          | Порт А                                      |

| 4000_0000h – 4000_FFFFh | ADC            | Блок АЦП                                    |

## 7 Контроллер Flash-памяти

### 7.1 Основная Flash-память

Основная Flash-память может использоваться для хранения программ и данных пользователя. Размер основной Flash-памяти составляет 64 Кбайт (64 страницы по 1 Кбайт), и в адресном пространстве она занимает диапазон с 0000h по FFFFh.

Чтение Flash-памяти осуществляется через две шины АНВ: I-code (для команд) и D-code (для данных). Чтение D-code шины имеет приоритет. На обеих шинах при попытке записи в любую область, чтении из несуществующей области, чтении во время, когда Flash-память занята (стирание, запись), транзакция проходит успешно с неопределенными данными на выходе.

Память доступна для чтения, записи, полного и постраничного стирания через регистры данных DATA1 и DATA0, адреса ADDR, команд CMD, статуса STAT блока MFLASH. Запись необходимо производить в предварительно очищенную ячейку памяти. Стирание памяти осуществляется полностью или постранично.

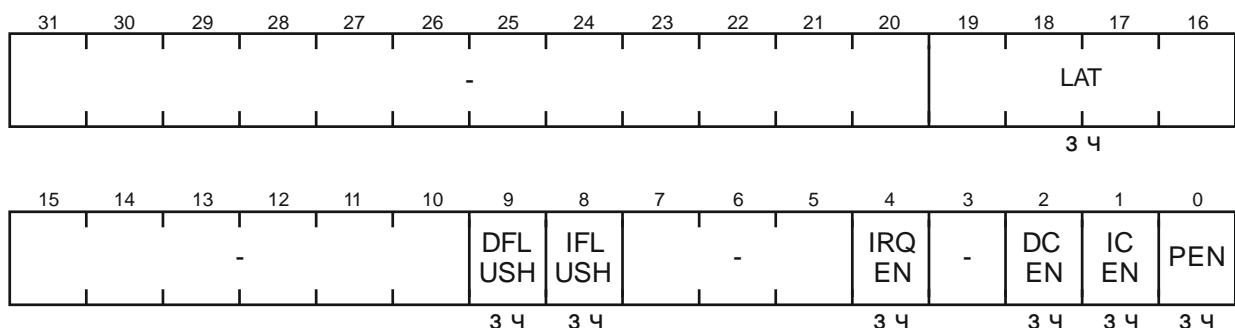

Минимальное время чтения данных из Flash-памяти составляет около 30 нс. Поэтому, исходя из выбранной рабочей частоты, следует задать определенное количество дополнительных тактов ожидания, необходимое для стабильного чтения из Flash-памяти. Данный параметр заносится в поле LAT регистра CTRL, см. таблицу 7.1.

Таблица 7.1 – Значения параметра (количество дополнительных тактов ожидания) в поле LAT регистра CTRL в зависимости от частоты сигнала SYSCLK

| fSYSCLK, МГц, не более | Количество дополнительных тактов ожидания в поле LAT регистра CTRL при чтении Flash-памяти |

|------------------------|--------------------------------------------------------------------------------------------|

| 100                    | 3                                                                                          |

| 90                     | 2                                                                                          |

| 60                     | 1                                                                                          |

| 30                     | 0                                                                                          |

Примечание – Значение параметра после сброса равно 1.

#### Операция предвыборки

При запросе данных на шине по адресу, по которому не осуществлялась предвыборка, выполняются следующие действия:

- 1 Сигнал готовности на шине устанавливается в ноль и задерживает транзакцию.

- 2 По запрашиваемому адресучитываются два двойных слова (64 бит) данных из Flash-памяти. Далее эти данные записываются во внутренний первый буфер.

- 3 Требуемое слово передается на шину АНВ, и сигнал готовности устанавливается в единицу.

4 Сразу после установки сигнала готовности, из Flash-памятичитываются два двойных слова данных по следующему адресу. Данные сохраняются во втором буфере. Если во время считывания этих данных появляются запросы по адресам, сохраненным в первом буфере, ответ возникает мгновенно, если по другим адресам, то готовность на шине устанавливается в ноль, происходит ожидание завершения считывания во второй буфер и далее возврат к действию 2.

5 Если приходят запросы по адресам, сохраненным в первом буфере, ответ возникает мгновенно, если по адресам находящимся во втором буфере, ответ также возникает мгновенно. Далее переписывается первый буфер значением второго и считывается следующий адрес из Flash-памяти. Если приходят запросы по адресам не из первого и второго буферов, то возврат к действию 1.

## Операция кэширования

Основная Flash-память дополнена блоками кэш-памяти по 1 Кбайт на каждую из шин I-code и D-code. Доступ к этим блокам осуществляется за 1 такт системной частоты. При первом обращении к адресу, его данные параллельно заносятся и в кэш-память, и сохраняются там. Если в дальнейшем произойдет повторное обращение к тому же адресу, данные будут прочитаны уже из кэш, обращения к медленной Flash-памяти не будет. Но данные в кэш, которые были запрошены давно, могут быть вытеснены более свежими данными, обращение к которым было позже. Таким образом, кэшированная информация постоянно обновляется, но участки программного кода, вызываемые чаще всего, с большей вероятностью окажутся в кэш. За счет этого достигается повышенная скорость выполнения такого кода.

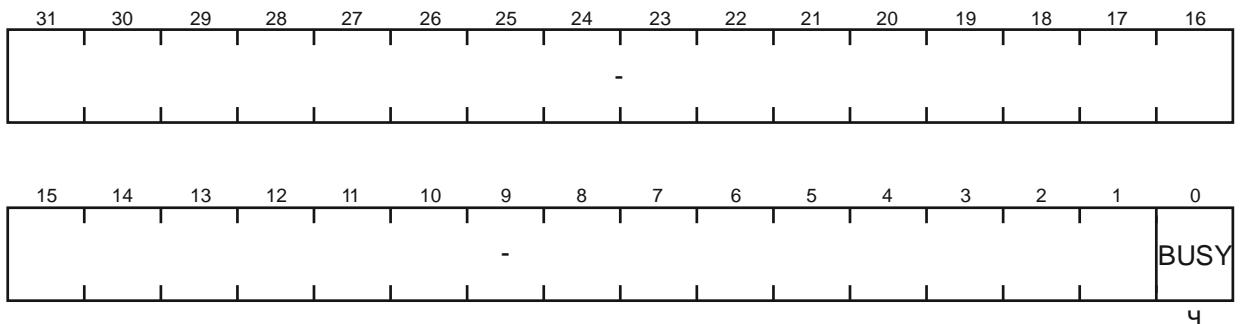

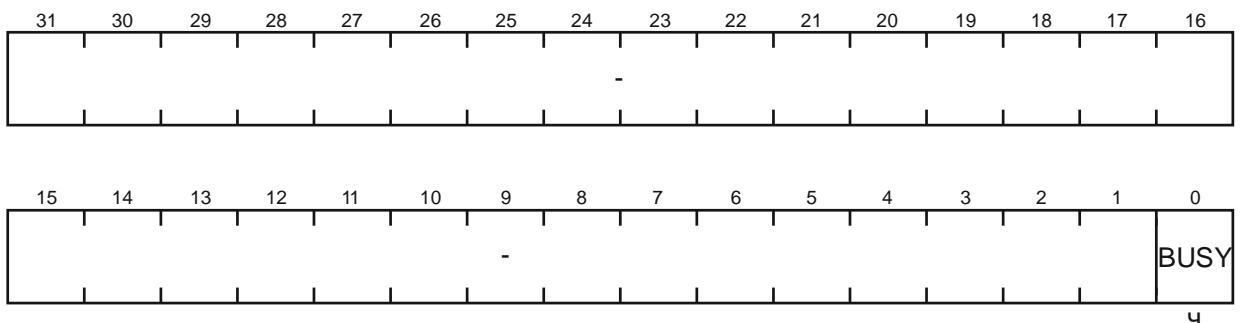

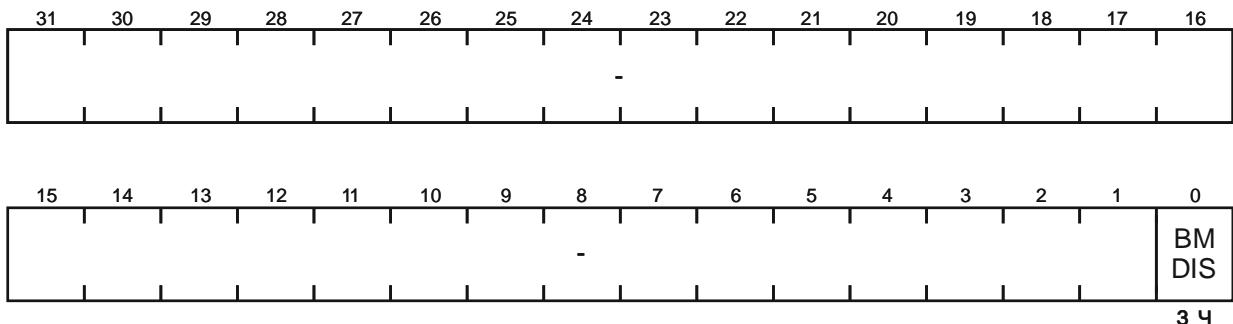

Предвыборка и кэш на каждую из шин I-code и D-code включаются отдельно в регистре CTRL. Перед включением кэша необходимо его сбросить, установив соответствующий бит FLUSH регистра CTRL. Во время процедуры сброса бит BUSY соответствующего регистра статуса кэш будет держаться в 1. После успешного завершения сброса будет сброшен и данный бит, после чего можно продолжать выполнение основной программы.

## 7.2 Загрузочная Flash-память

Загрузочная Flash-память (NVR область) может использоваться для хранения пользовательской программы-загрузчика, которая посредством одного из имеющихся интерфейсов получает данные для прошивки основной памяти. Размер загрузочной Flash-памяти составляет 4 Кбайт (4 страницы по 1 Кбайт каждая). Но для программы-загрузчика доступны только первые 3 Кбайт. Верхний килобайт отведен под хранение пользовательских данных, а в его первом байте (абсолютный адрес C00h) располагается конфигурационное слово CFGWORD, содержащее параметры загрузки и защиты контроллера. Описание битов CFGWORD представлено в таблице 7.2.

Примечание – параллельный доступ к NVR и основной области Flash-памяти невозможен. Так например, ядро, исполняющее код из основной области Flash будет вынужденно остановиться на время осуществления модификации NVR области, т.к. не может в это время считывать инструкции. Подобное справедливо и для обратного случая.

Таблица 7.2 – Конфигурационное слово CFGWORD

| CFGWORD + C00h (смещение относительно начального адреса NVR области) |      |                                                           |

|----------------------------------------------------------------------|------|-----------------------------------------------------------|

| Поле                                                                 | Биты | Описание                                                  |

| BMODEDIS                                                             | 4    | Бит источника загрузки                                    |

|                                                                      |      | 0   Загрузка из NVR области                               |

|                                                                      |      | 1   Загрузка из основной Flash-памяти (по умолчанию)      |

| FLASHWE                                                              | 3    | Бит включения защиты основной Flash-памяти                |

|                                                                      |      | 0   Запрет записи и стирания основного блока Flash-памяти |

|                                                                      |      | 1   Защита выключена (по умолчанию)                       |

| NVRWE                                                                | 2    | Бит включения защиты NVR области Flash-памяти             |

|                                                                      |      | 0   Запрет записи и стирания NVR блока Flash-памяти       |

|                                                                      |      | 1   Защита выключена (по умолчанию)                       |

| DEBUGEN                                                              | 1    | Бит разрешения работы системы отладки ядра                |

|                                                                      |      | 0   Откладка отключена                                    |

|                                                                      |      | 1   Откладка включена (по умолчанию)                      |

| JTAGEN                                                               | 0    | Бит разрешения работы пинов JTAG/SWD                      |

|                                                                      |      | 0   Работа запрещена                                      |

|                                                                      |      | 1   Работа разрешена (по умолчанию)                       |

| –                                                                    | 7-5  | Зарезервировано                                           |

При установленных битах NVRWE или FLASHWE запрещается любая модификация соответствующей области памяти через регистровый интерфейс. Операции записи и стирания интерпретируются как операция чтения, при этом стандартным образом продолжают работать механизмы флагов из регистра STAT.

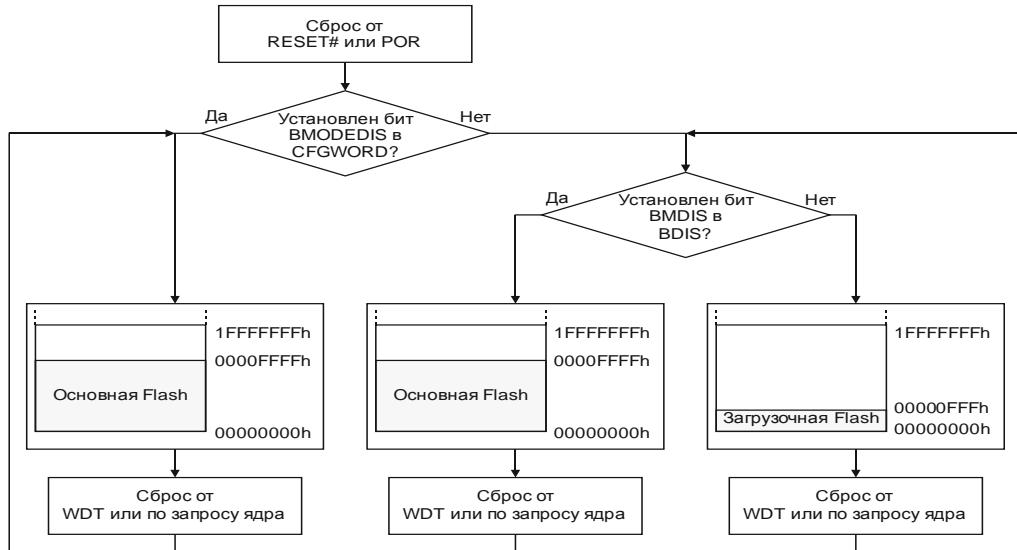

По умолчанию после стирания CFGWORD включена загрузка из основной памяти. Чтобы использовать загрузчик, необходимо сбросить в нем бит BMODEDIS. Тогда при загрузке произойдет подмена основной Flash-памяти на область загрузочной Flash. Т. е. при обращении по адресам 0000\_0000h – 0000\_0FFFh будут прочитаны данные из загрузочной Flash-памяти, см. рисунок 7.1.

Рисунок 7.1 – Блок-схема алгоритма загрузки микроконтроллера

При этом обе области полностью доступны для чтения, записи, стирания через регистровый интерфейс MFLASH.

Есть возможность после отработки программы-загрузчика сразу перезапустить контроллер с области основной Flash-памяти. Для этого необходимо установить бит BMDIS регистра BDIS блока MFLASH и подать команду программной перезагрузки контроллера (установить бит SYSRESETREQ регистра AIRCR ядра). Устройство перезагрузится уже с основной Flash-памятью. Данная комбинация действий будет работать только до внешнего сброса или сброса по питанию контроллера. После внешней перезагрузки при сброшеном бите BMODEDIS загрузка опять начнется с загрузочной Flash-памяти. Чтобы отключить полностью старт с загрузочной Flash-памяти, необходимо вернуть бит BMODEDIS в 1. Это возможно осуществить, выполнив стирание соответствующей страницы загрузочной Flash-памяти или сервисное стирание всего контроллера. При этом обновленное значение вступит в силу только после внешнего сброса или сброса по питанию. Подобное справедливо и для других битов CFGWORD.

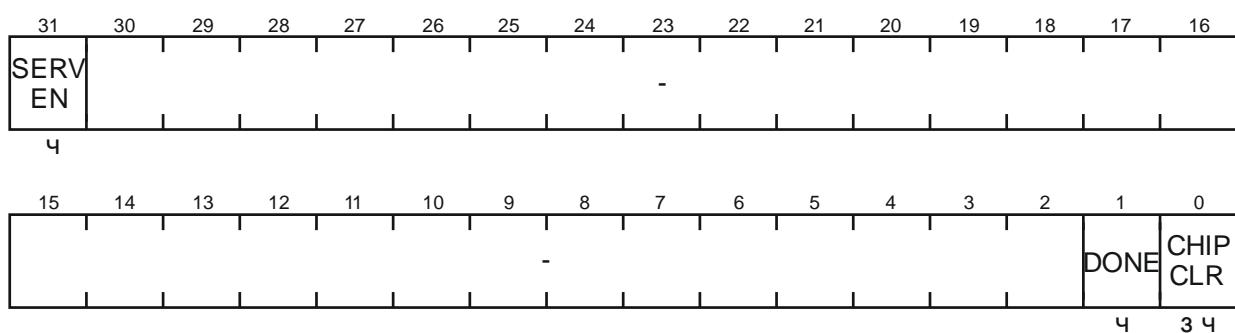

### 7.3 Сервисный сброс всей Flash-памяти

1 Во время сброса микроконтроллера анализируется состояние вывода SERVEN. Если вывод находится в состоянии логической единицы (подтянут к 3,3 В), то загрузочная и основная Flash-памяти переводятся в режим, в котором чтение запрещено (при чтении возвращаются нули). При этом игнорируется состояние битов DEBUGEN и JTAGEN.

2 Далее по отладочному интерфейсу (SWD или JTAG) должна быть подана команда записи значения 0000\_0001h в регистр SERVCTL блока SIU, после чего будет активировано полное стирание загрузочной и основной Flash-памяти. По завершении процесса стирания в этом же регистре выставится флаг DONE

**Примечание** – Если полное стирание не требуется, то во время сброса на выводе SERVEN должен удерживаться логический ноль.

## 8 Контроллер прямого доступа к памяти DMA

Основные свойства и отличительные особенности контроллера прямого доступа к памяти DMA:

- 16 каналов;

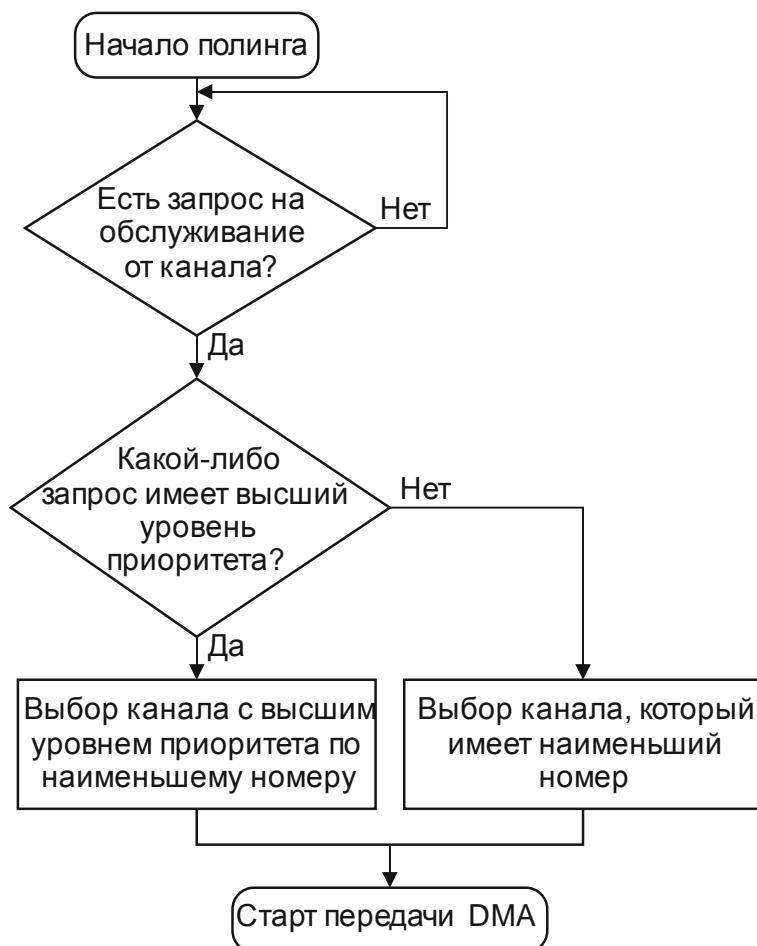

- каждый канал DMA $i$  (где  $i$  от 0 до 15) имеет свои сигналы управления передачей данных и программируемый уровень приоритета;

- каждый уровень приоритета обрабатывается исходя из уровня приоритета, определяемого номером канала DMA $i$ ;

- поддержка различного типа передачи данных в пределах внутреннего ОЗУ: память – память, память – периферия, периферия – память;

- поддержка различных типов циклов;

- поддержка передачи данных различной разрядности;

- каждому каналу DMA $i$  доступна первичная и альтернативная структура управляющих данных канала;

- все данные канала хранятся во внутреннем ОЗУ в структуре управляющих данных канала;

- разрядность данных приемника равна разрядности данных передатчика;

- количество передач в одном цикле контроллера DMA может программироваться от 1 до 1024;

- инкремент адреса передачи может быть больше, чем разрядность данных;

- возможность начать передачи по сигналам от блоков UART, SPI, ADC, TMR, PWM, QEP.

Аппаратные источники запросов каналов контроллера DMA указаны в таблице 8.1.

Таблица 8.1 – Аппаратные источники запросов каналов контроллера DMA

| Номер канала | Аппаратный источник запросов                | Описание                                           |

|--------------|---------------------------------------------|----------------------------------------------------|

| 0            | UART0_TX                                    | Канал DMA от UART0 по передаче                     |

| 1            | UART1_TX                                    | Канал DMA от UART1 по передаче                     |

| 2            | UART0_RX                                    | Канал DMA от UART0 по приему                       |

| 3            | UART1_RX                                    | Канал DMA от UART1 по приему                       |

| 4            | ADC_SEQ0                                    | Канал DMA от секвенсора 0 блока АЦП                |

| 5            | ADC_SEQ1                                    | Канал DMA от секвенсора 1 блока АЦП                |

| 6            | SPI_TX                                      | Канал DMA от SPI по передаче                       |

| 7            | SPI_RX                                      | Канал DMA от SPI по приему                         |

| 8 – 15       | В соответствии с регистром DMAMUX блока SIU | Каналы DMA с конфигурируемыми источниками запросов |

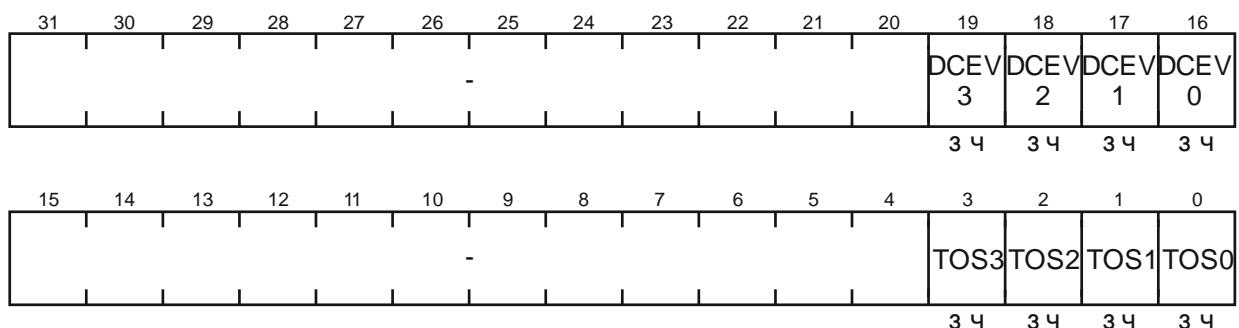

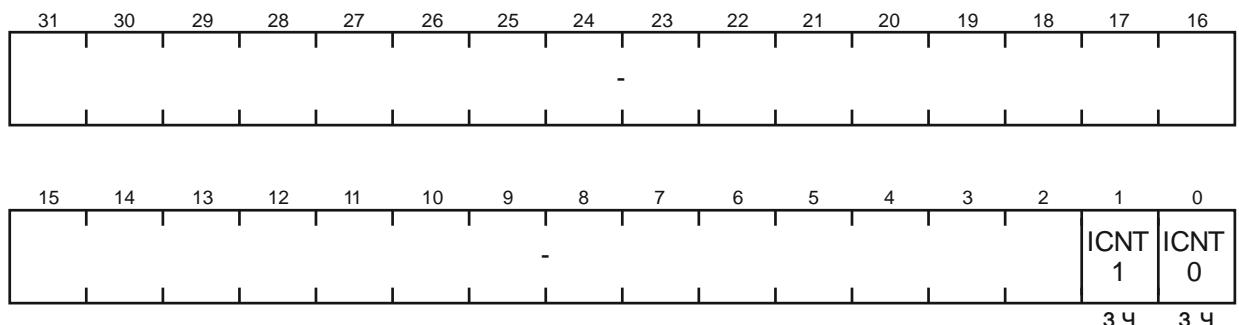

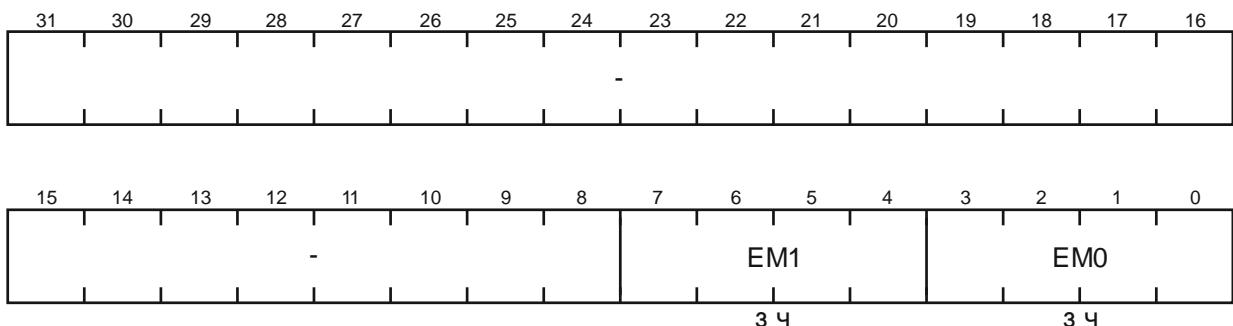

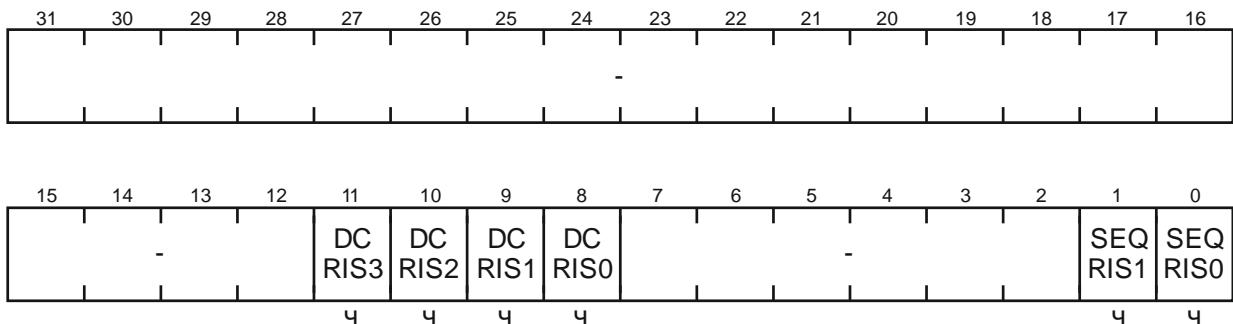

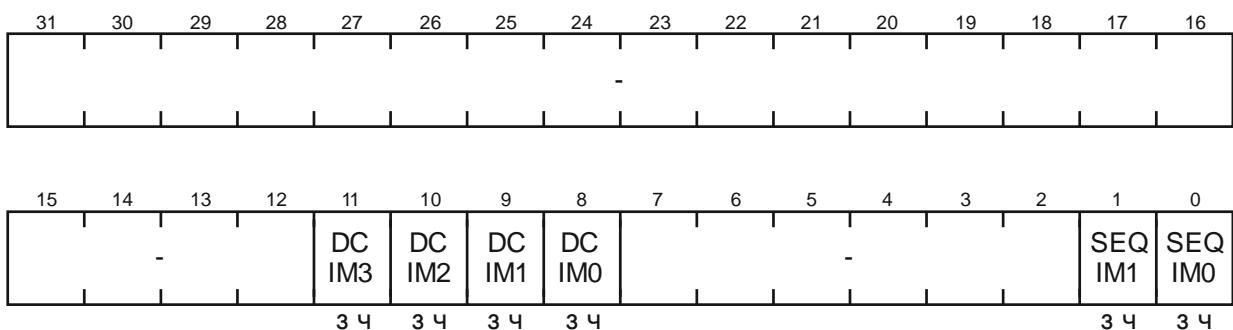

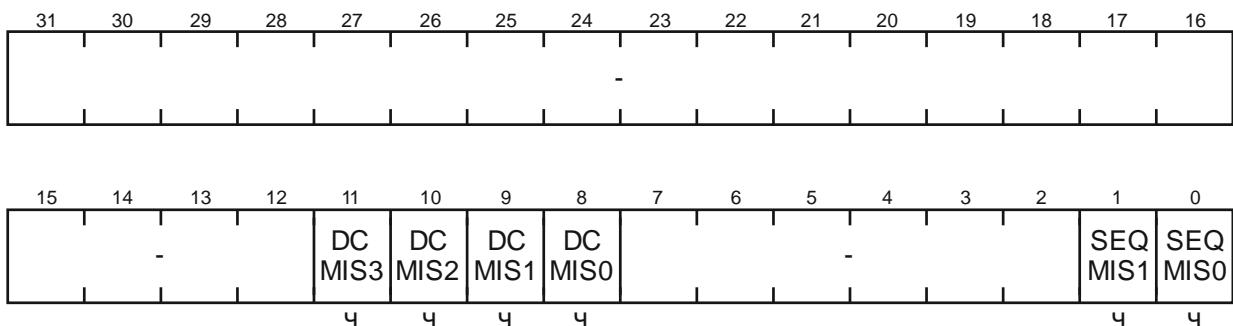

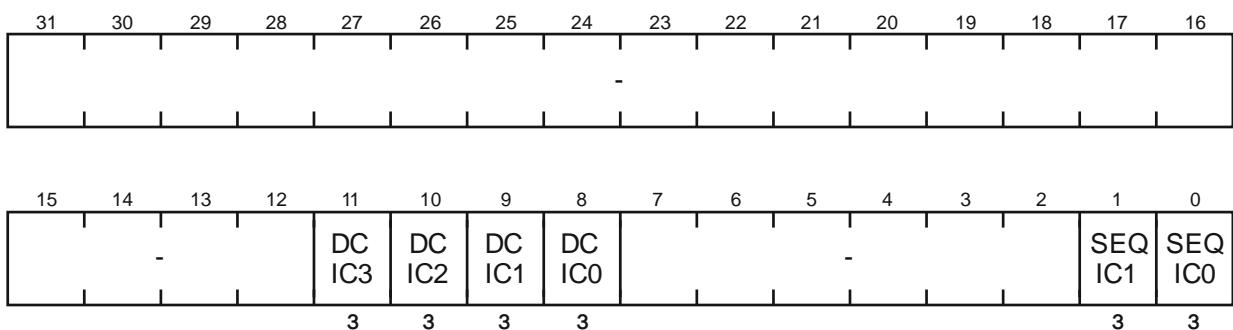

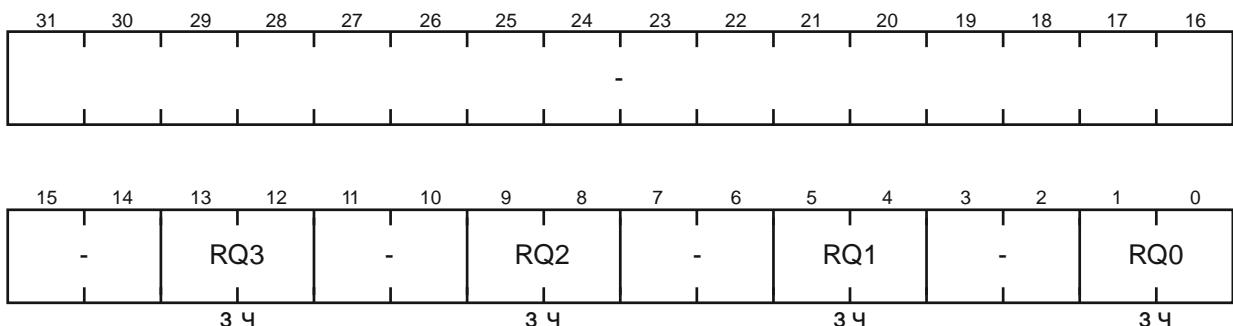

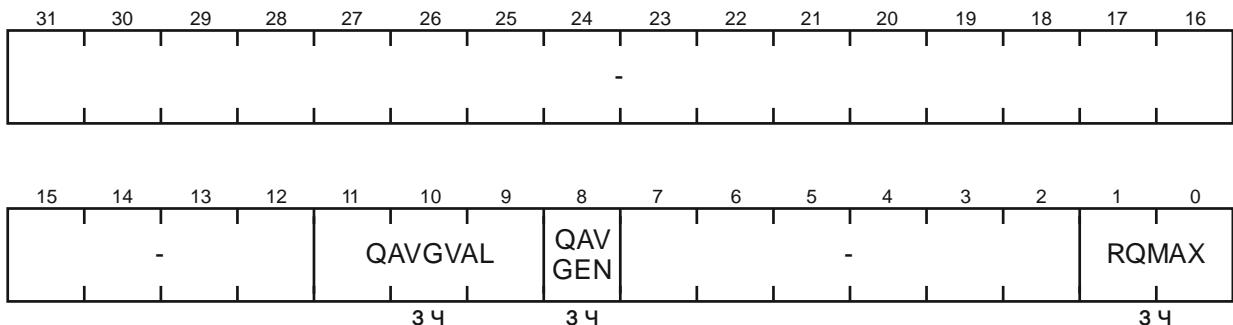

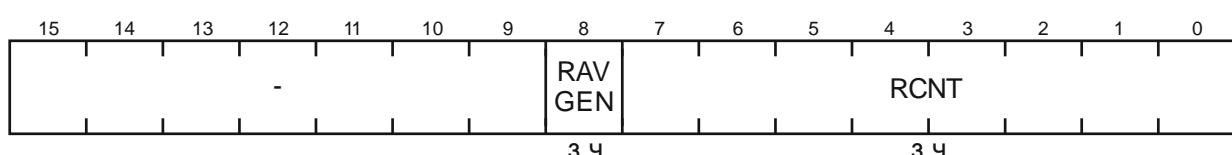

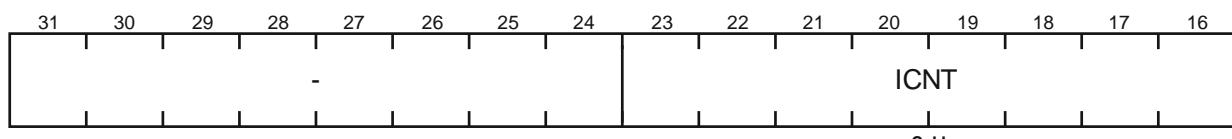

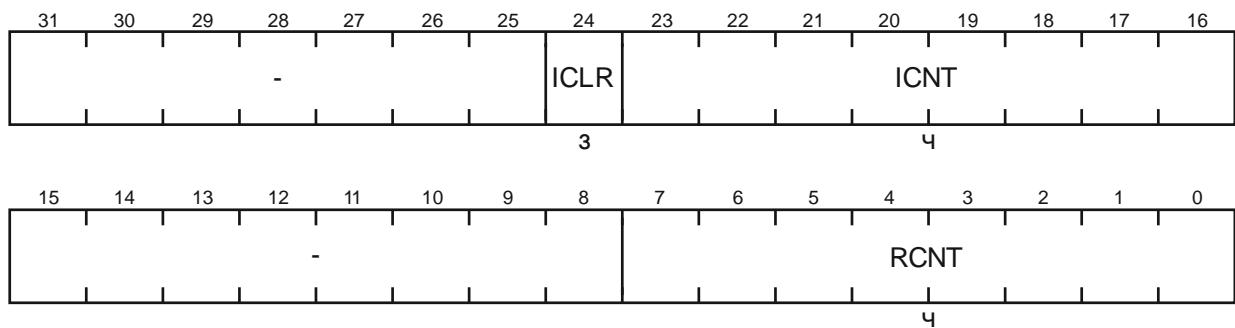

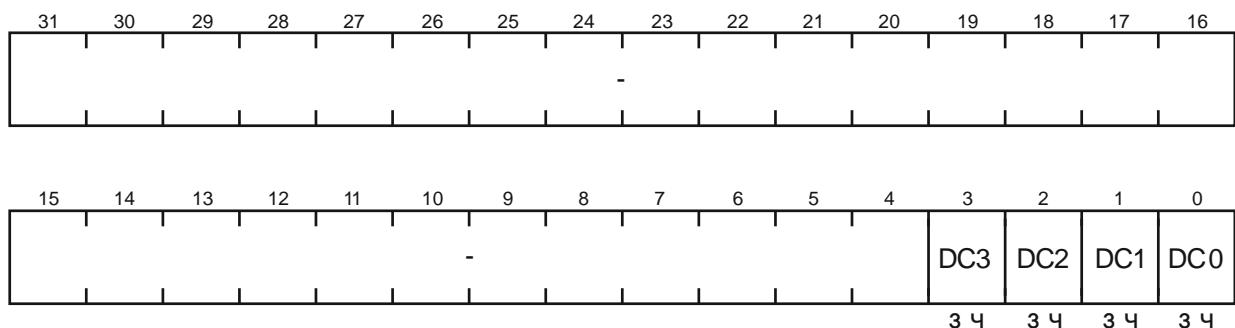

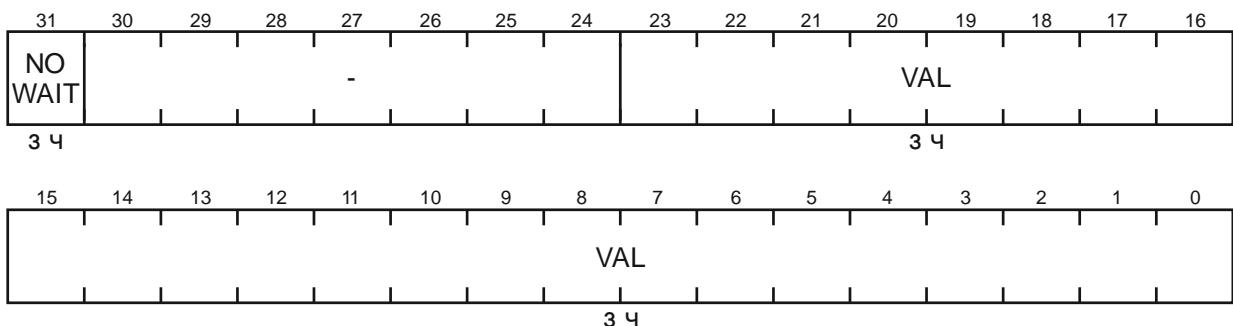

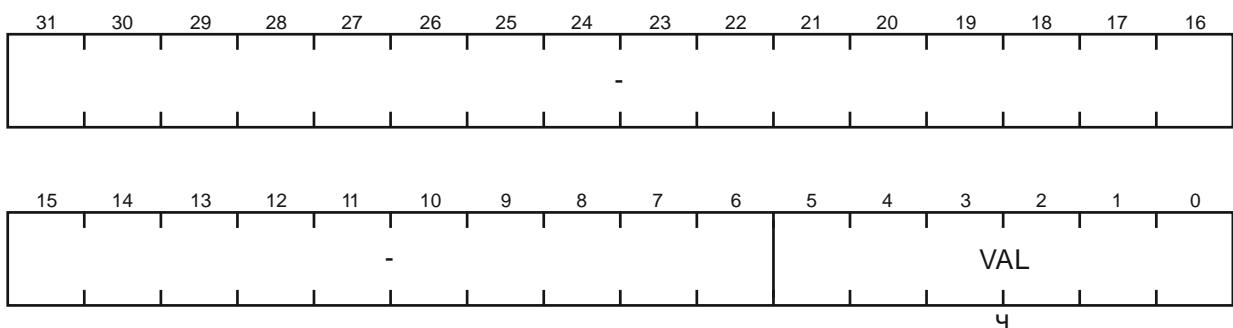

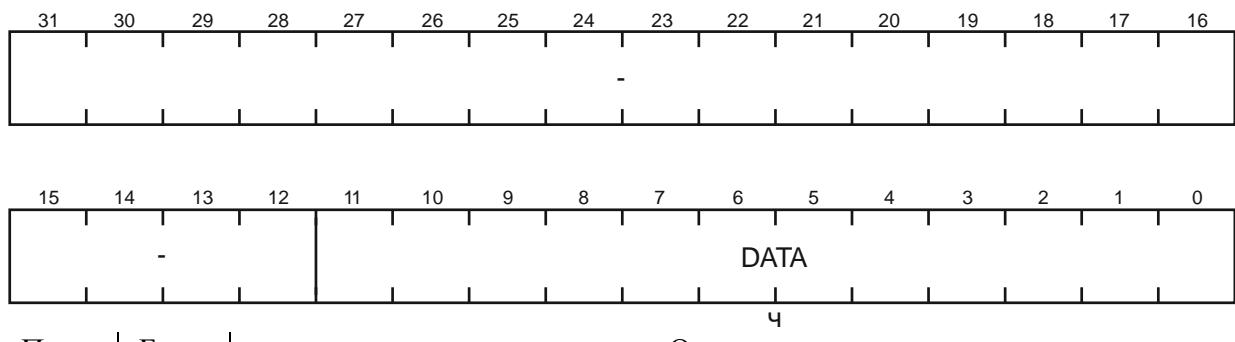

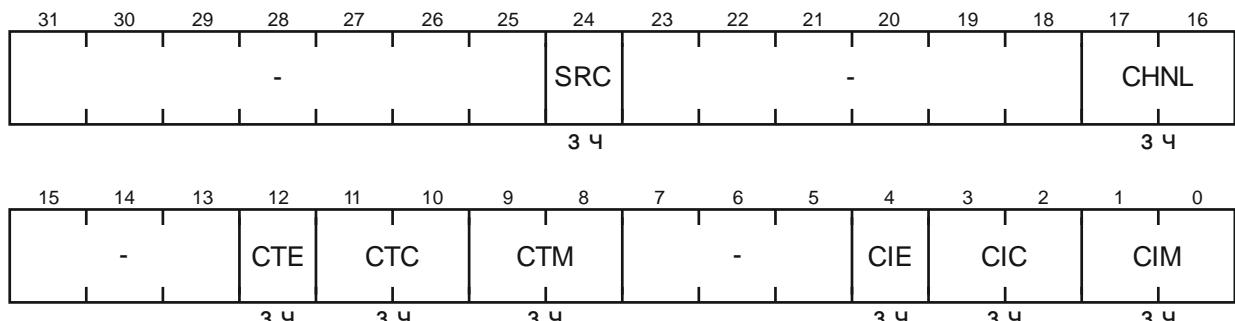

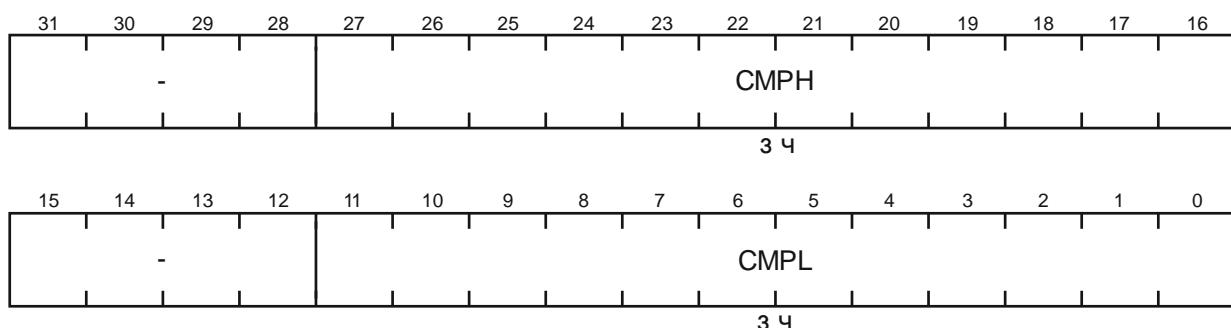

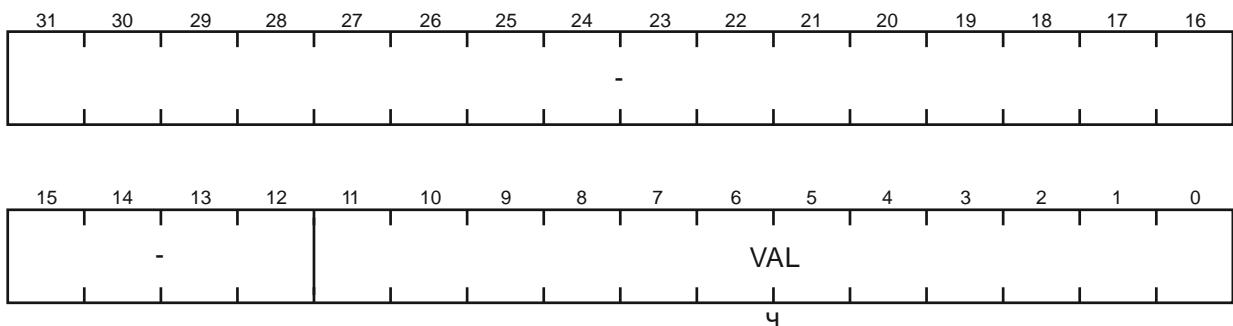

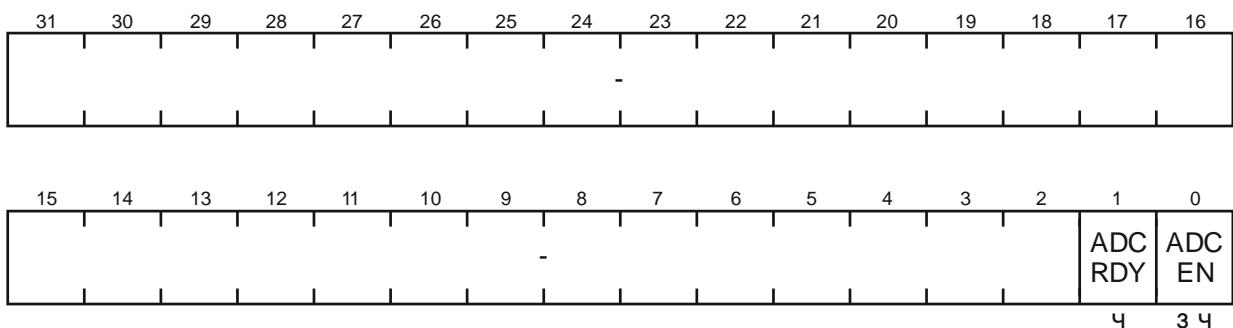

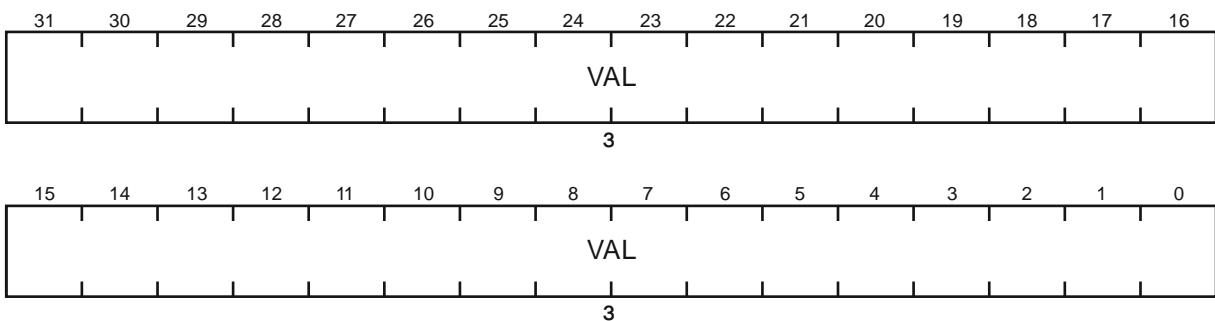

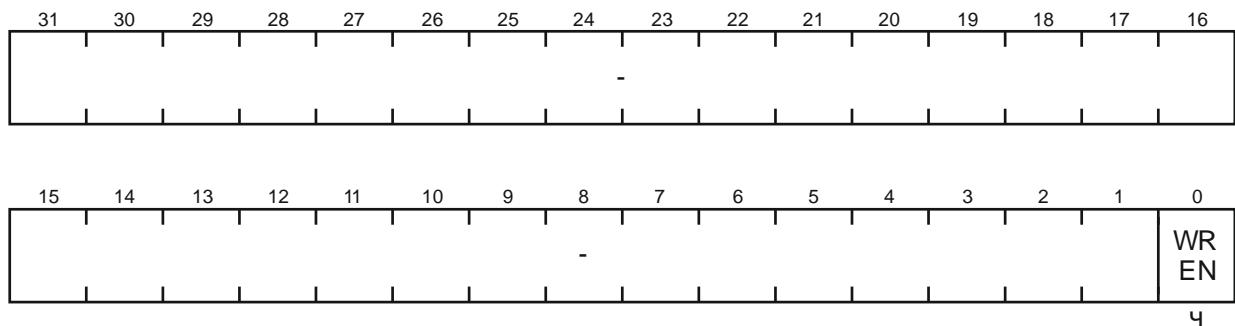

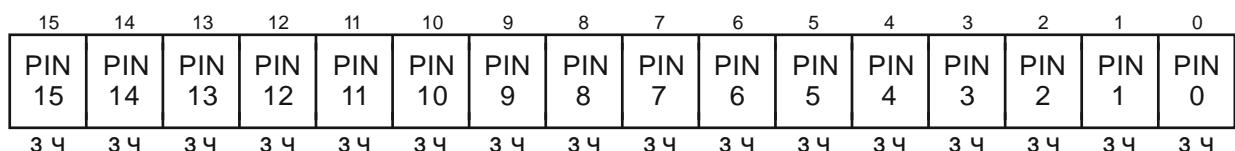

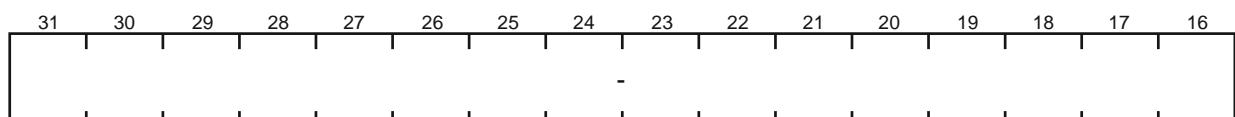

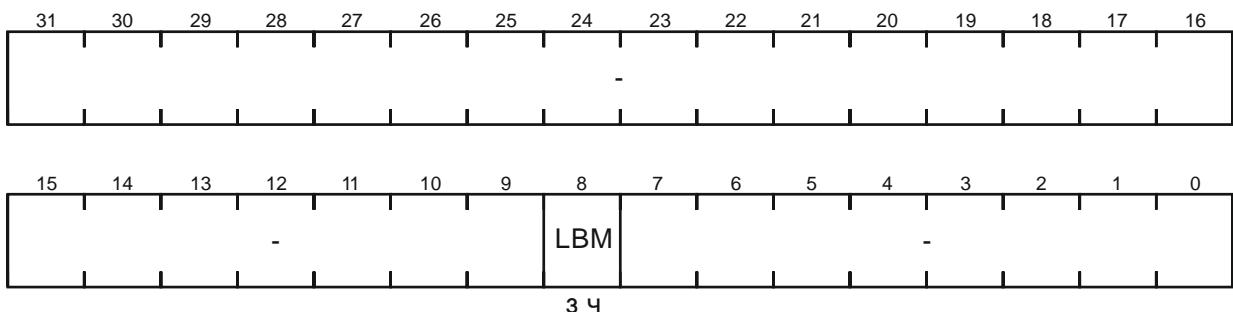

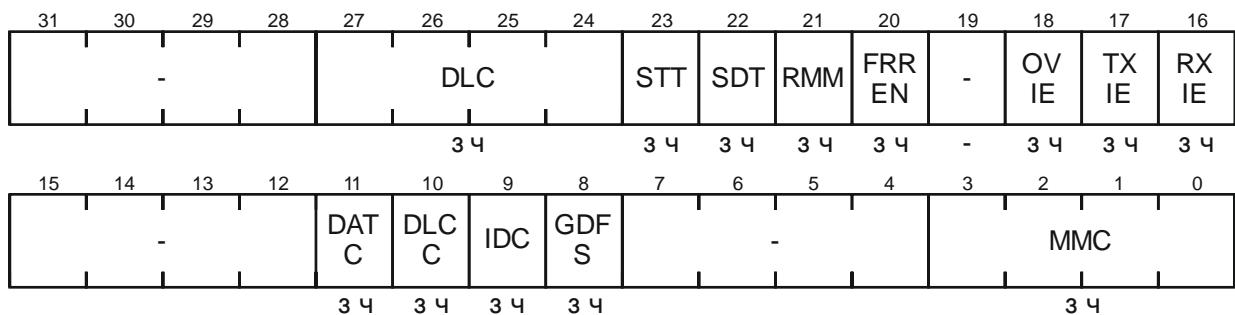

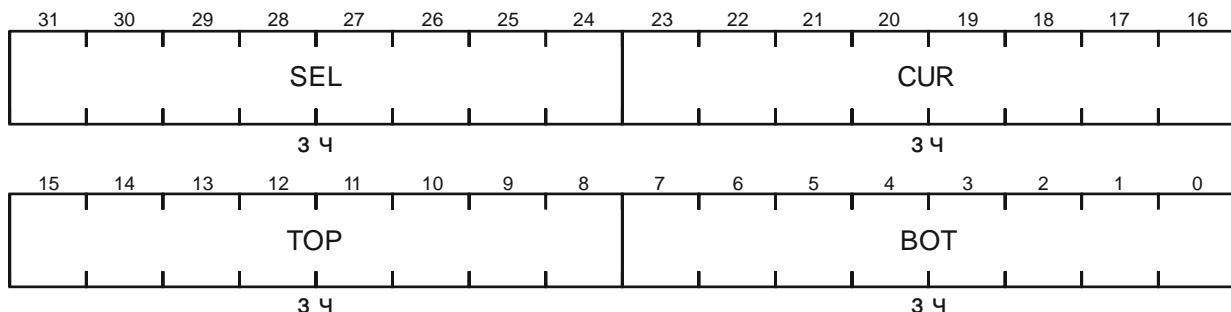

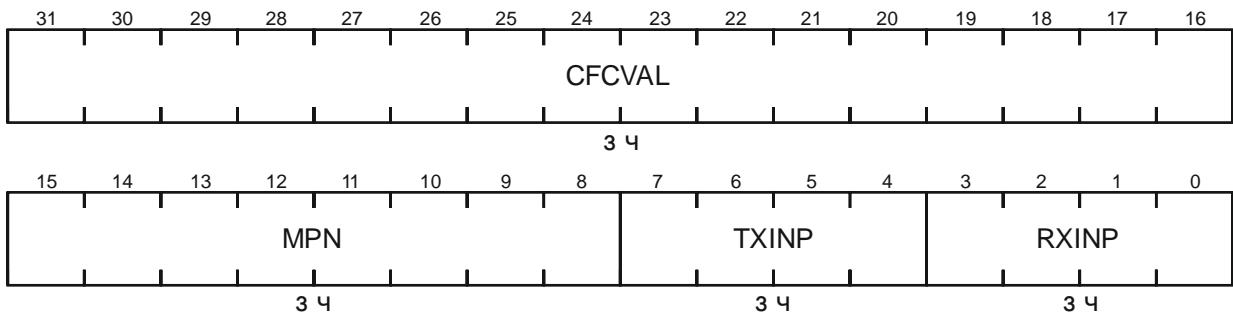

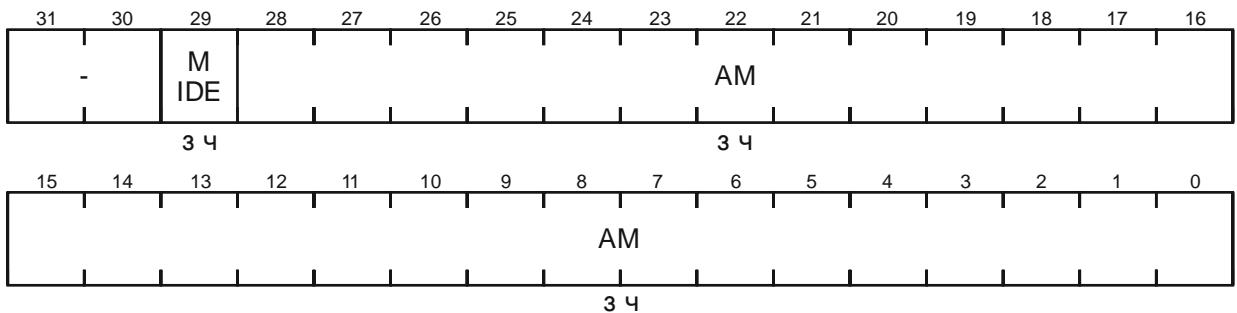

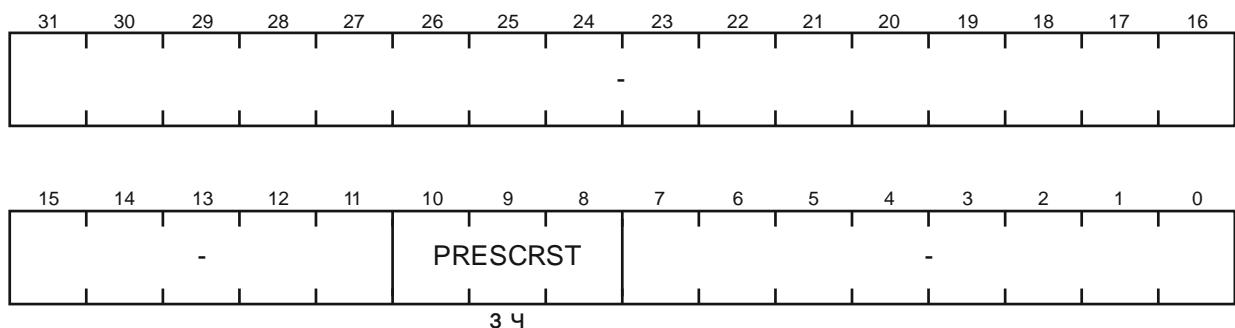

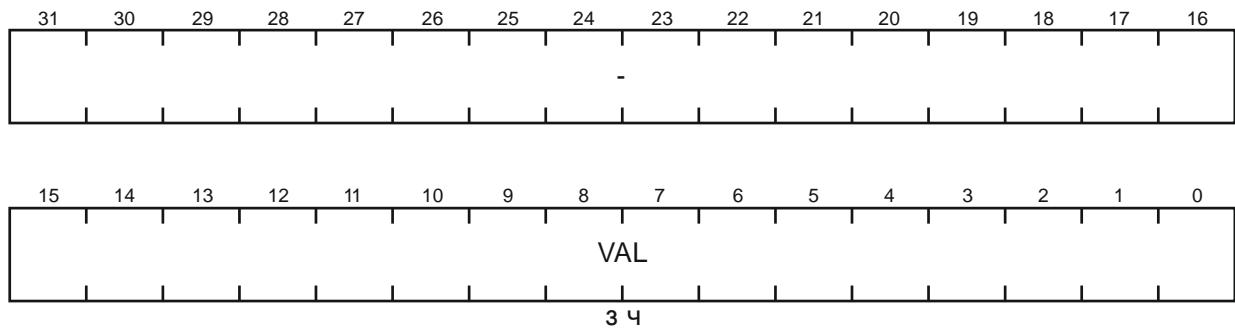

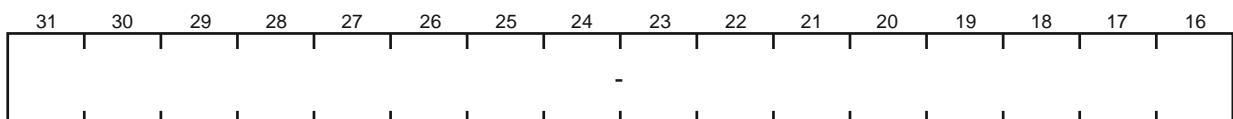

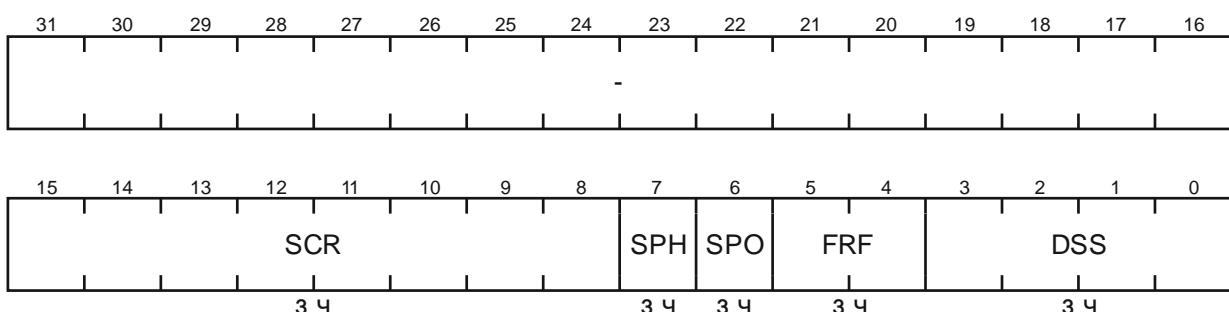

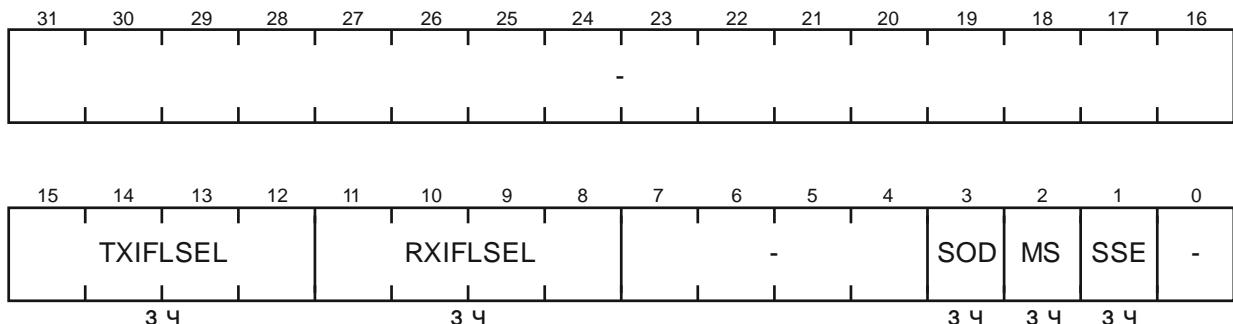

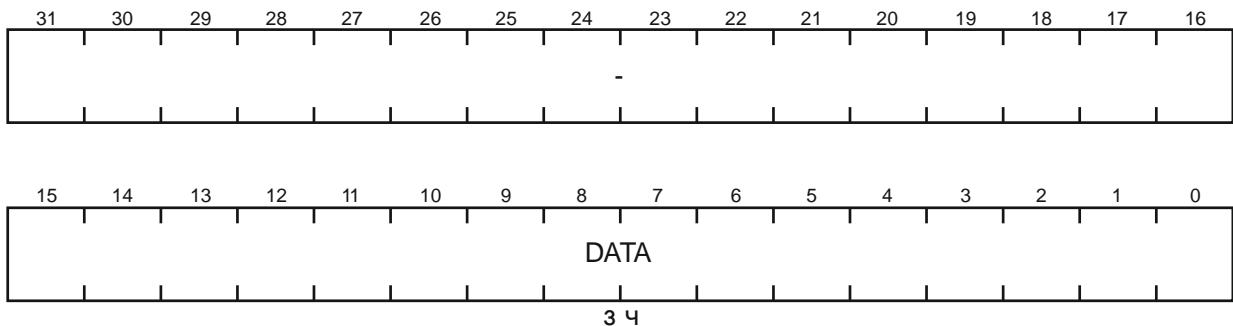

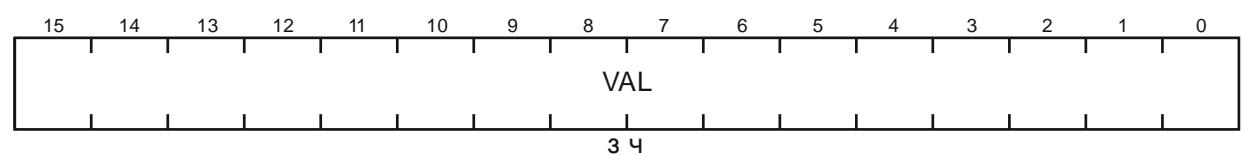

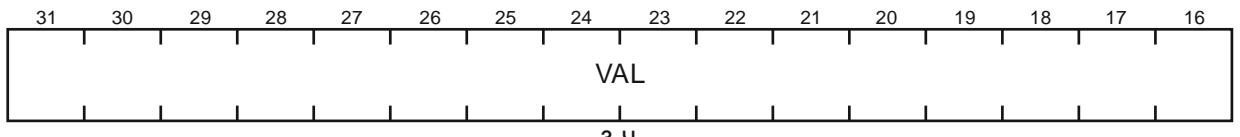

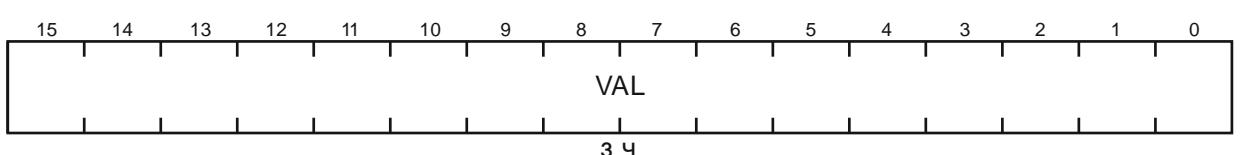

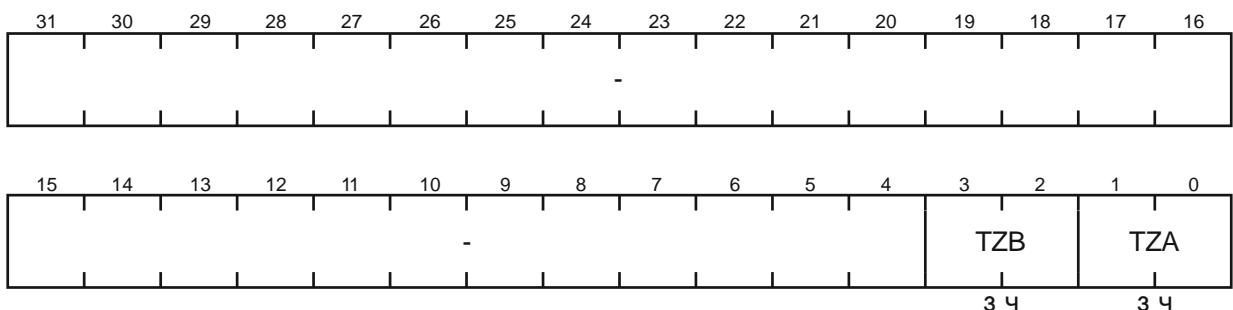

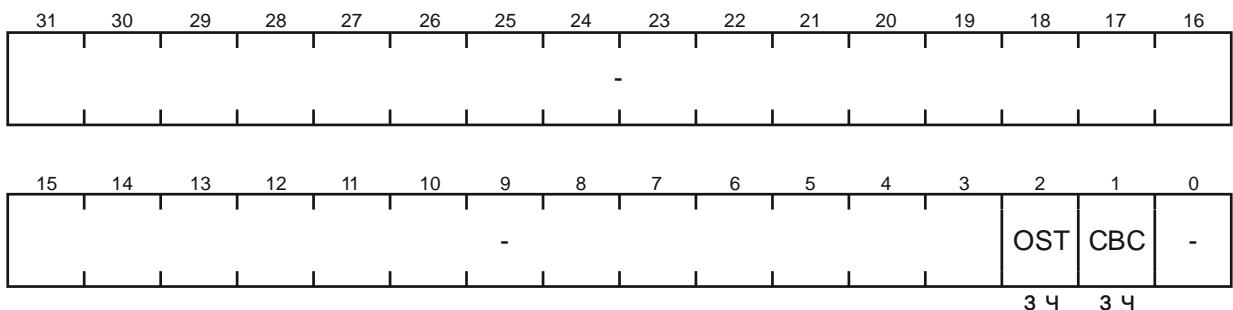

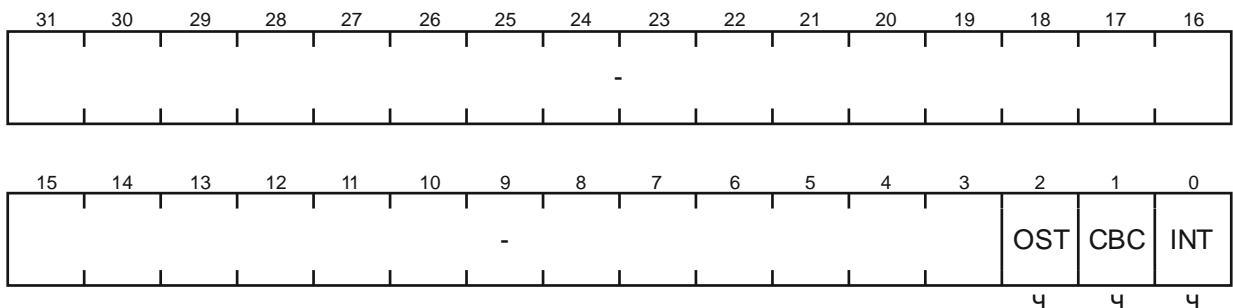

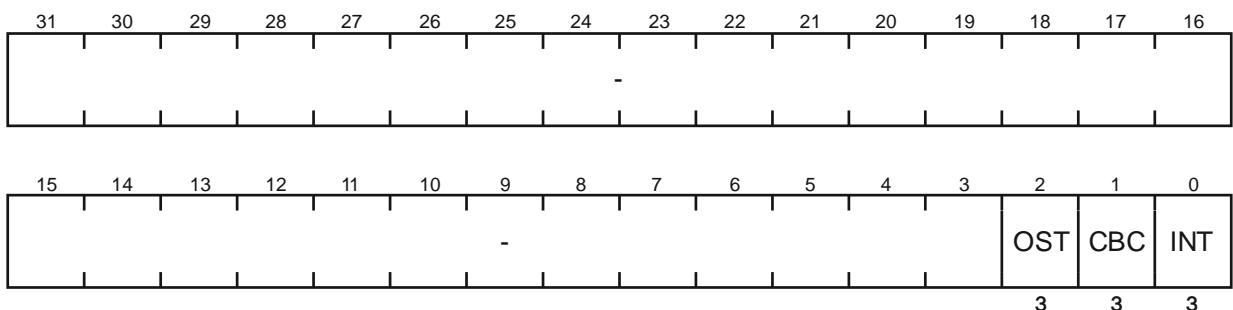

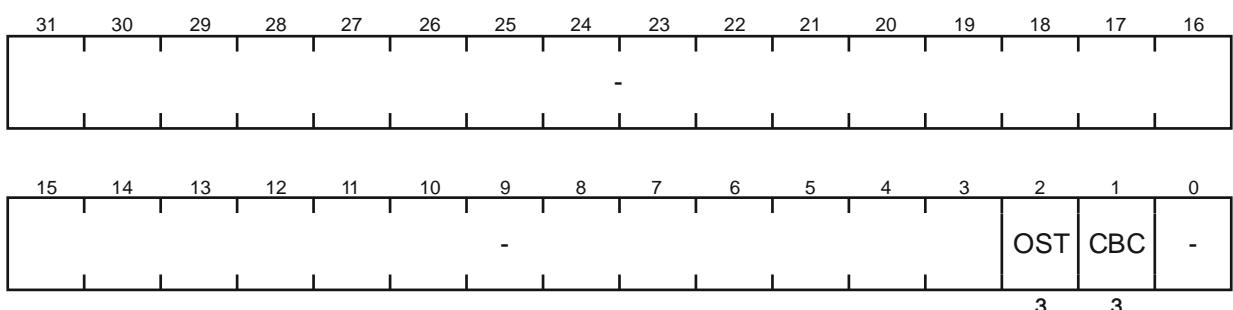

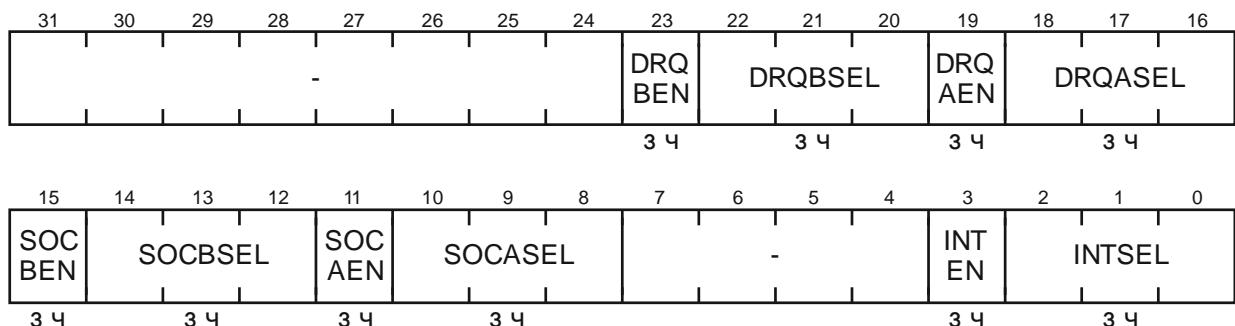

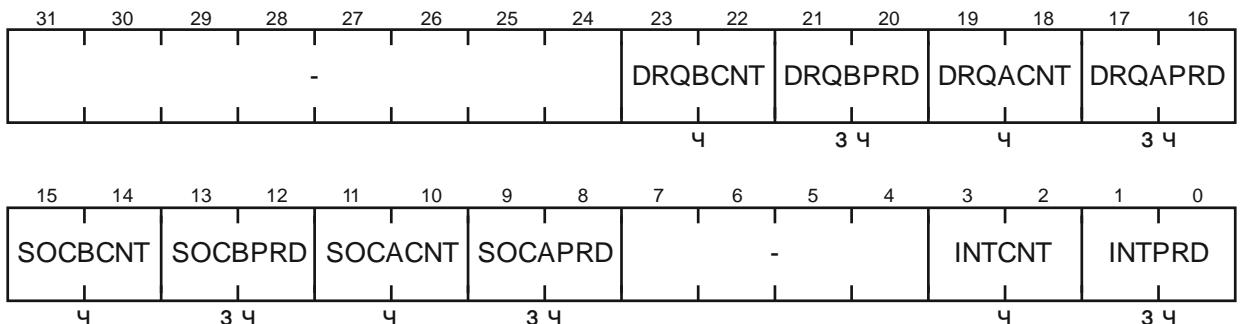

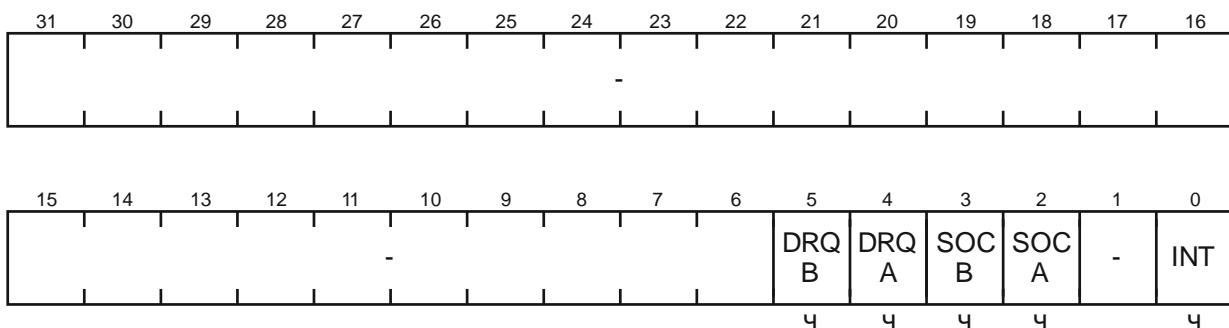

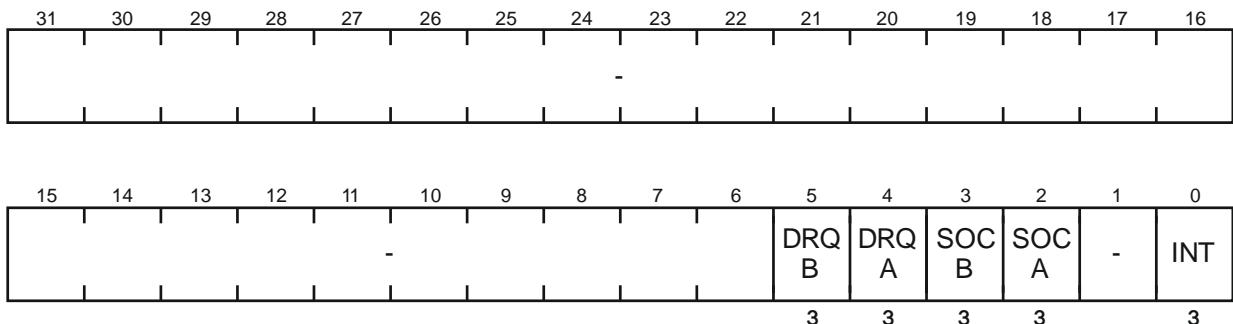

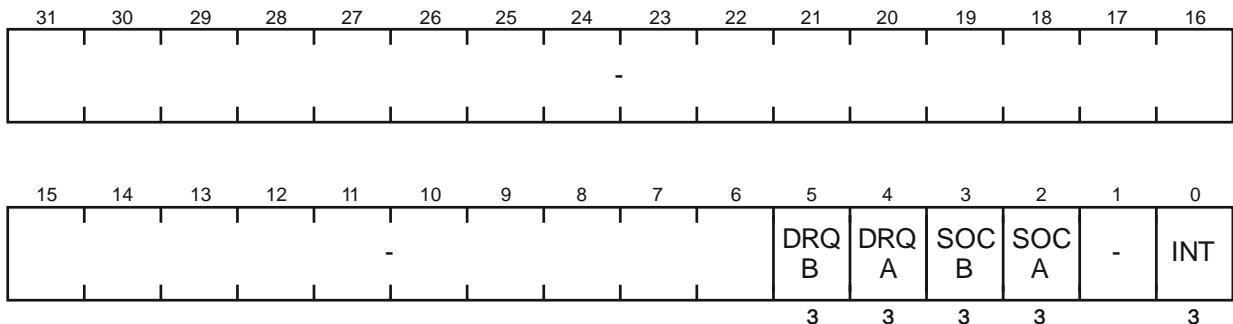

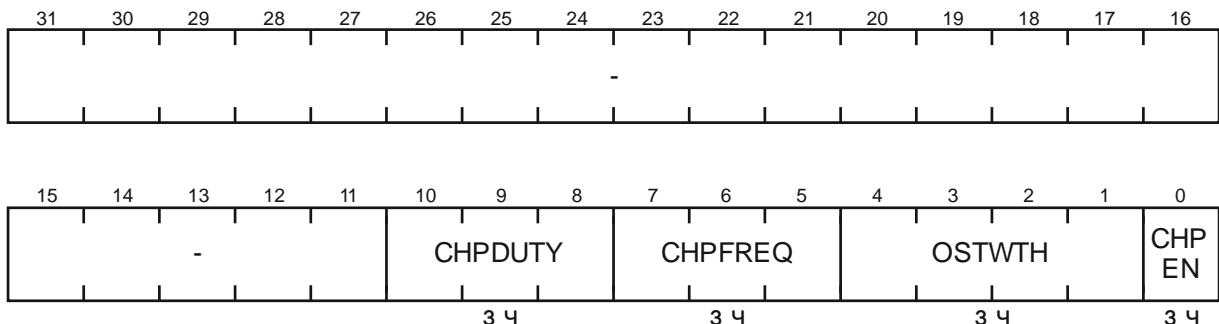

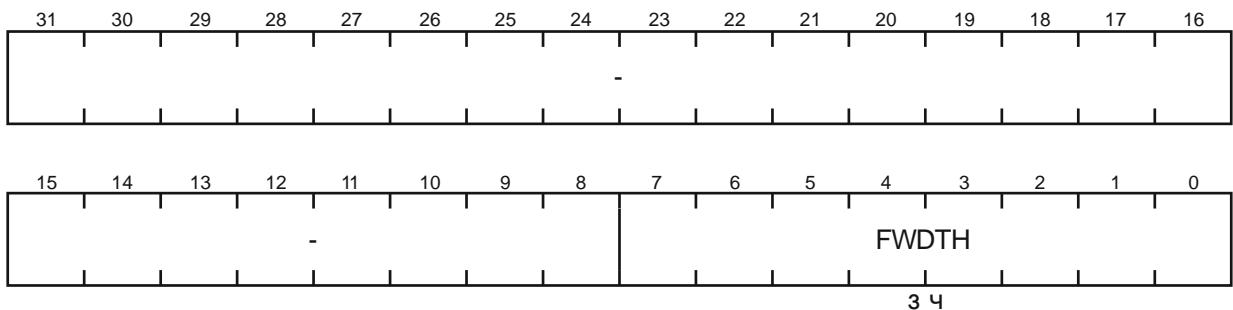

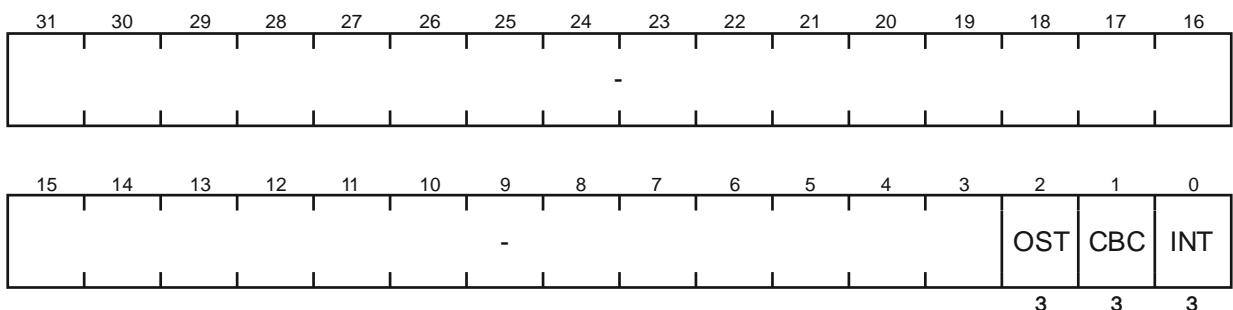

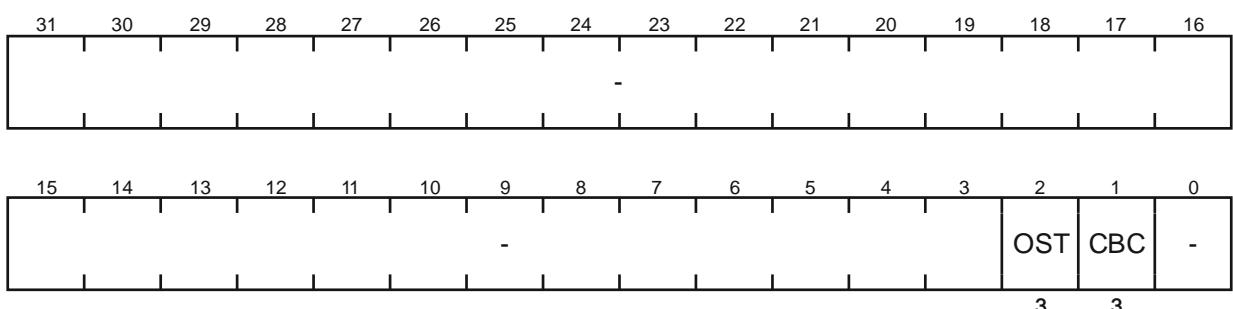

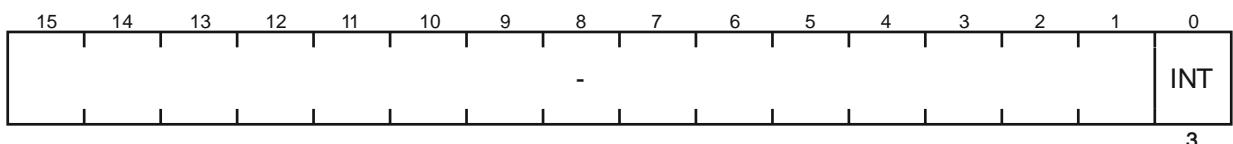

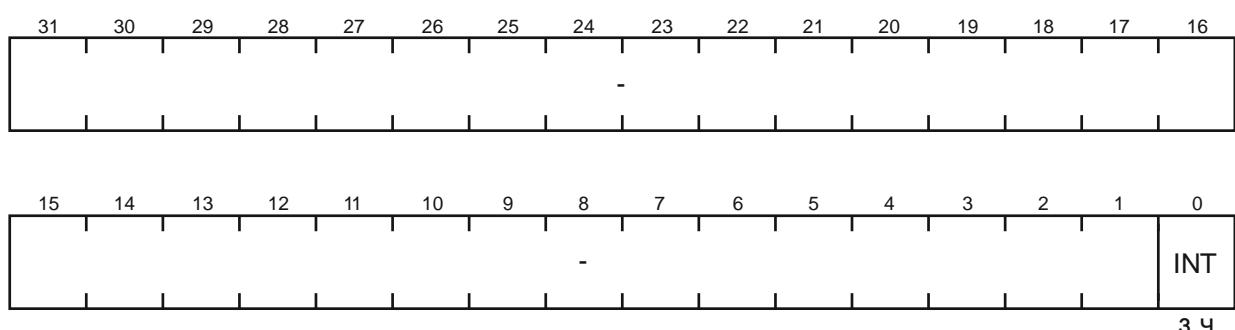

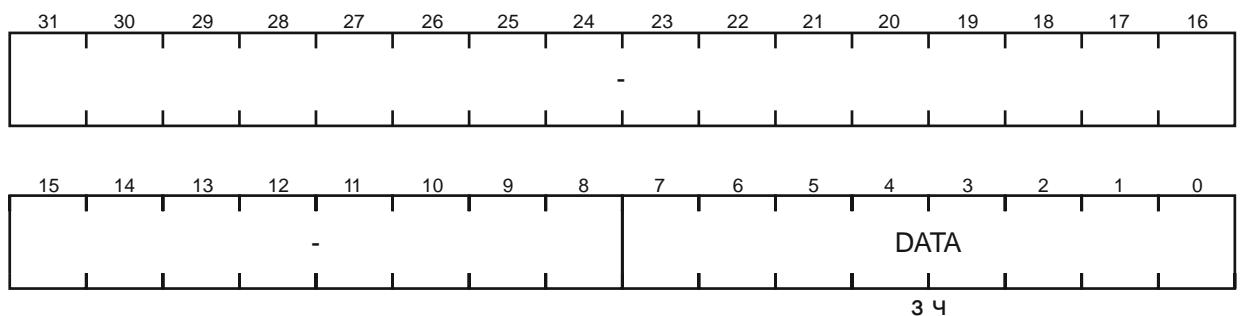

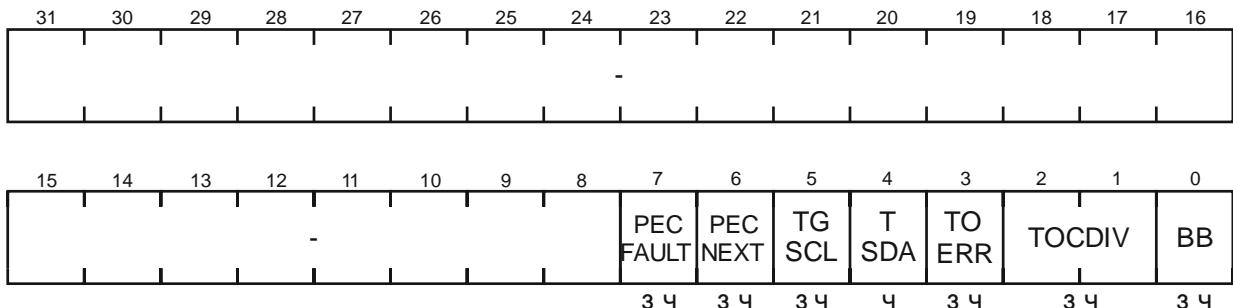

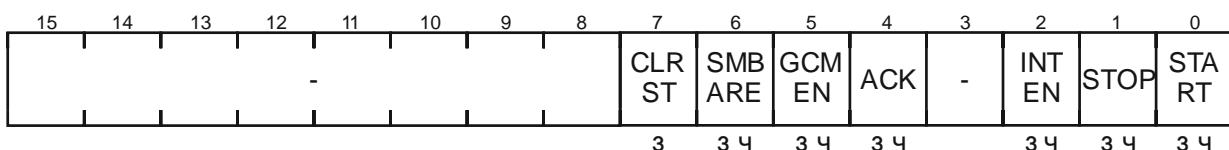

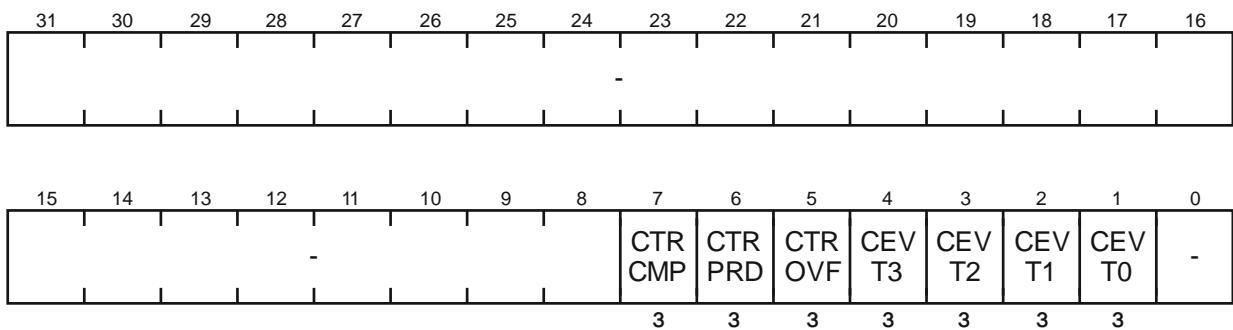

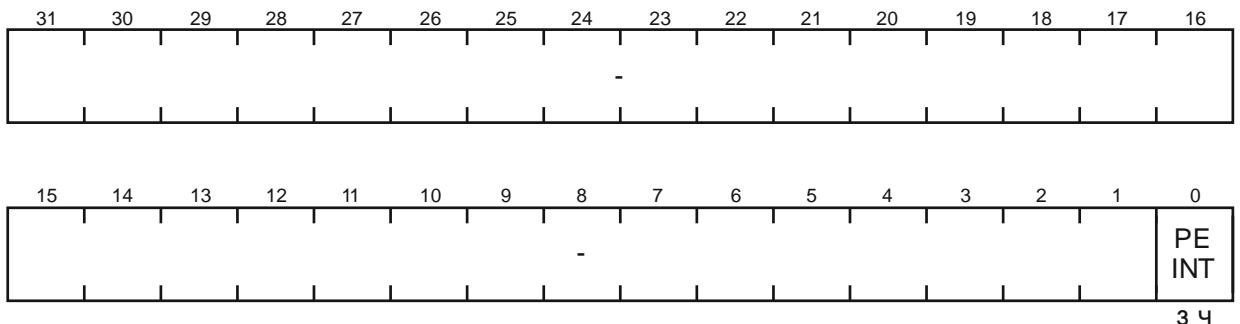

## 8.1 Программное управление контроллером DMA

Контроллер DMA выполняет передачи 8-, 16- и 32-разрядных данных. Разрядность данных источника и приемника должны быть одинаковыми.

Контроллер DMA позволяет управлять инкрементом адреса при чтении данных из источника и при записи данных в приемник. Инкремент адреса зависит от разрядности передаваемых данных: минимальная величина инкремента адреса всегда соответствует разрядности передаваемых данных; максимальная величина – одно слово. Контроллер DMA может быть настроен на работу с фиксированным адресом (например, для работы с FIFO).

Контроллер DMA имеет возможность обслуживать сигналы запроса на одиночный обмен SREQ и сигналы запроса на пакетный обмен BREQ блоков UART, SPI. Блок ADC генерирует только запросы на пакетный обмен BREQ.

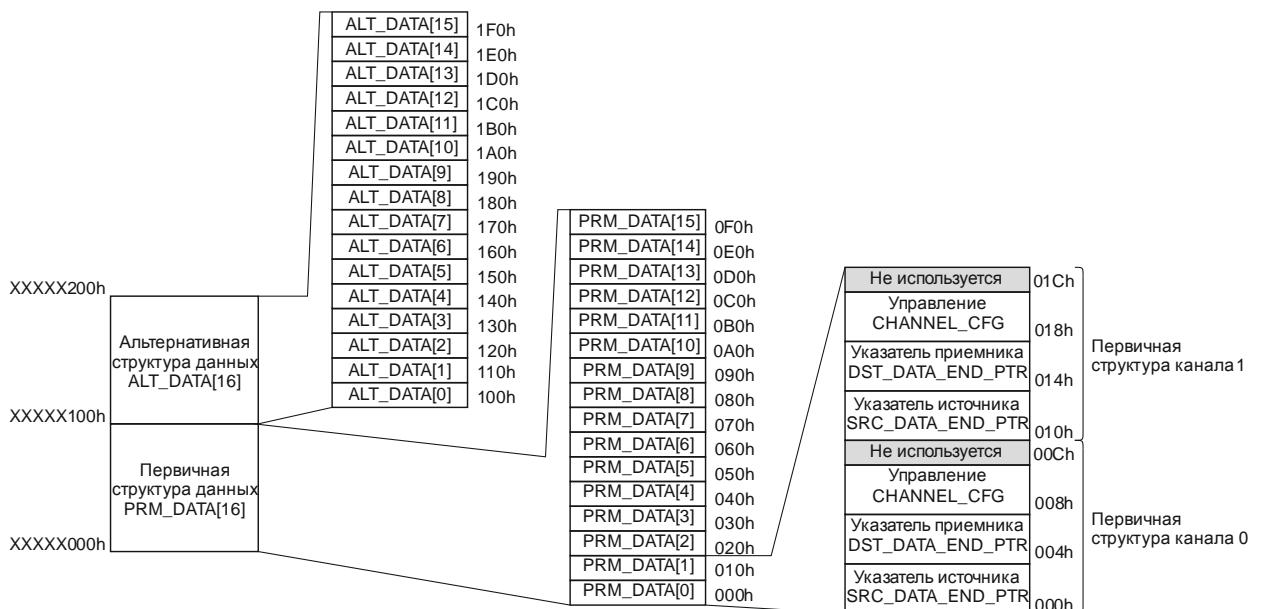

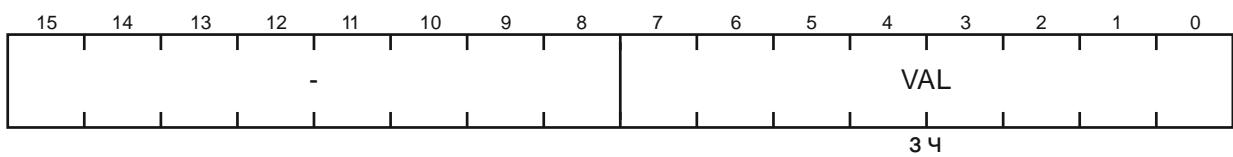

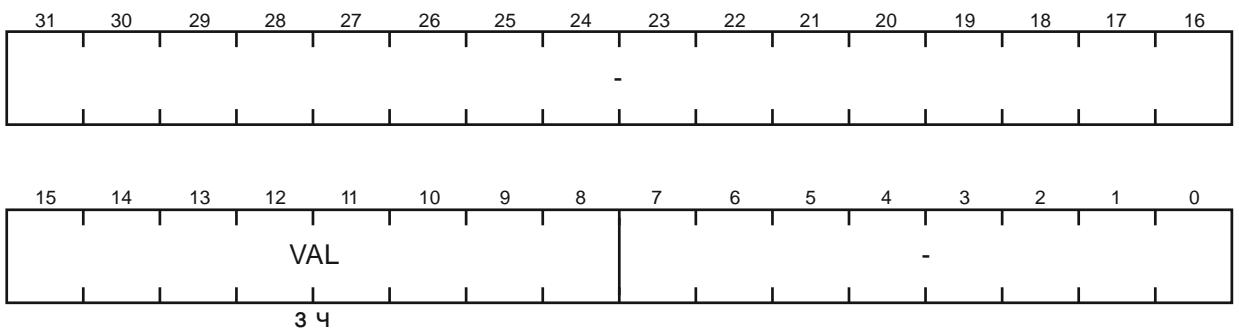

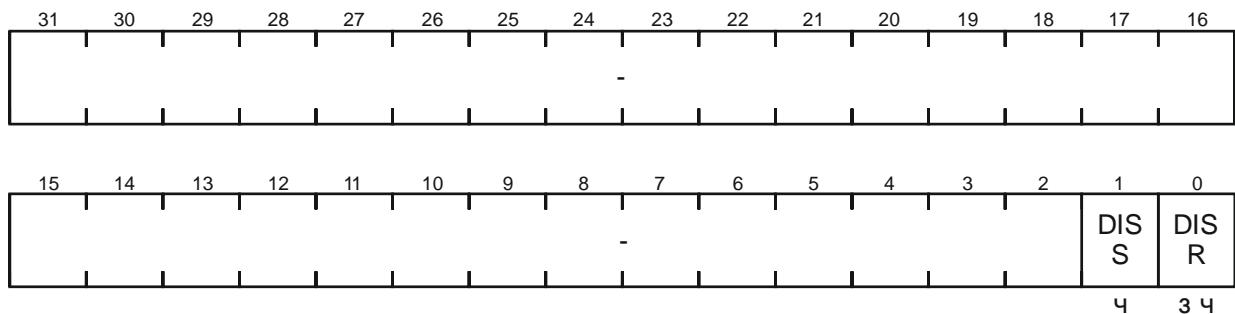

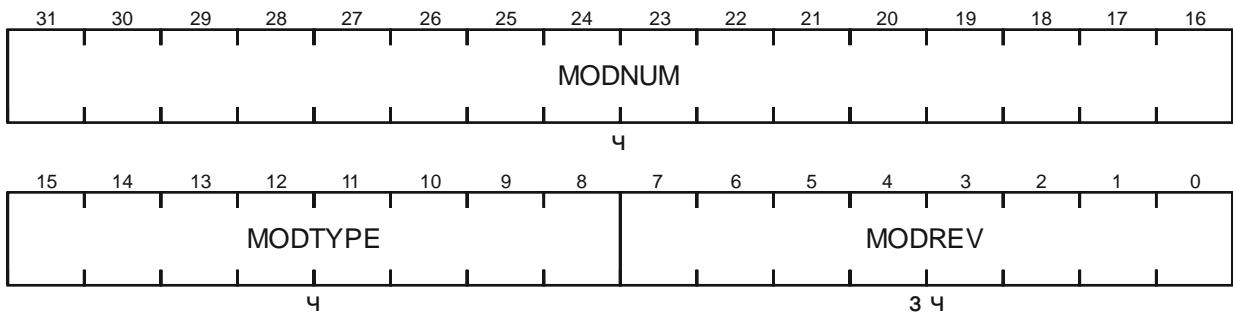

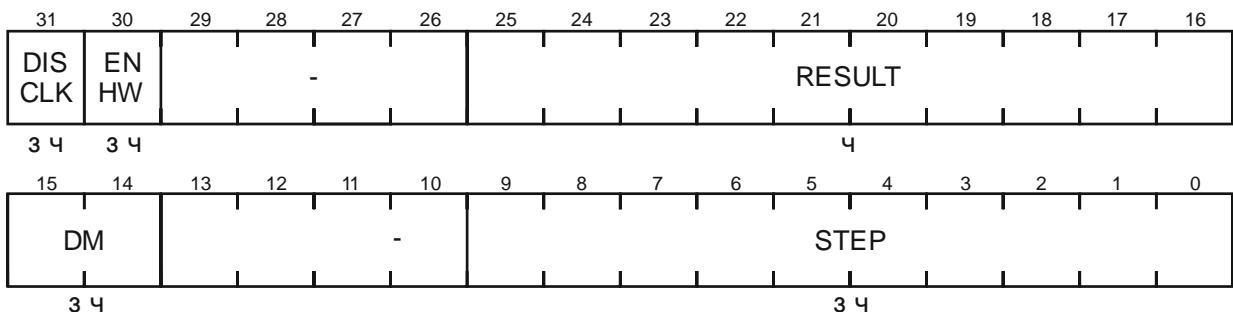

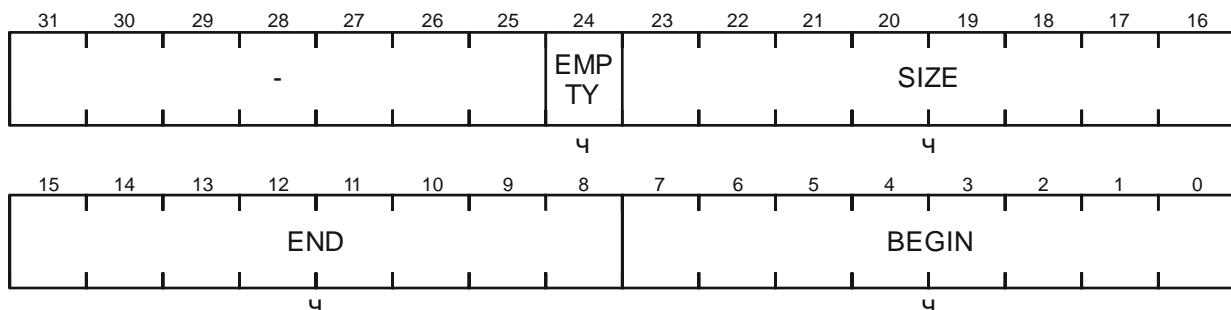

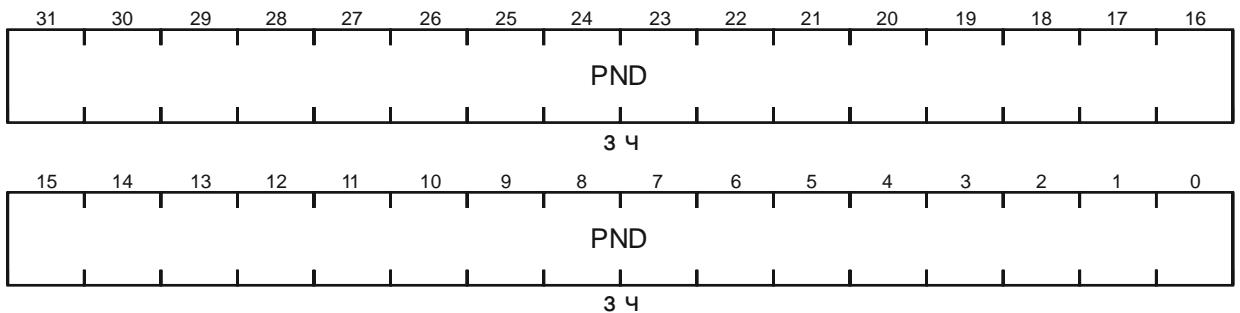

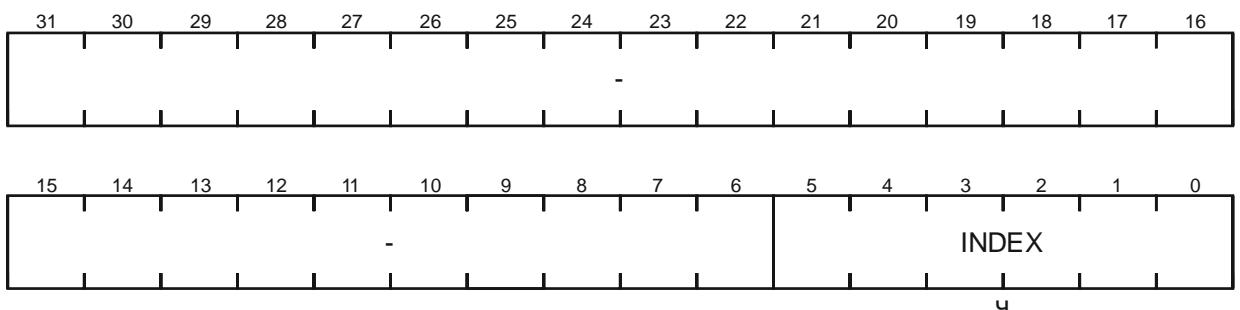

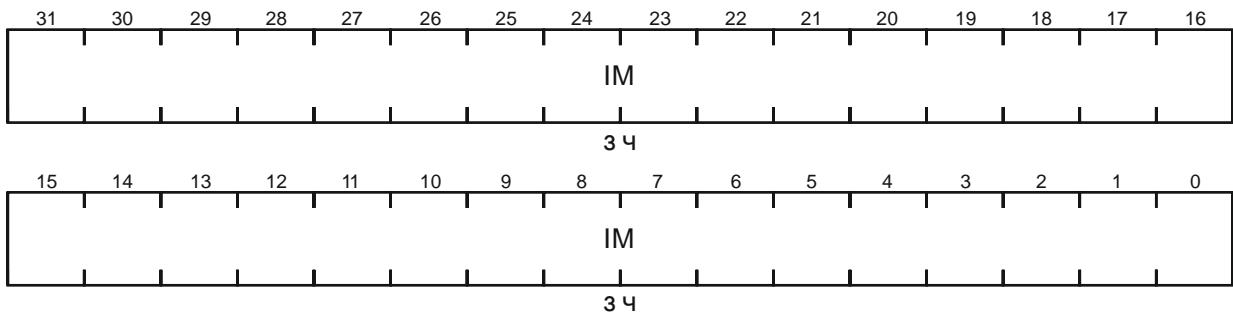

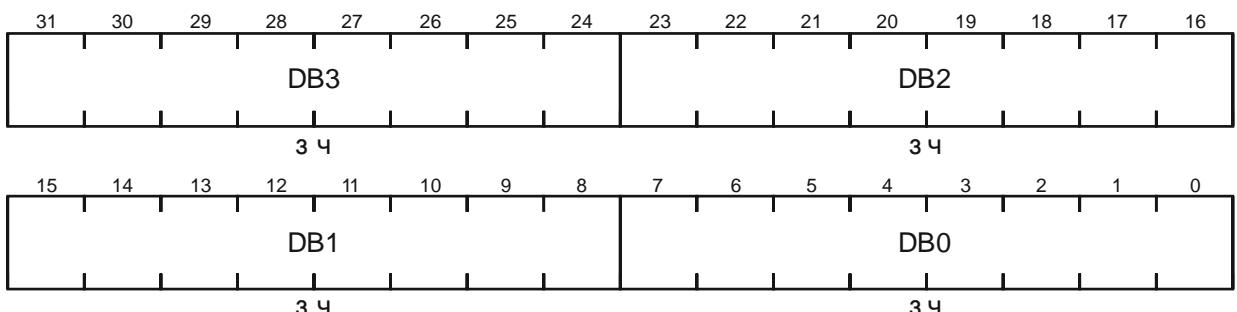

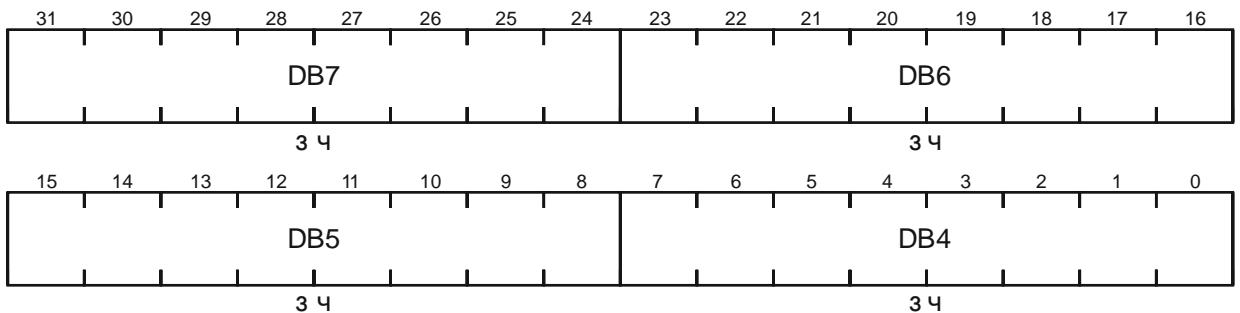

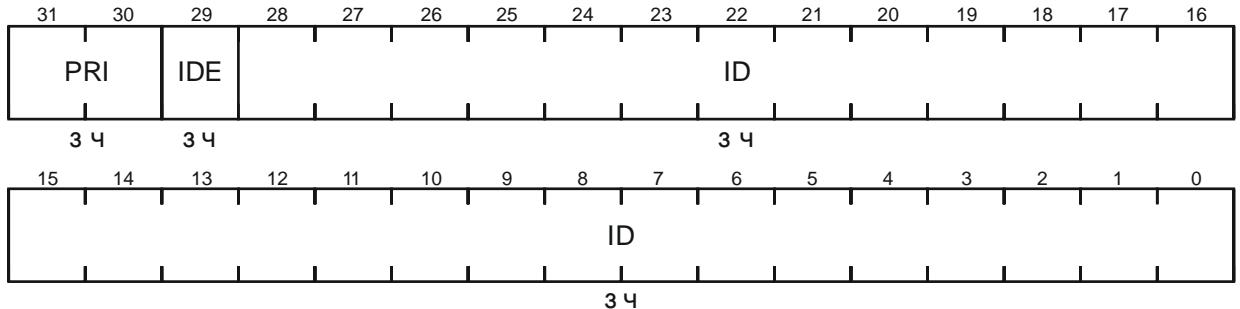

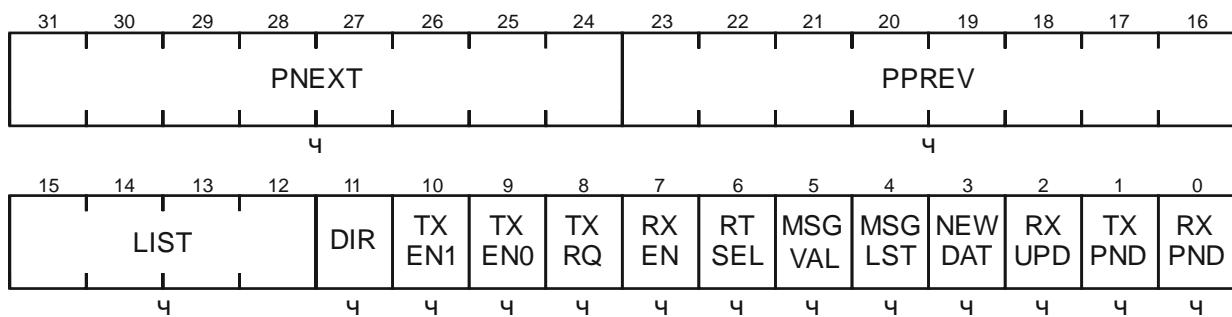

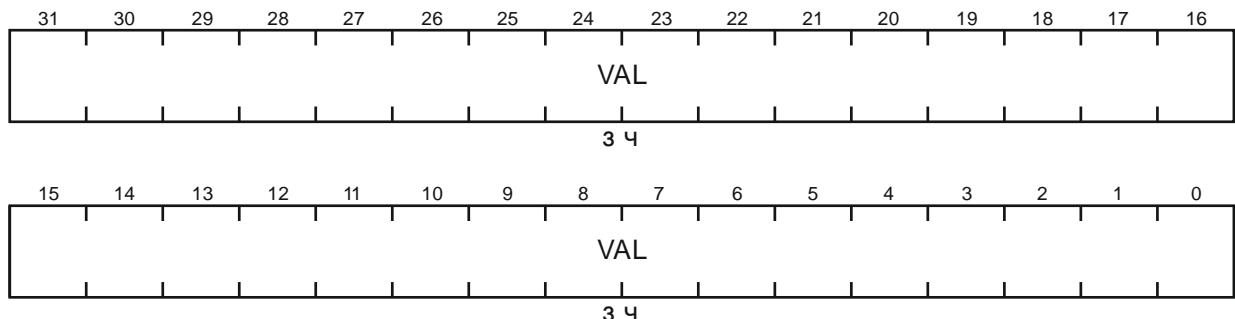

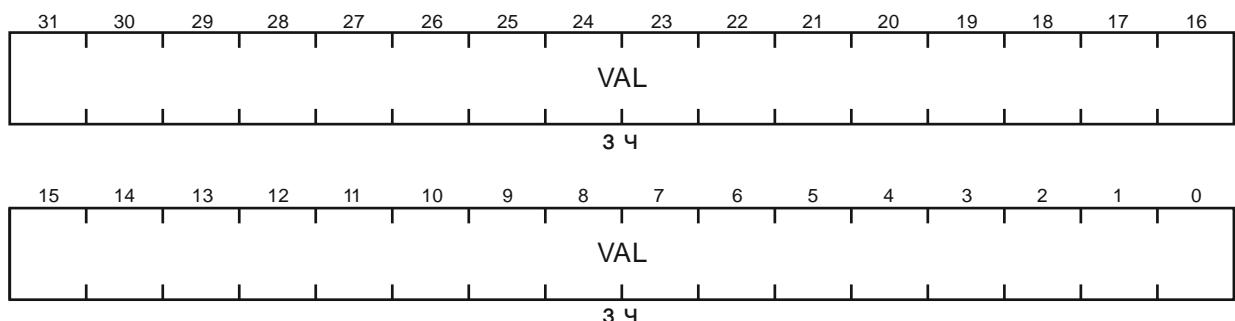

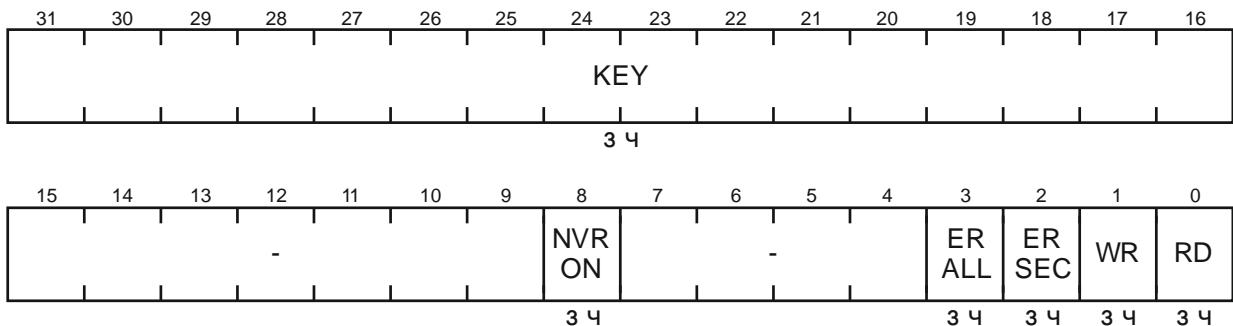

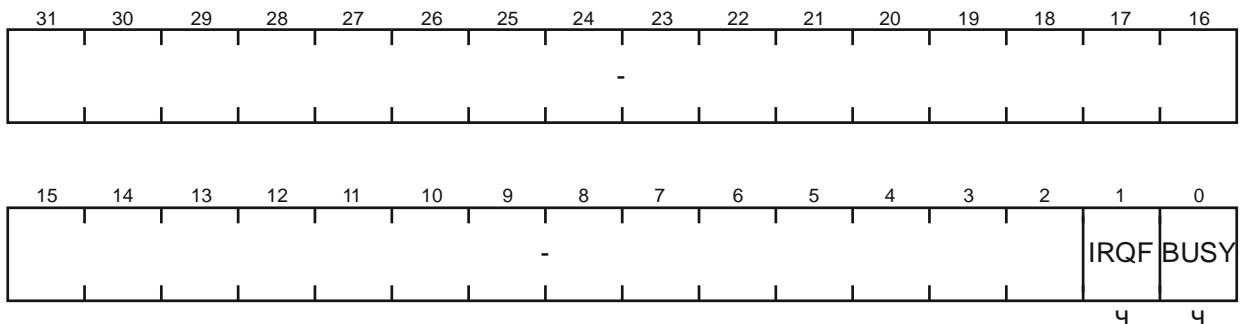

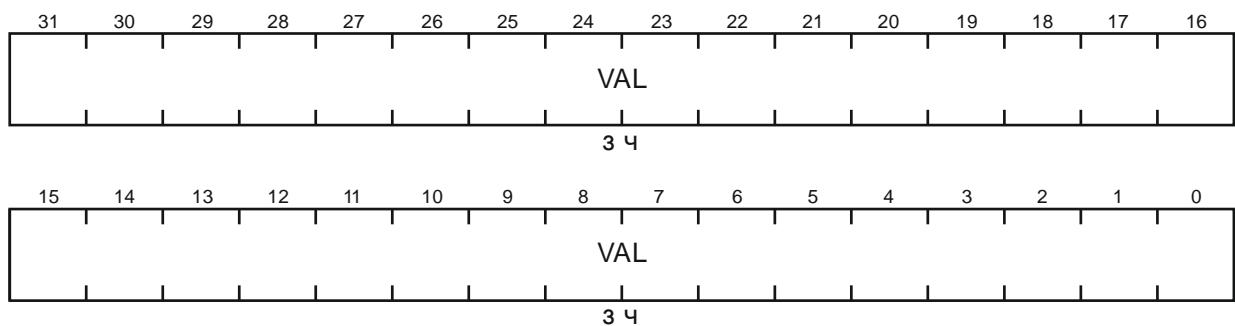

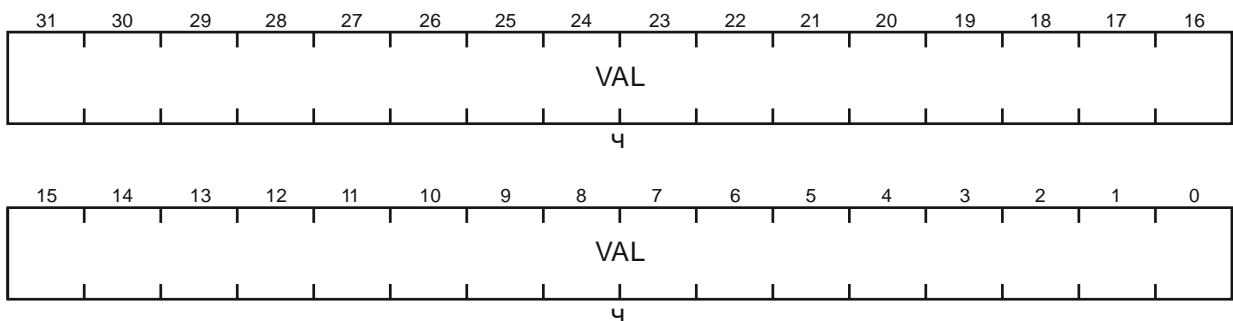

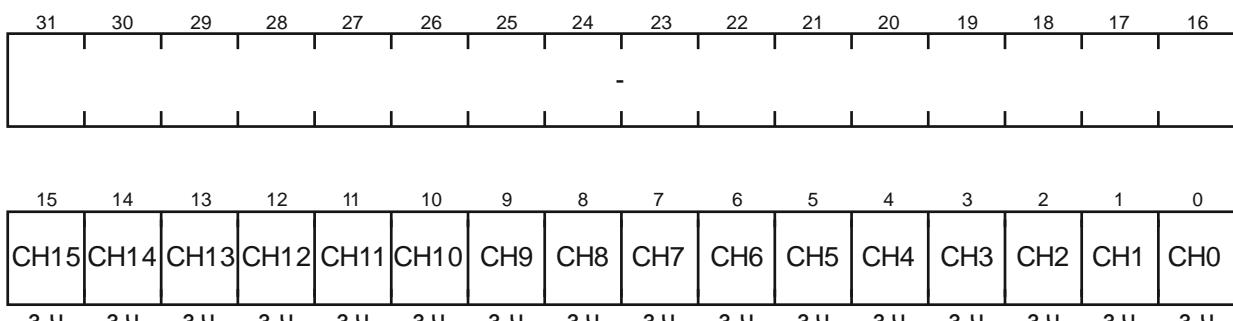

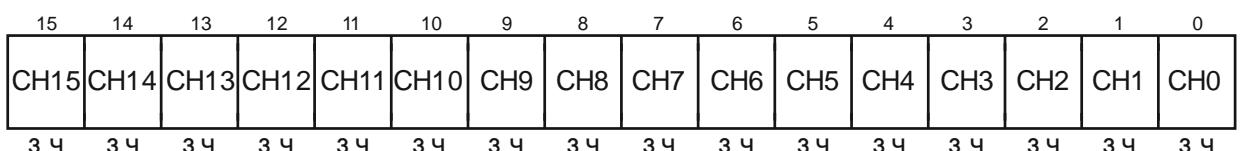

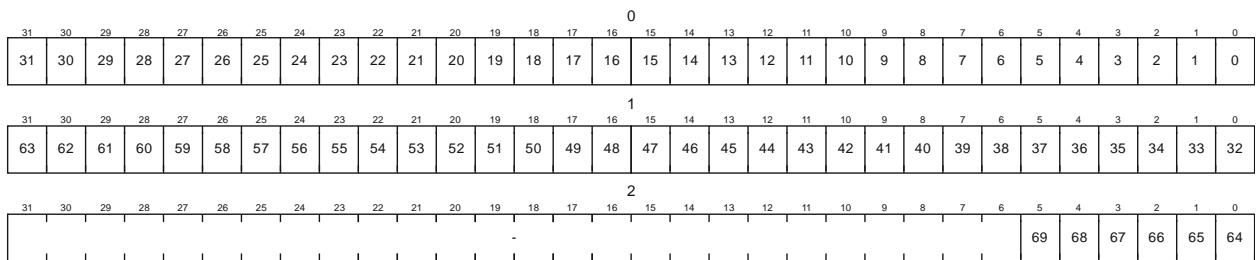

Каждому каналу контроллера DMA соответствуют две структуры управляющих данных: первичная и альтернативная. В ОЗУ должна быть отведена область для хранения этих структур.

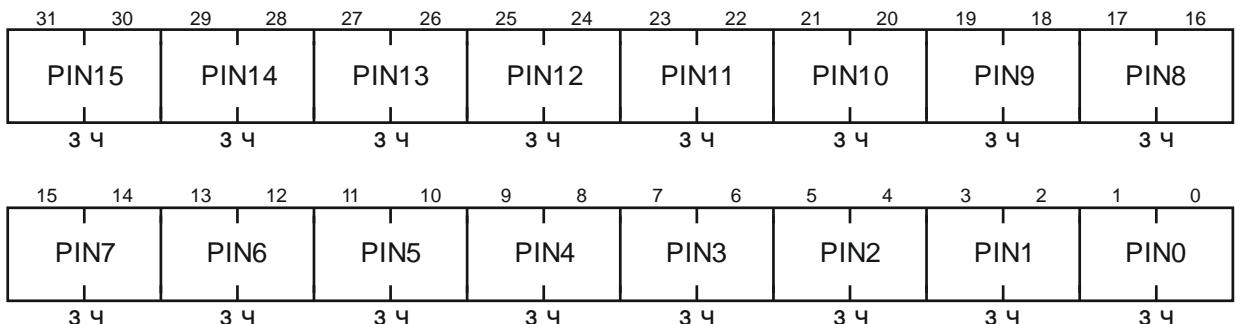

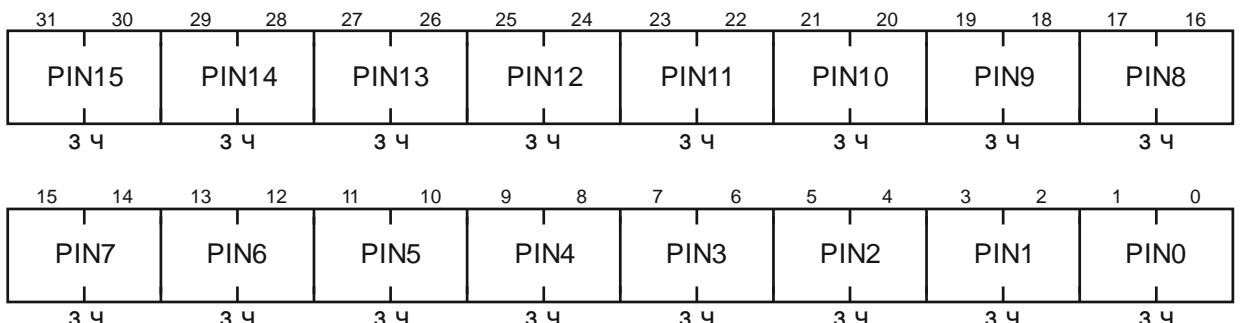

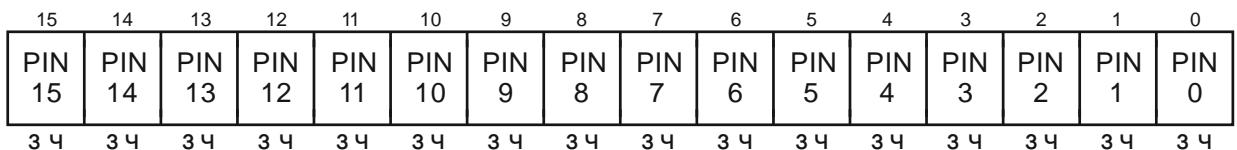

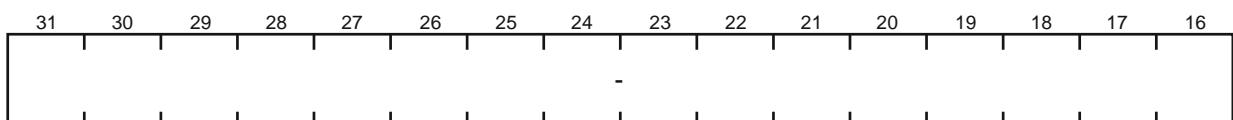

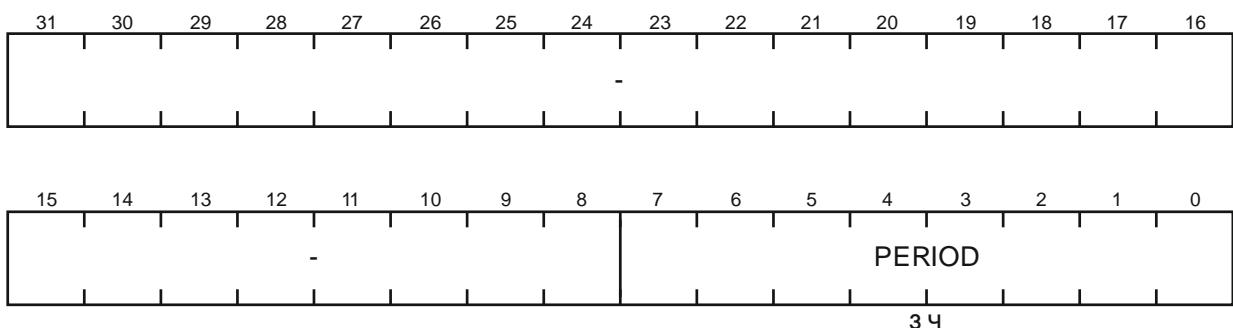

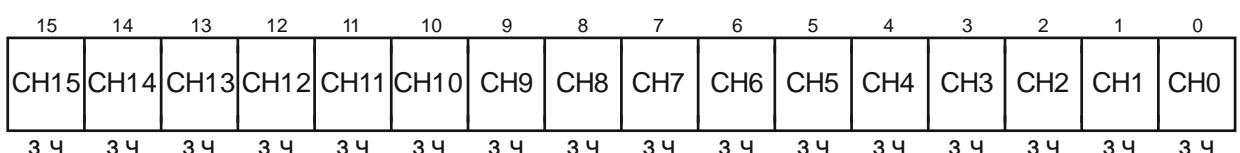

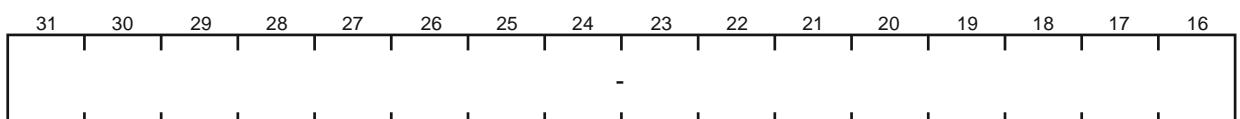

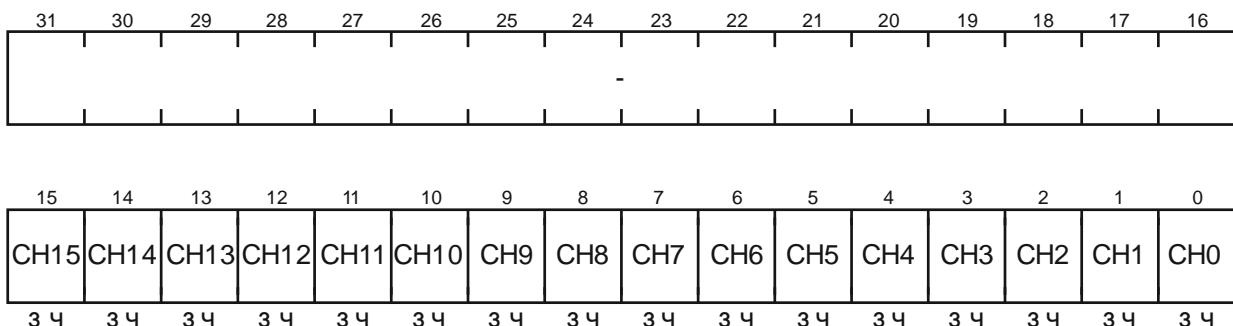

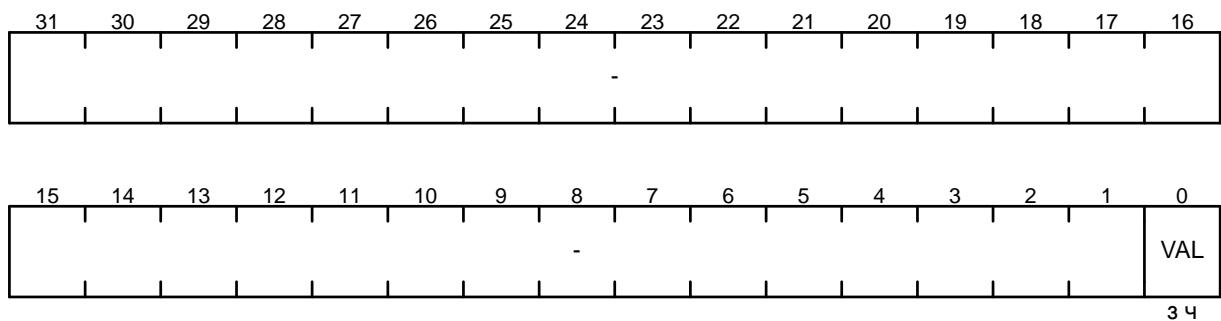

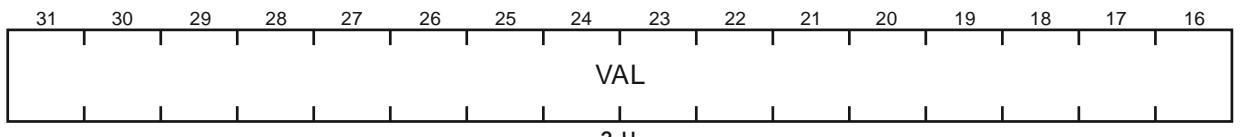

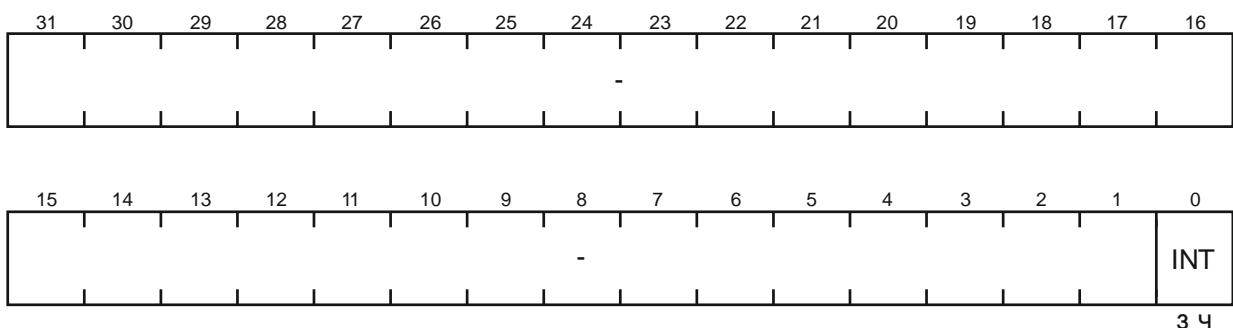

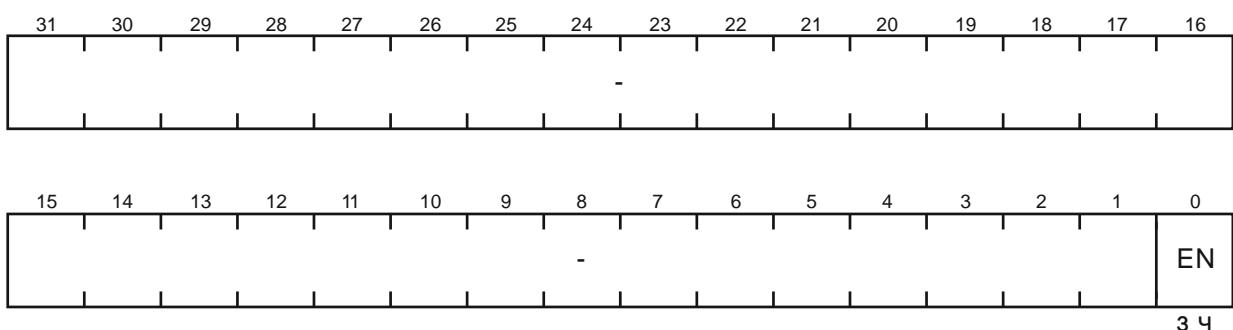

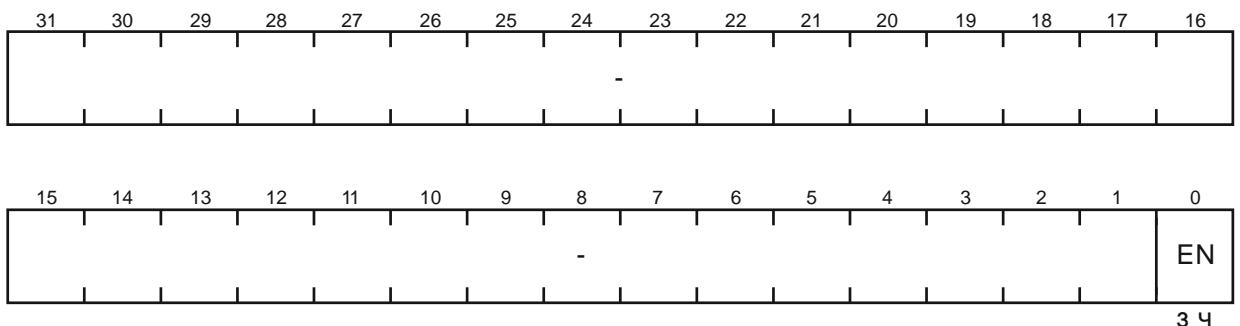

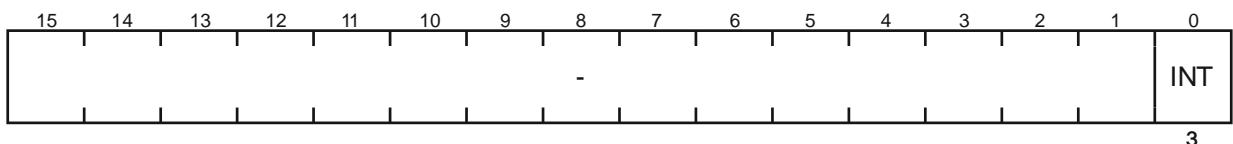

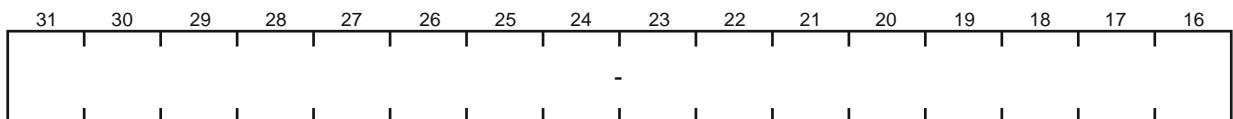

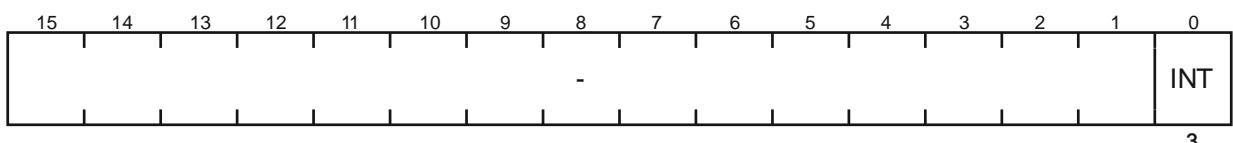

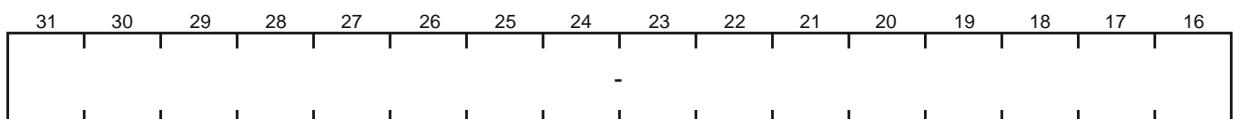

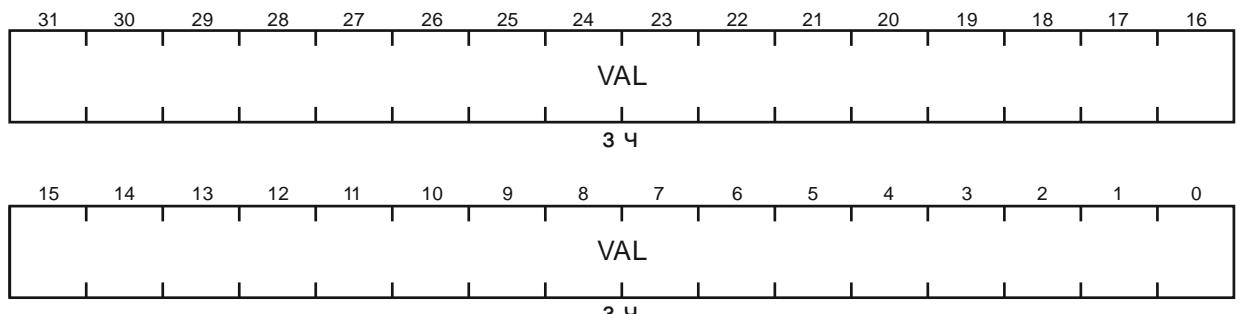

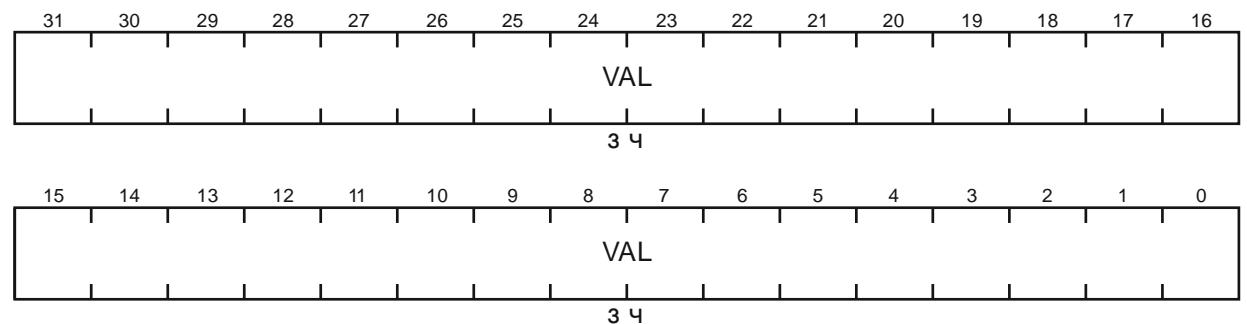

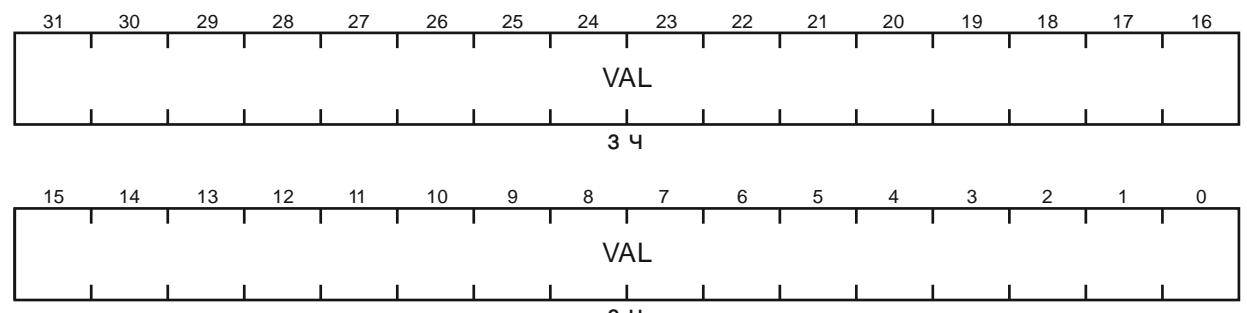

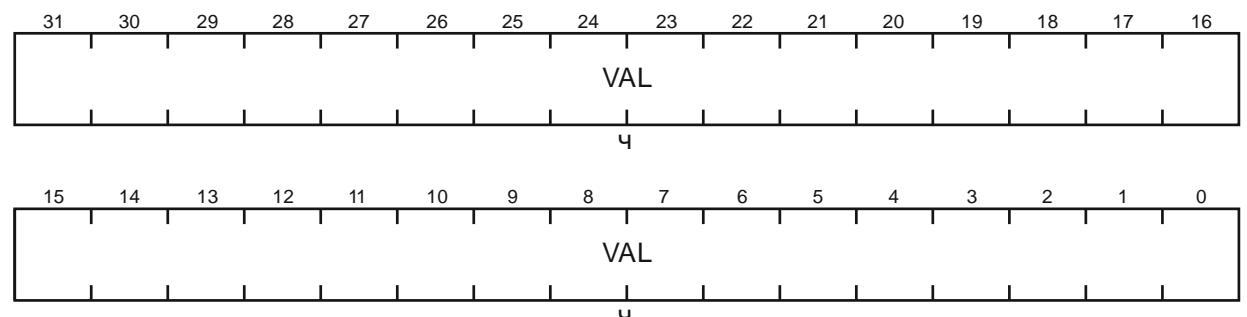

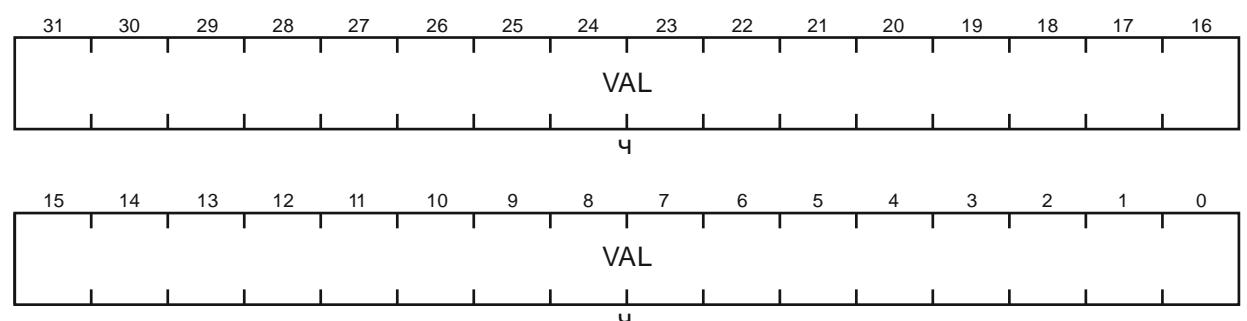

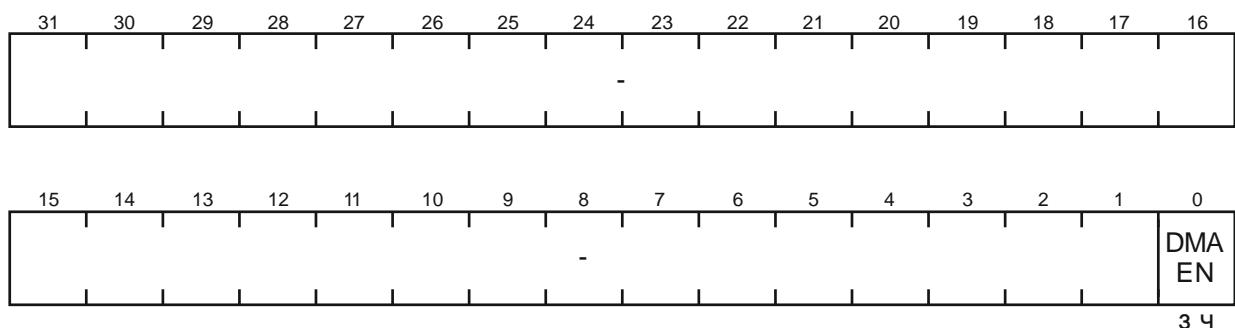

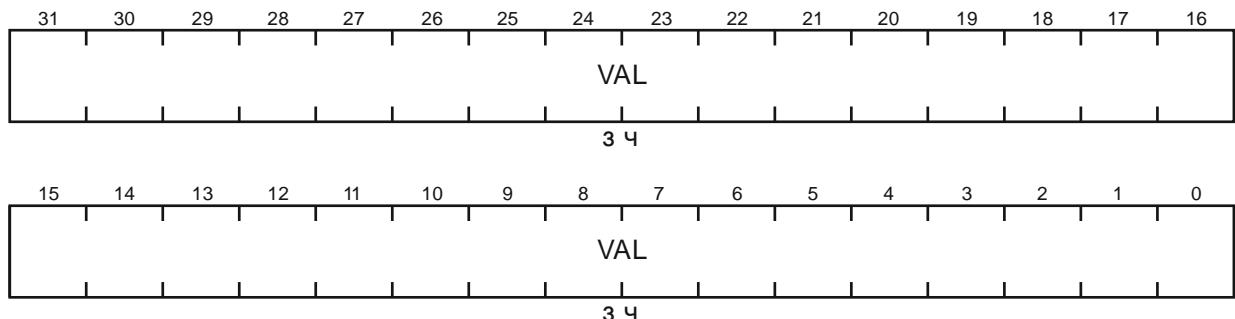

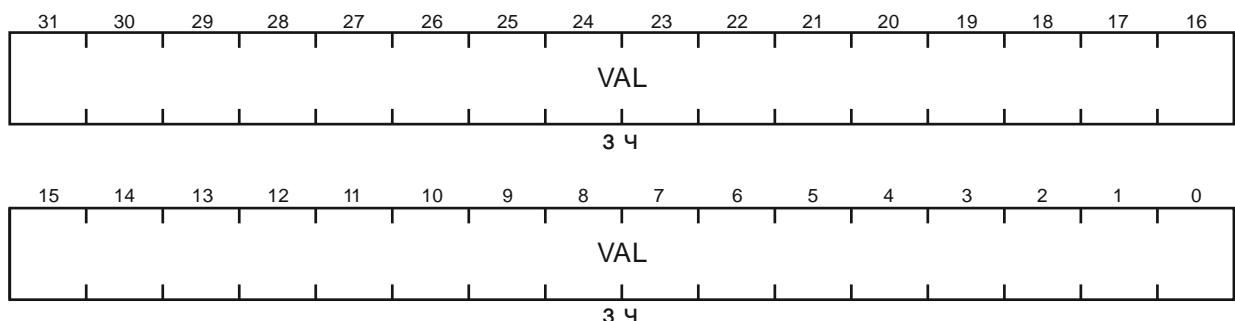

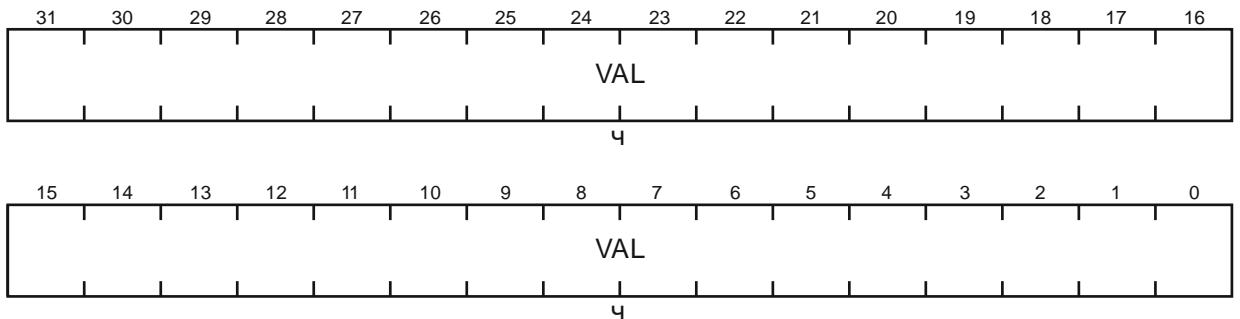

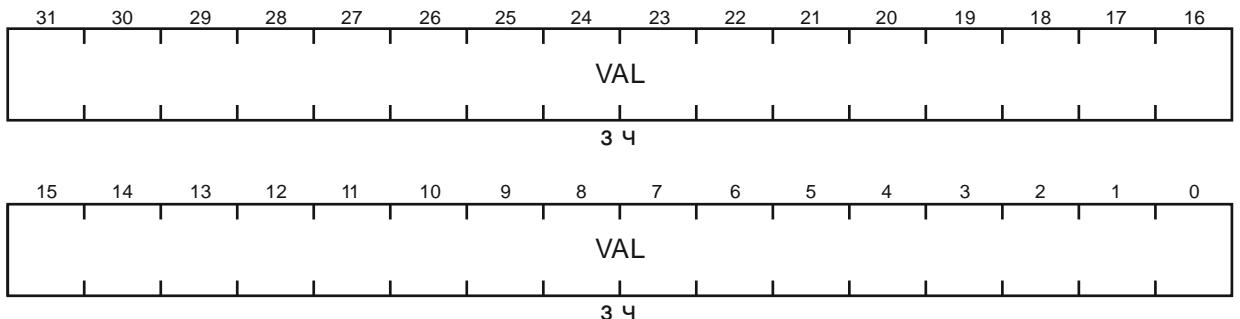

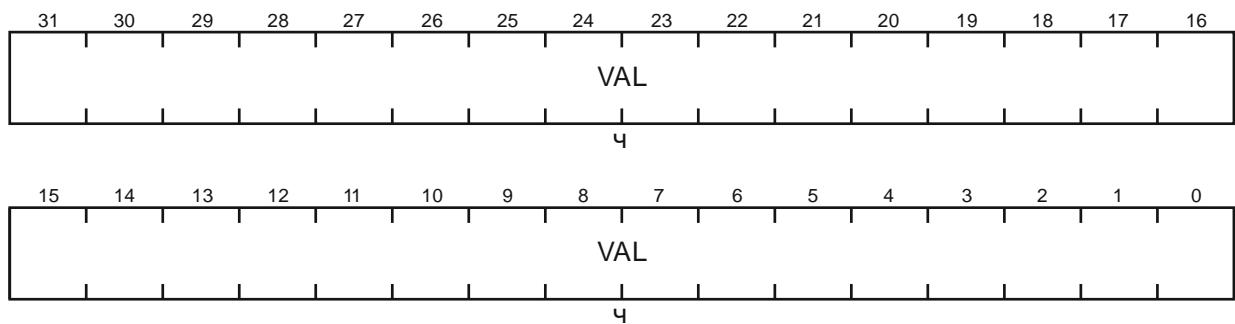

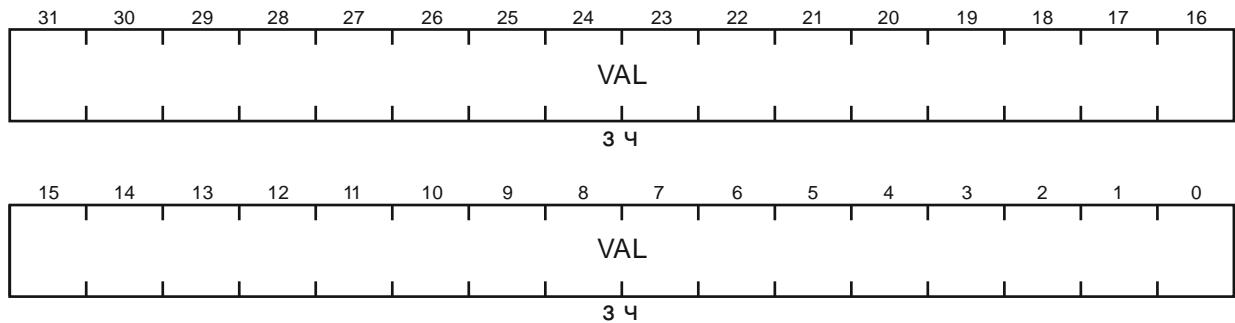

На рисунке 8.1 показана область памяти, необходимая контроллеру для структур управляющих данных каналов, при использовании всех 16 каналов и optionalной альтернативной структуры данных.

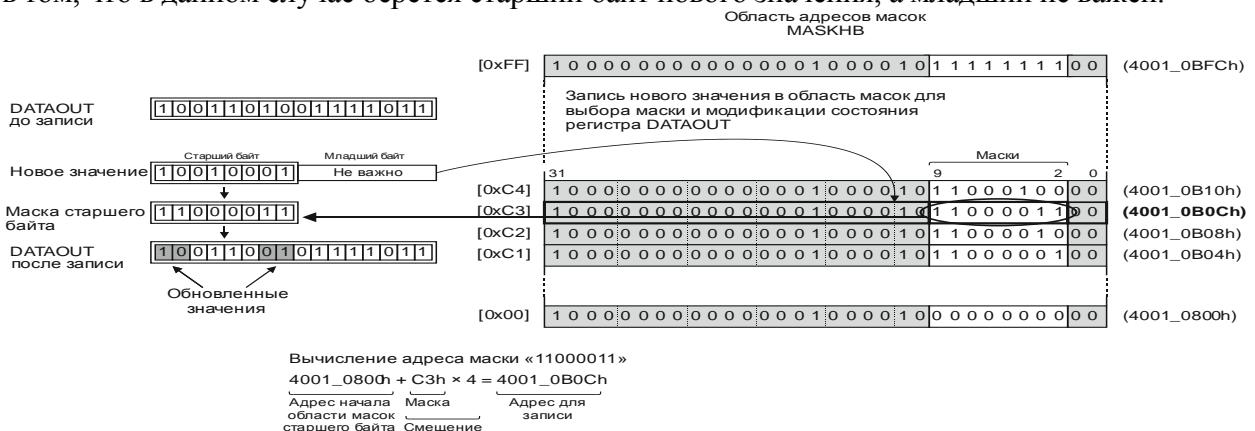

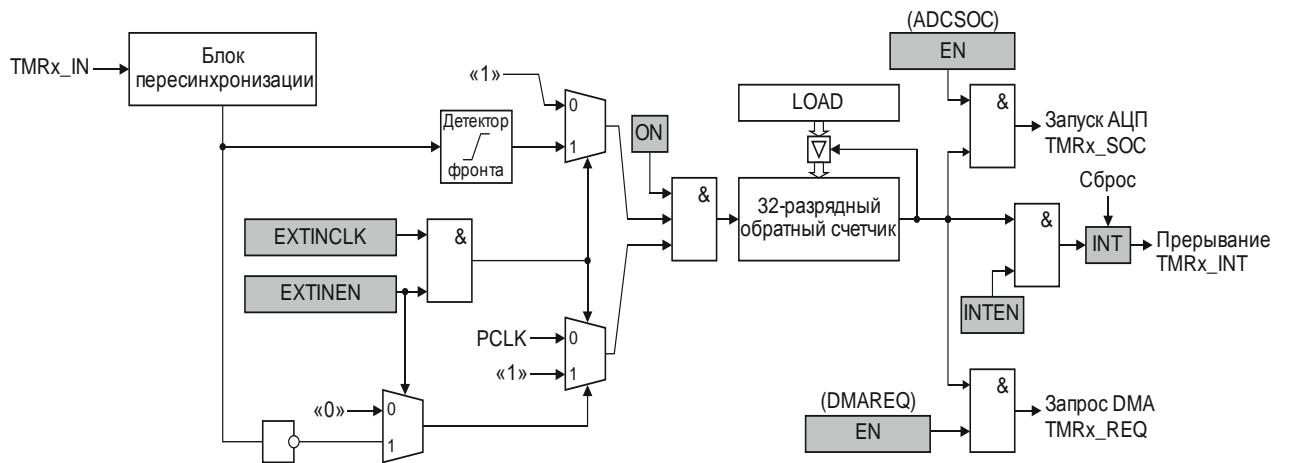

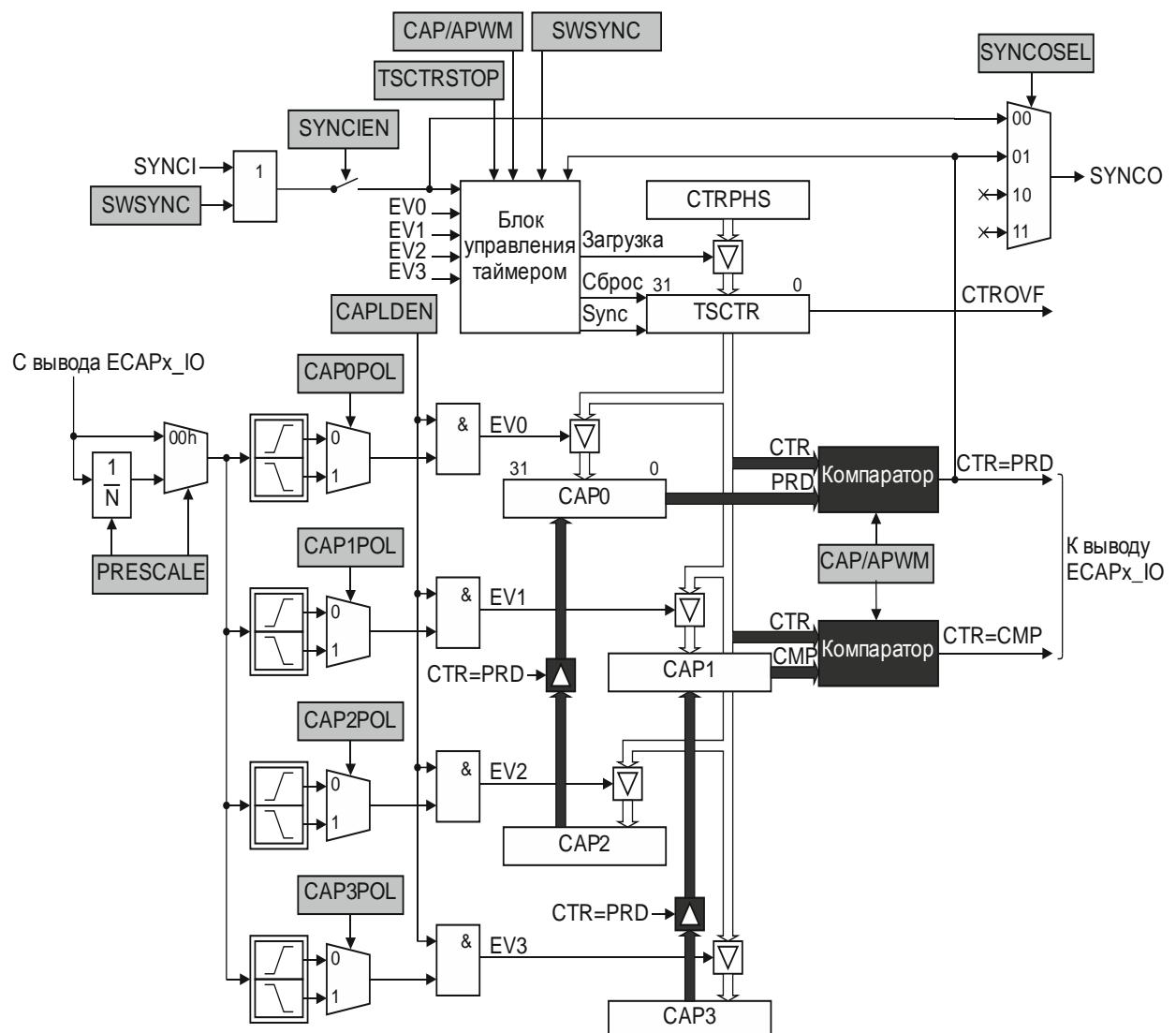

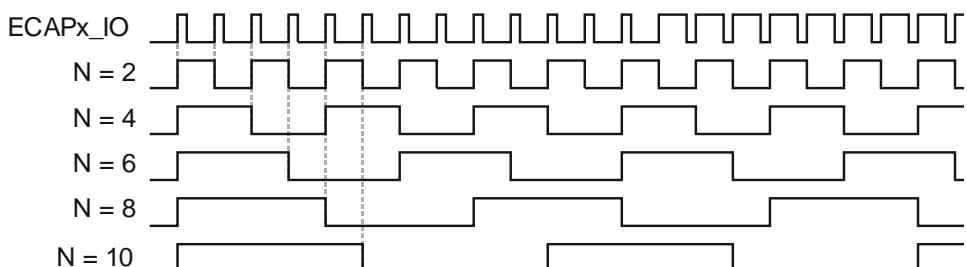

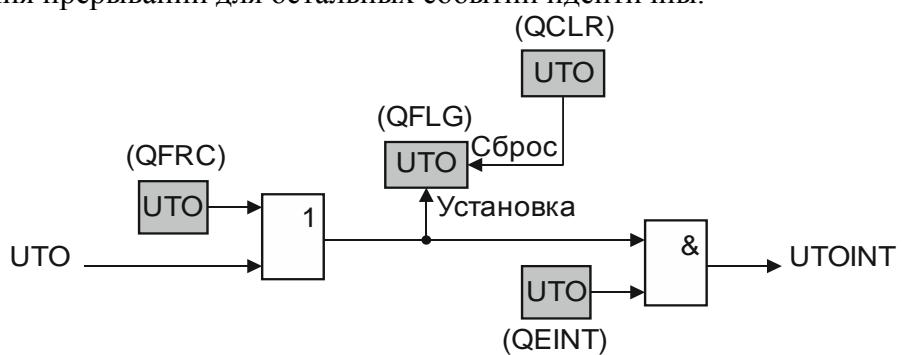

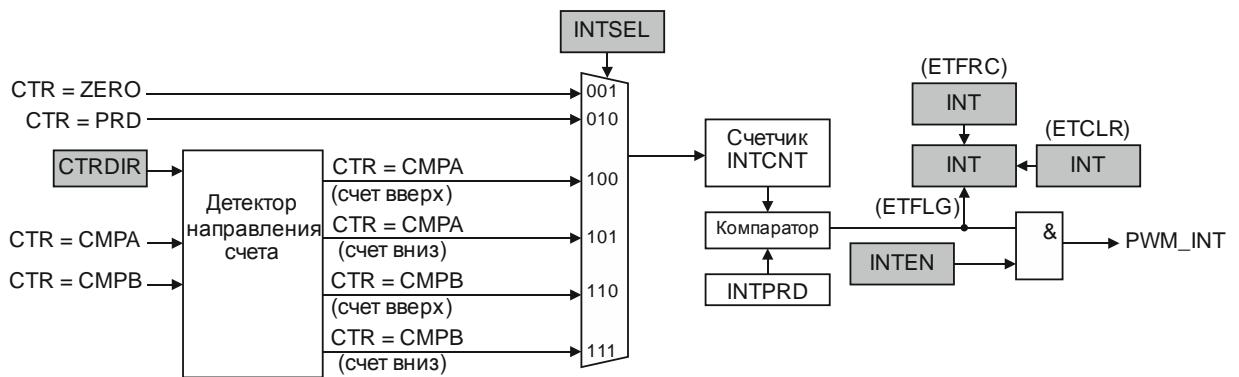

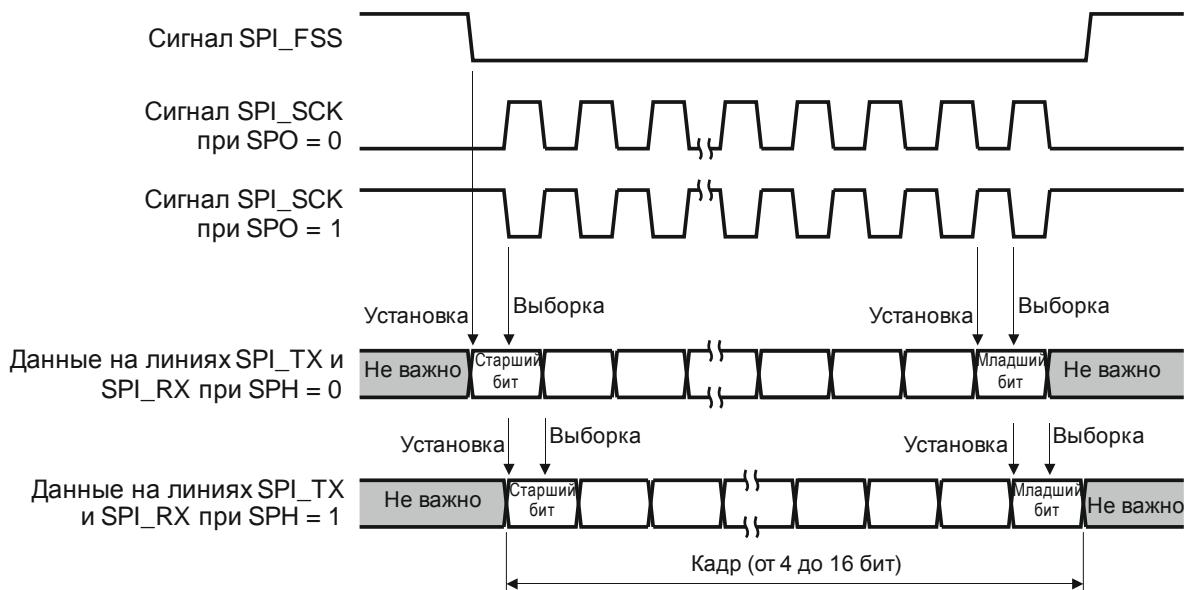

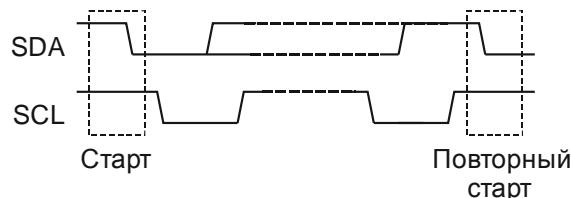

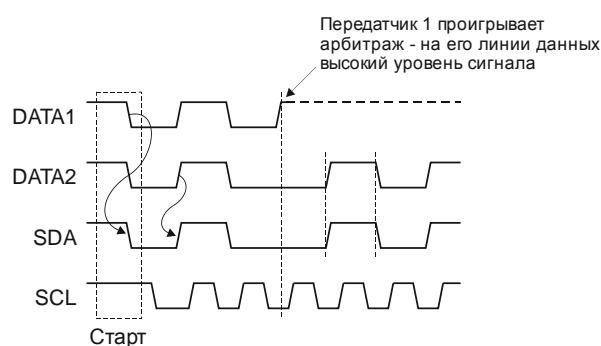

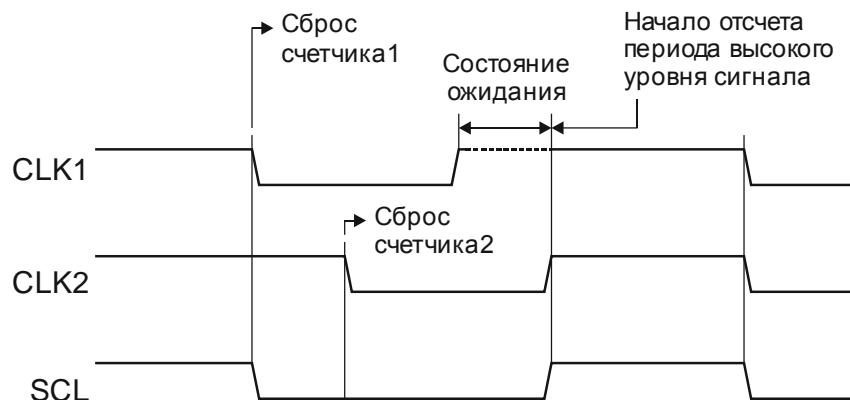

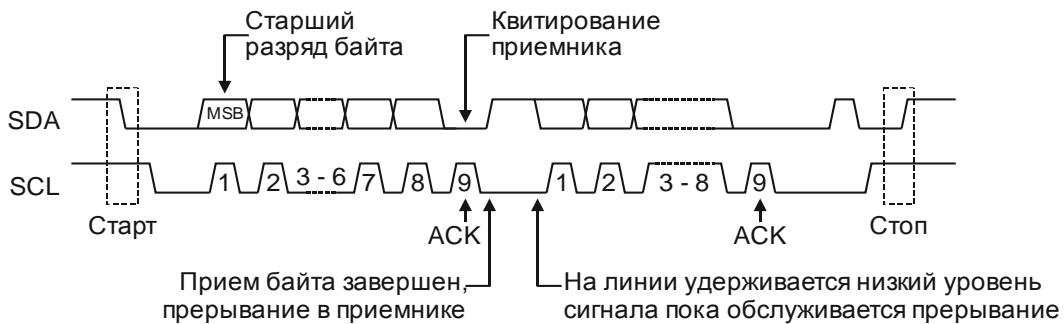

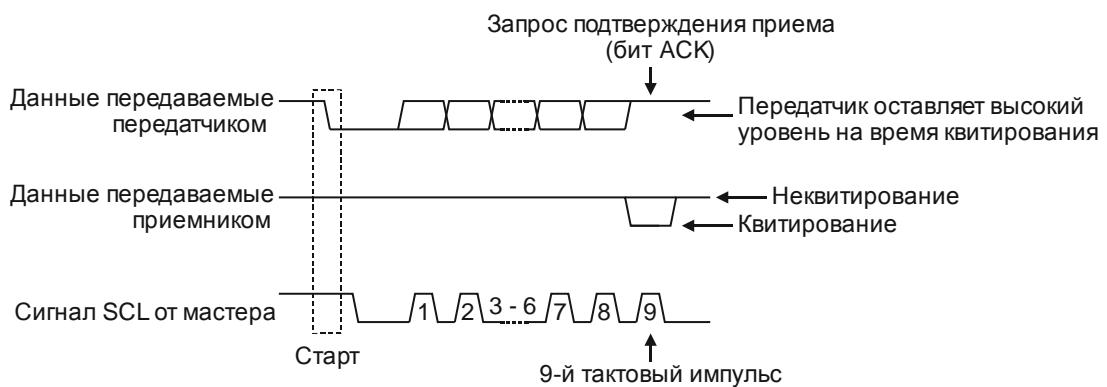

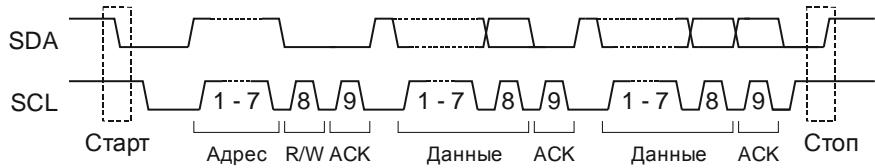

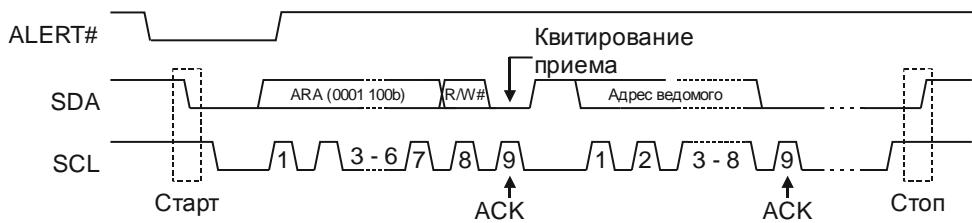

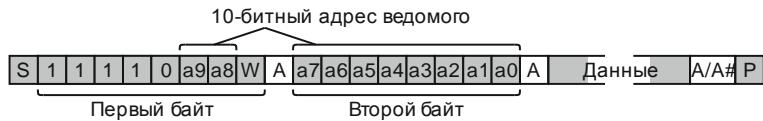

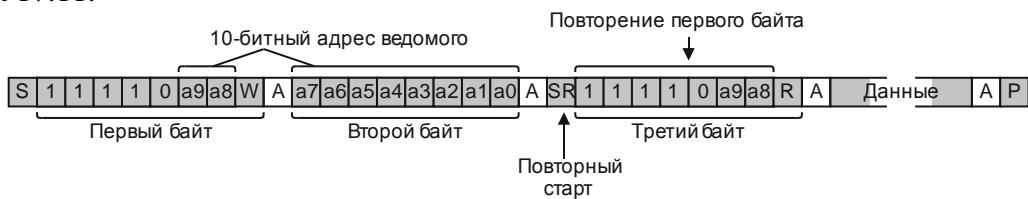

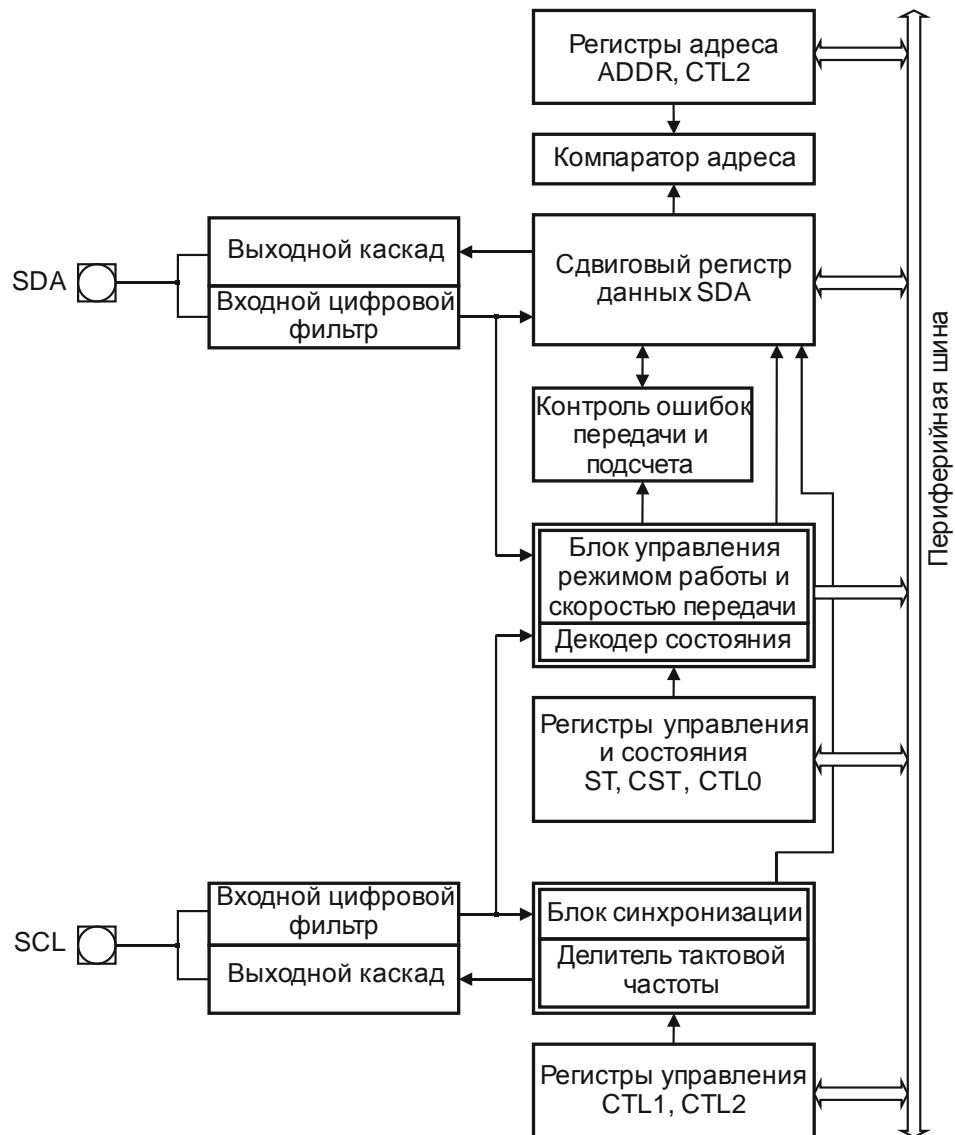

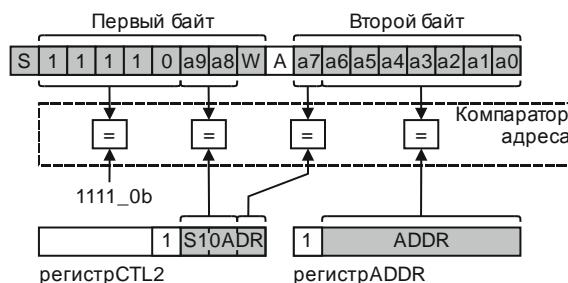

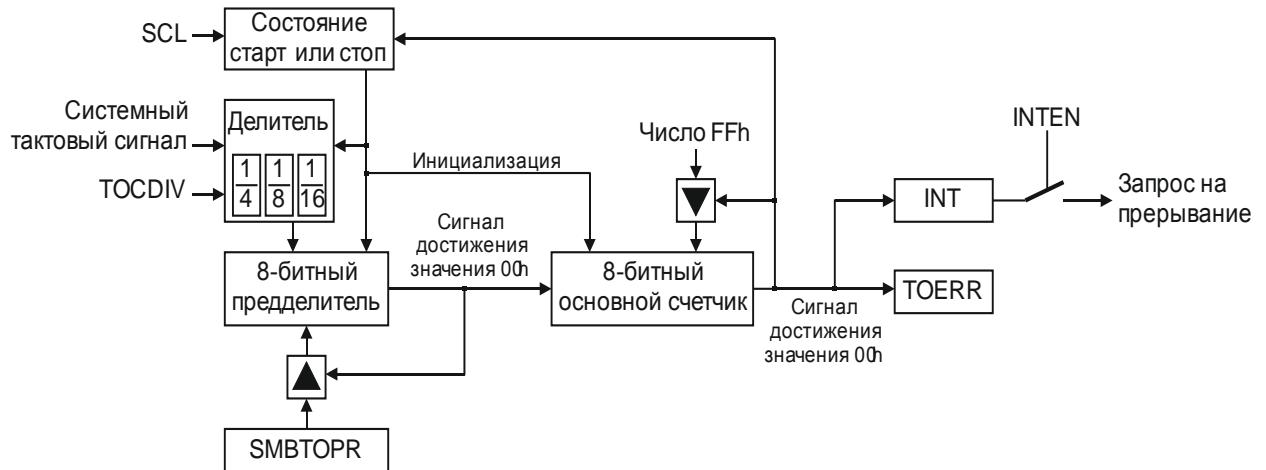

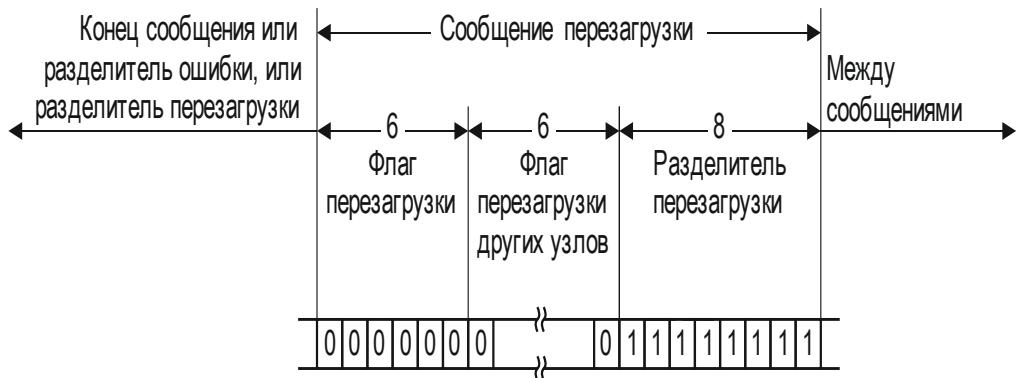

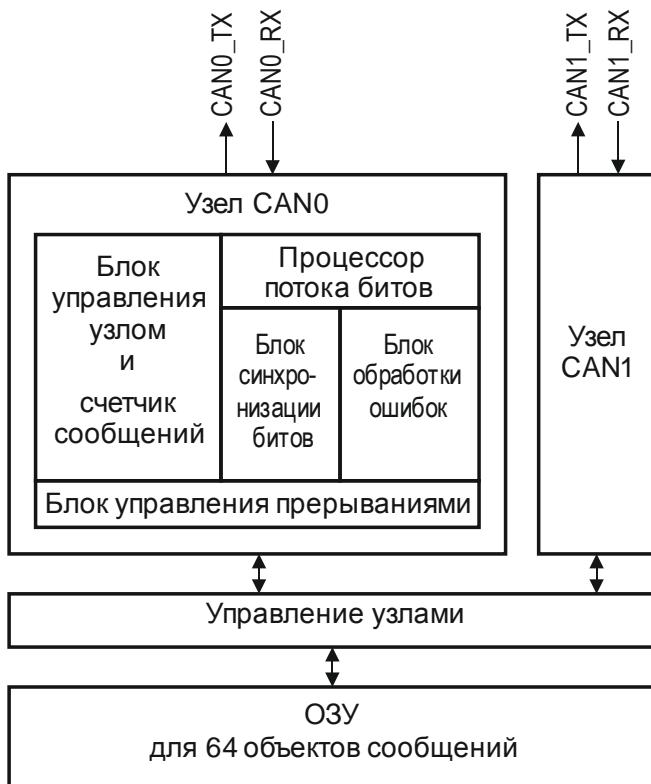

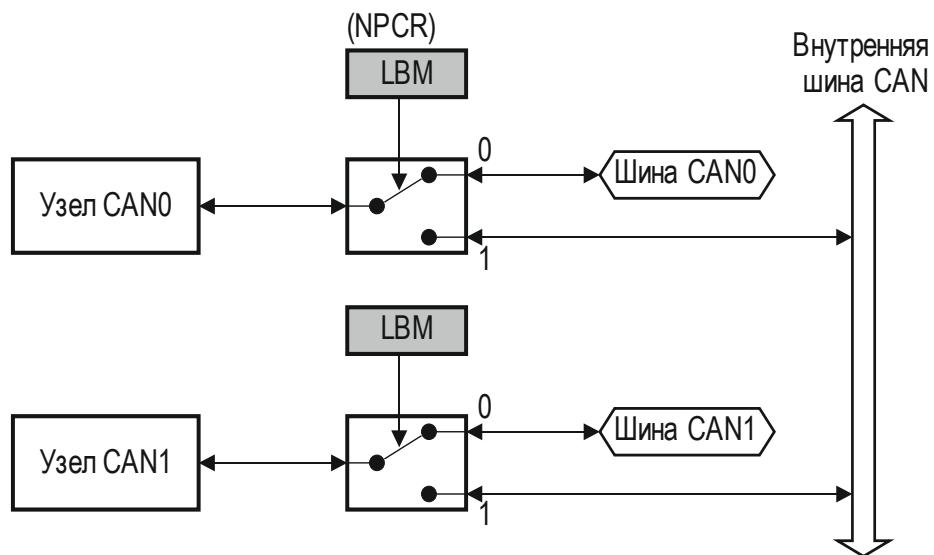

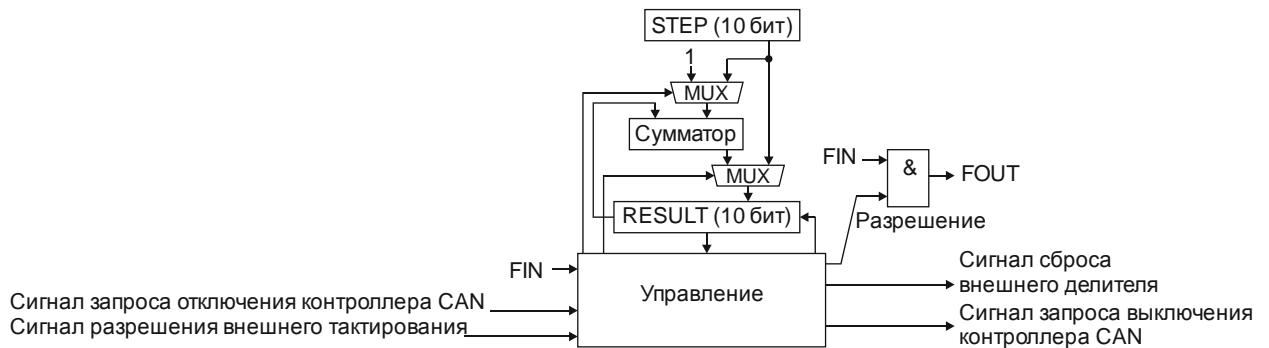

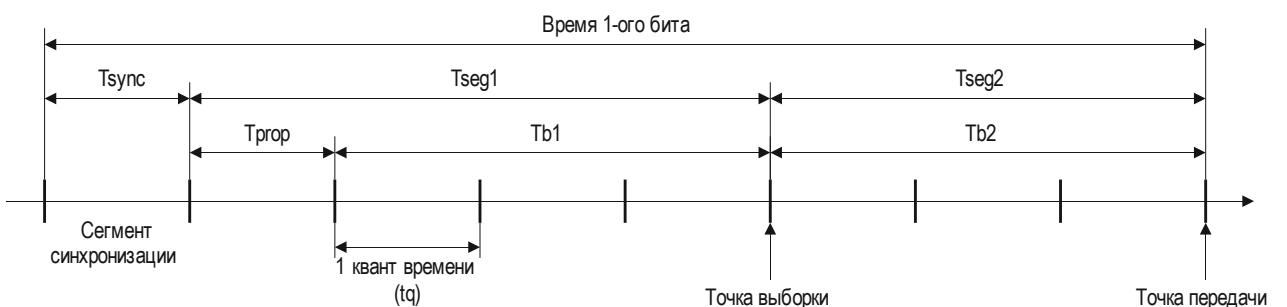

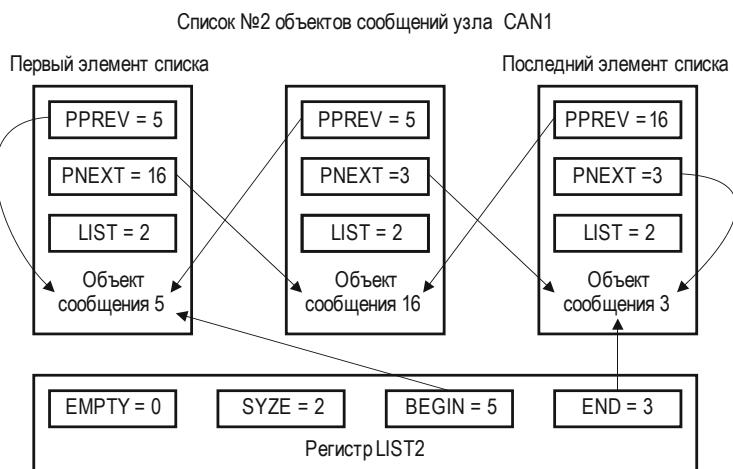

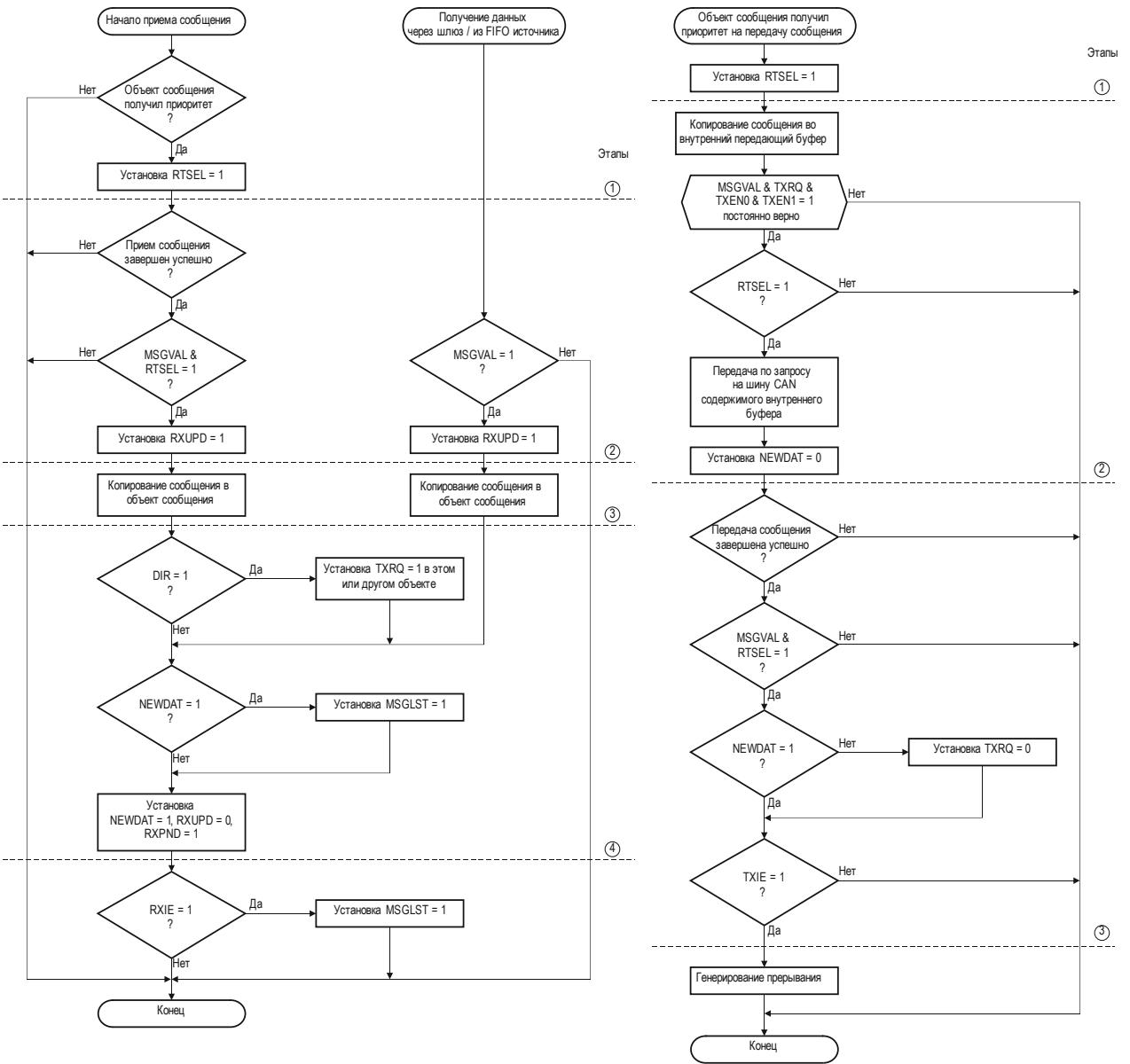

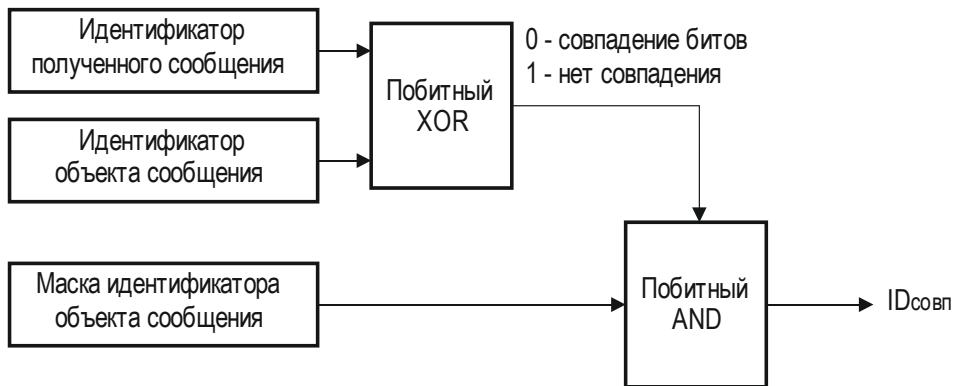

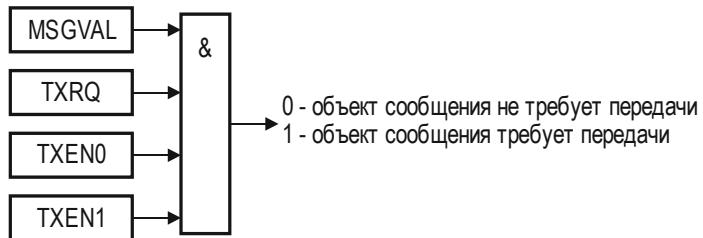

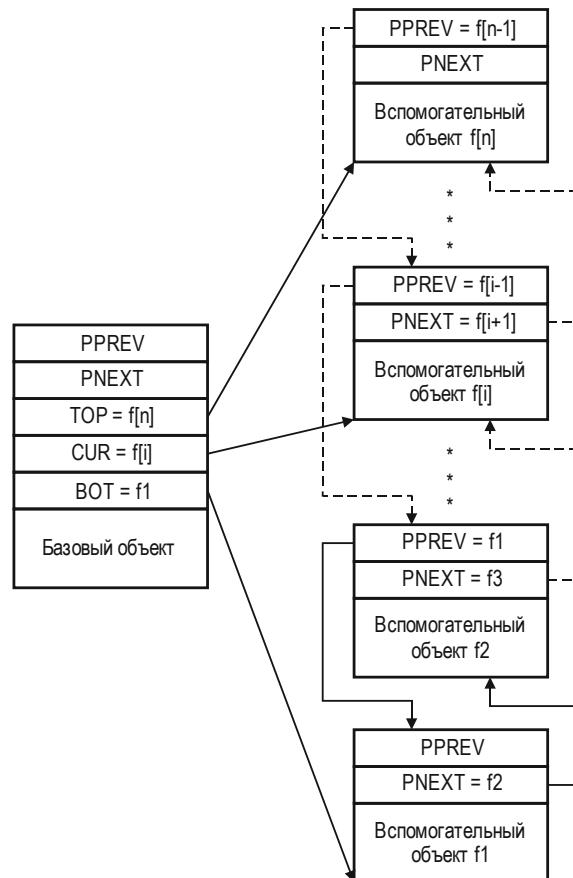

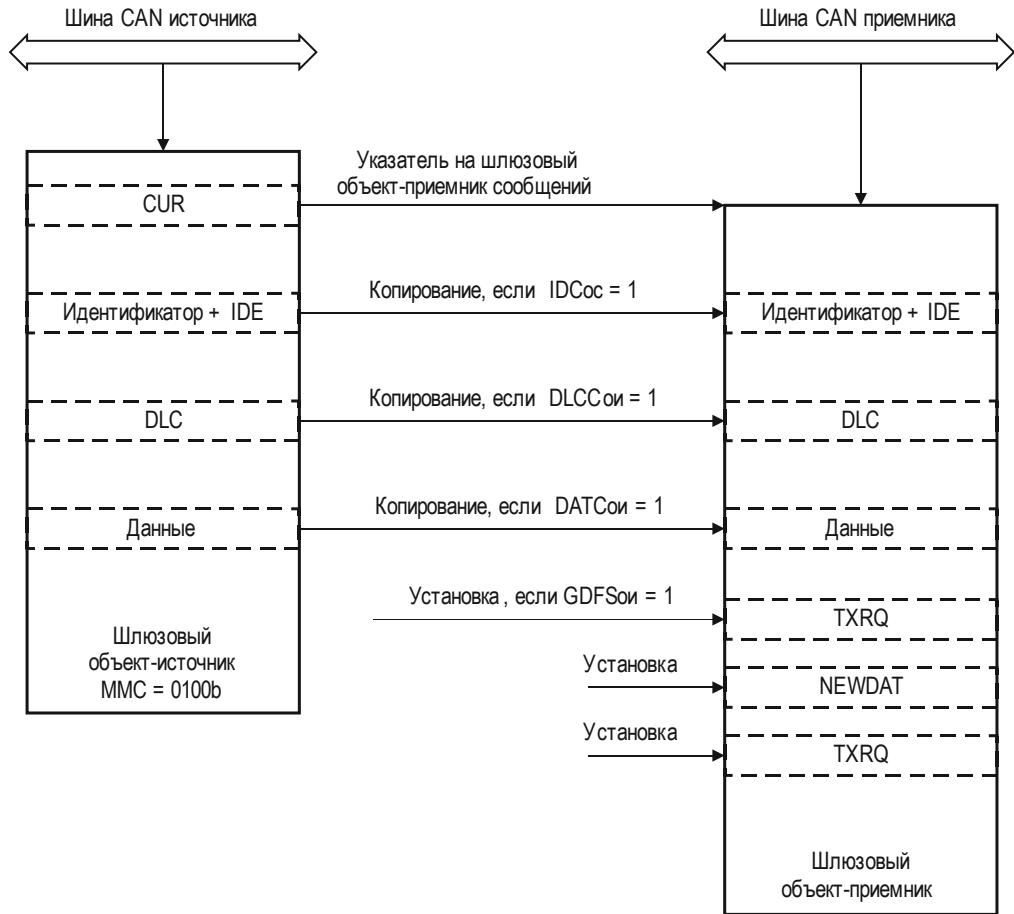

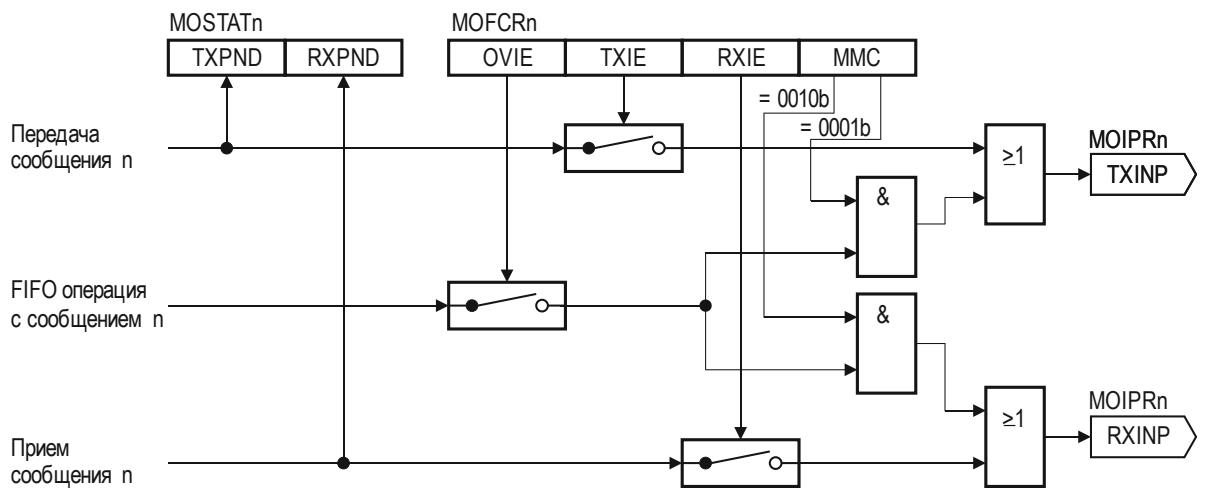

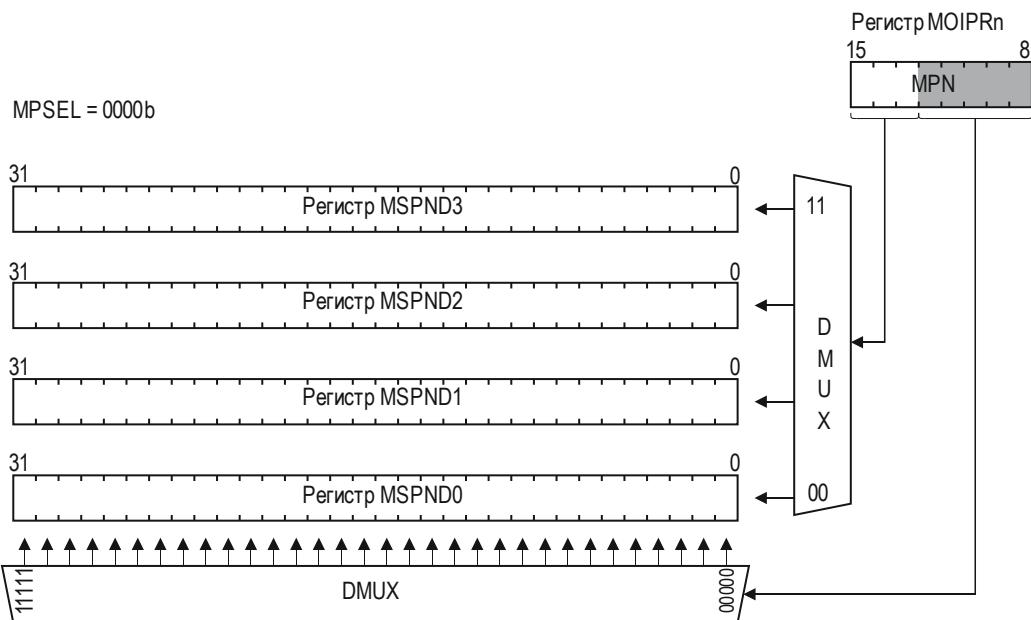

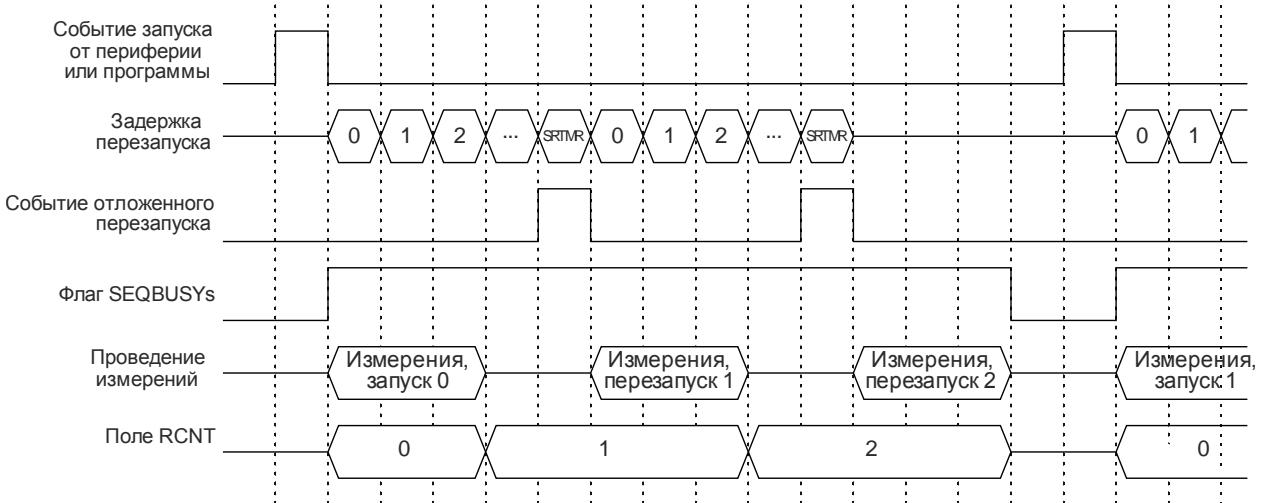

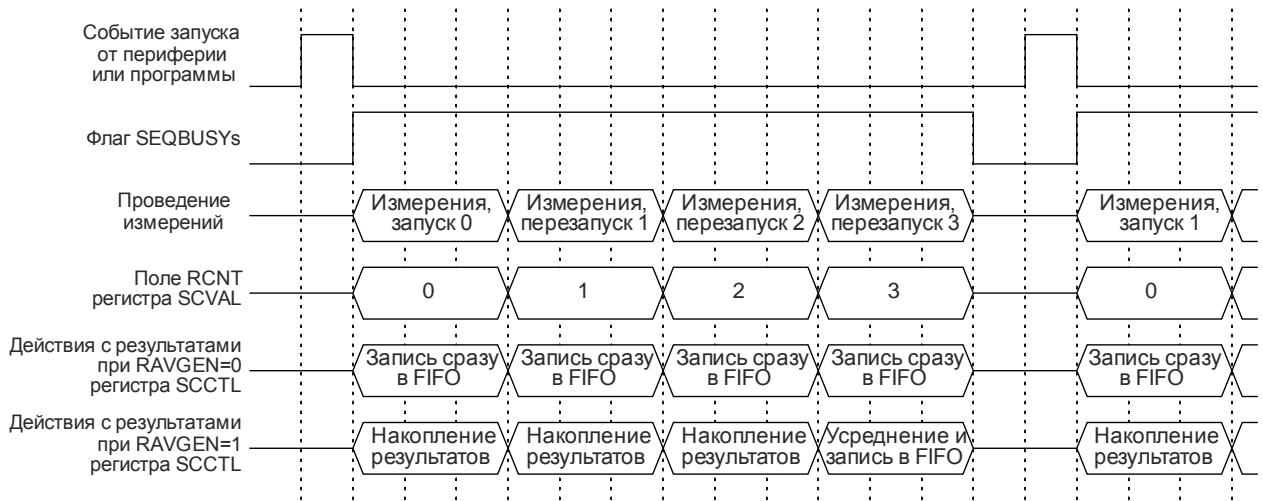

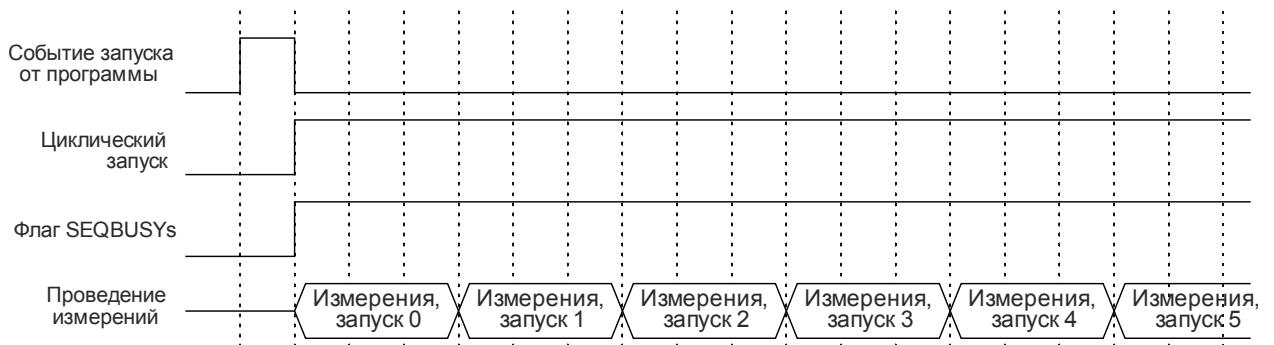

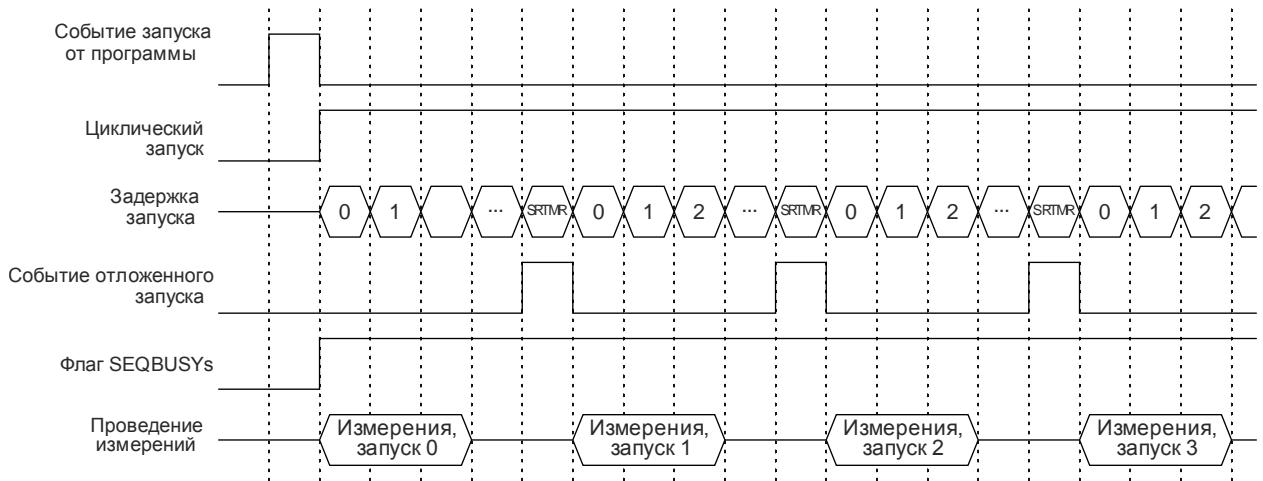

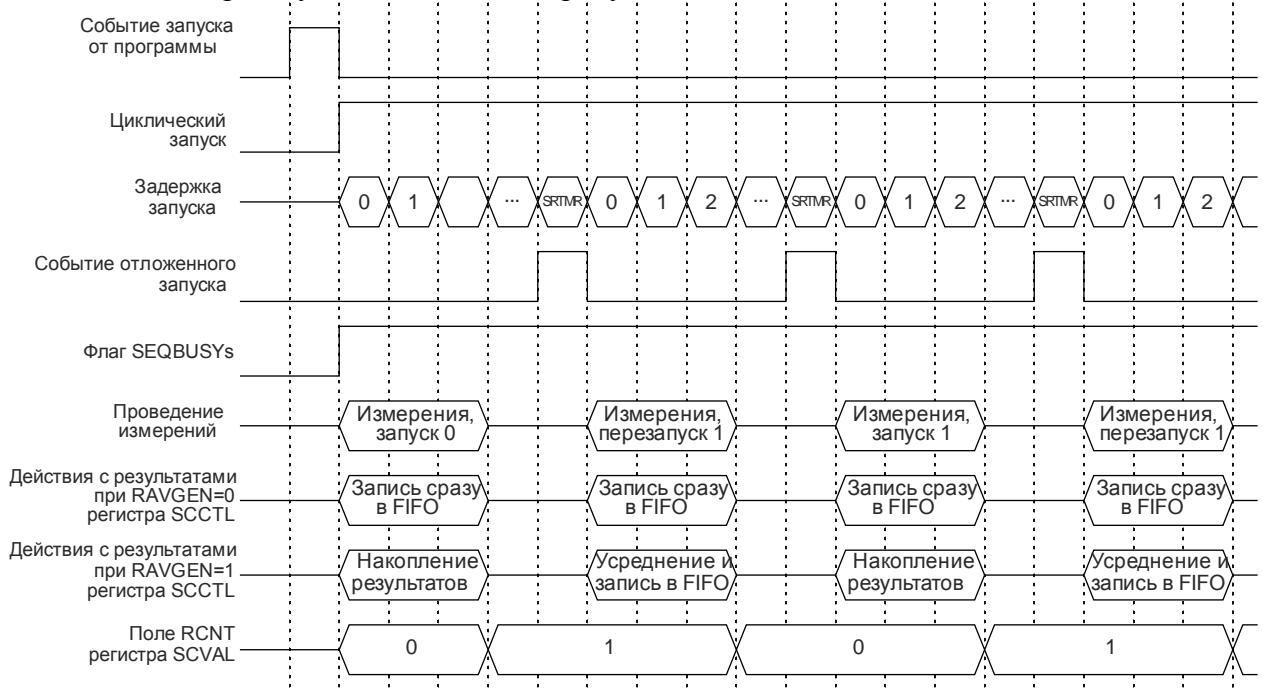

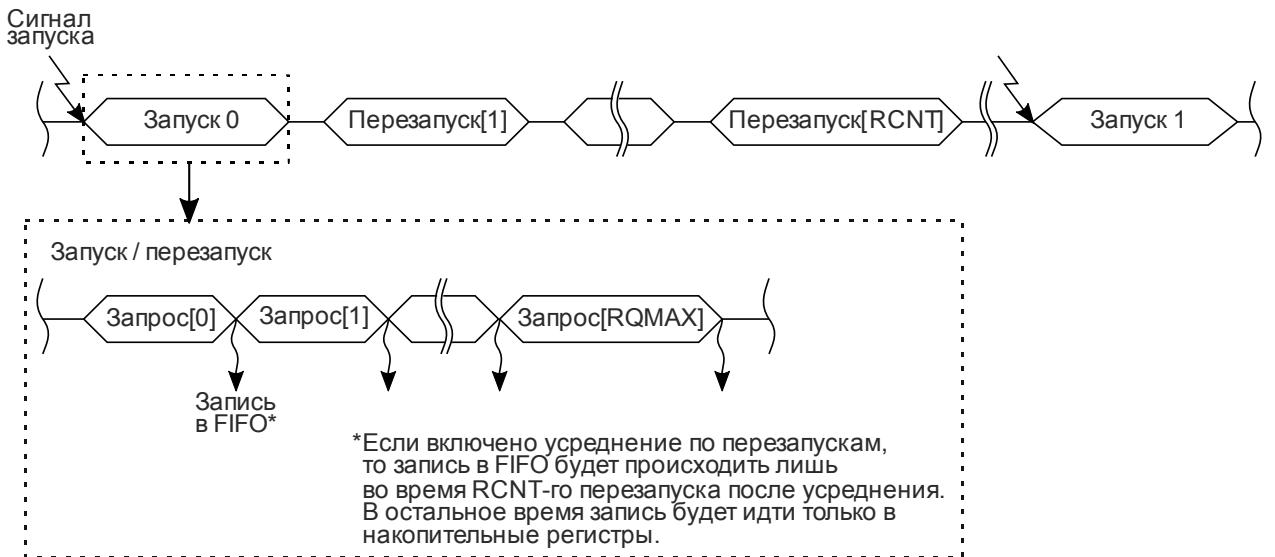

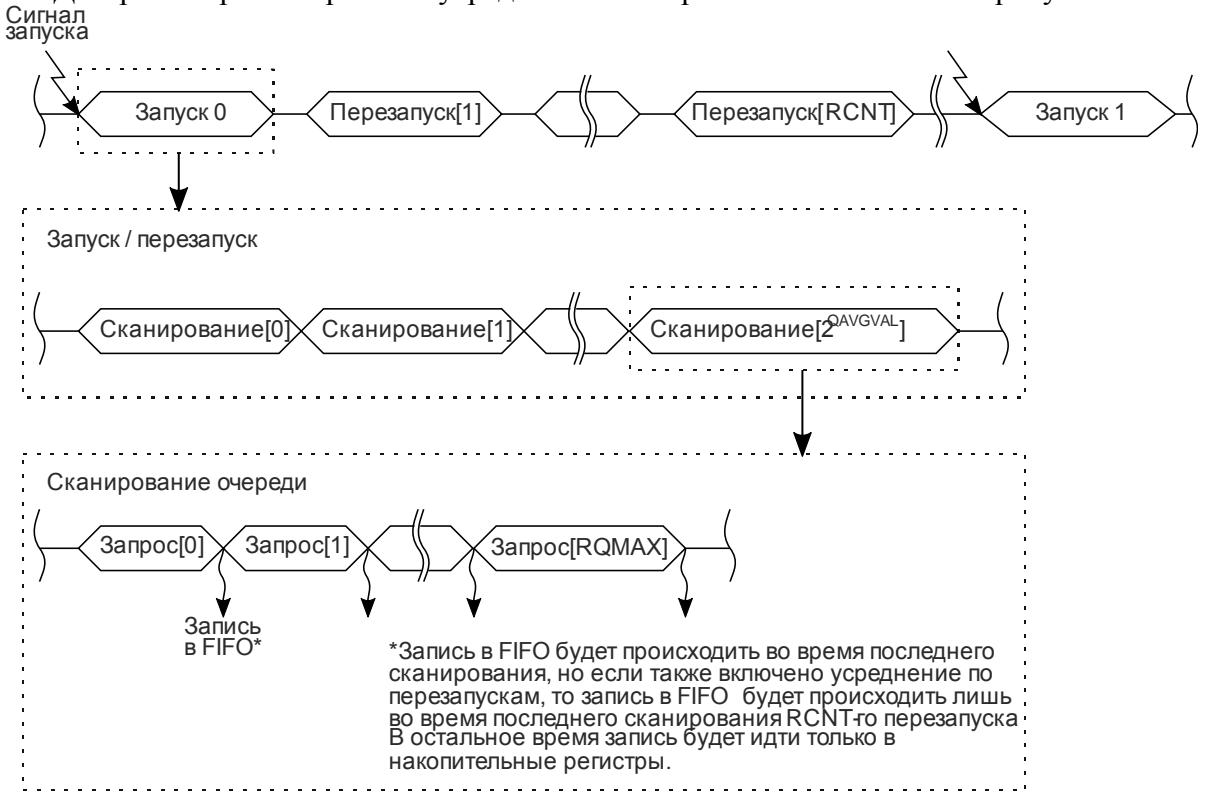

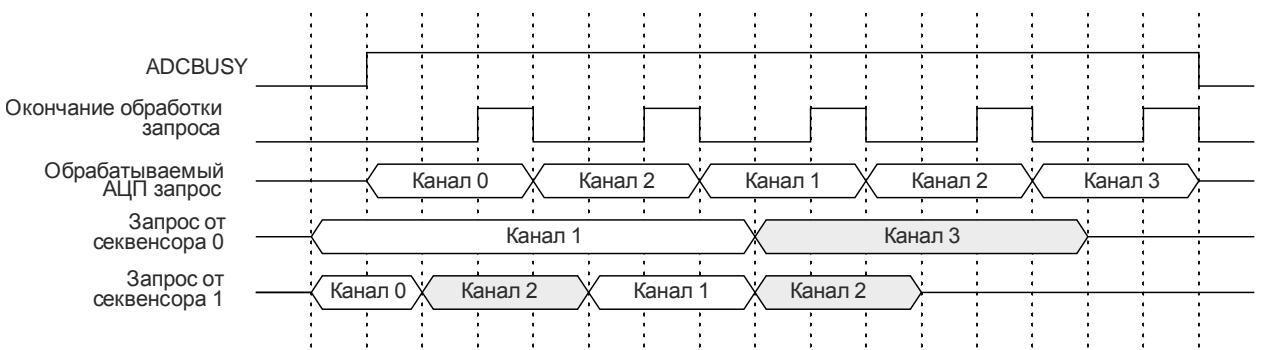

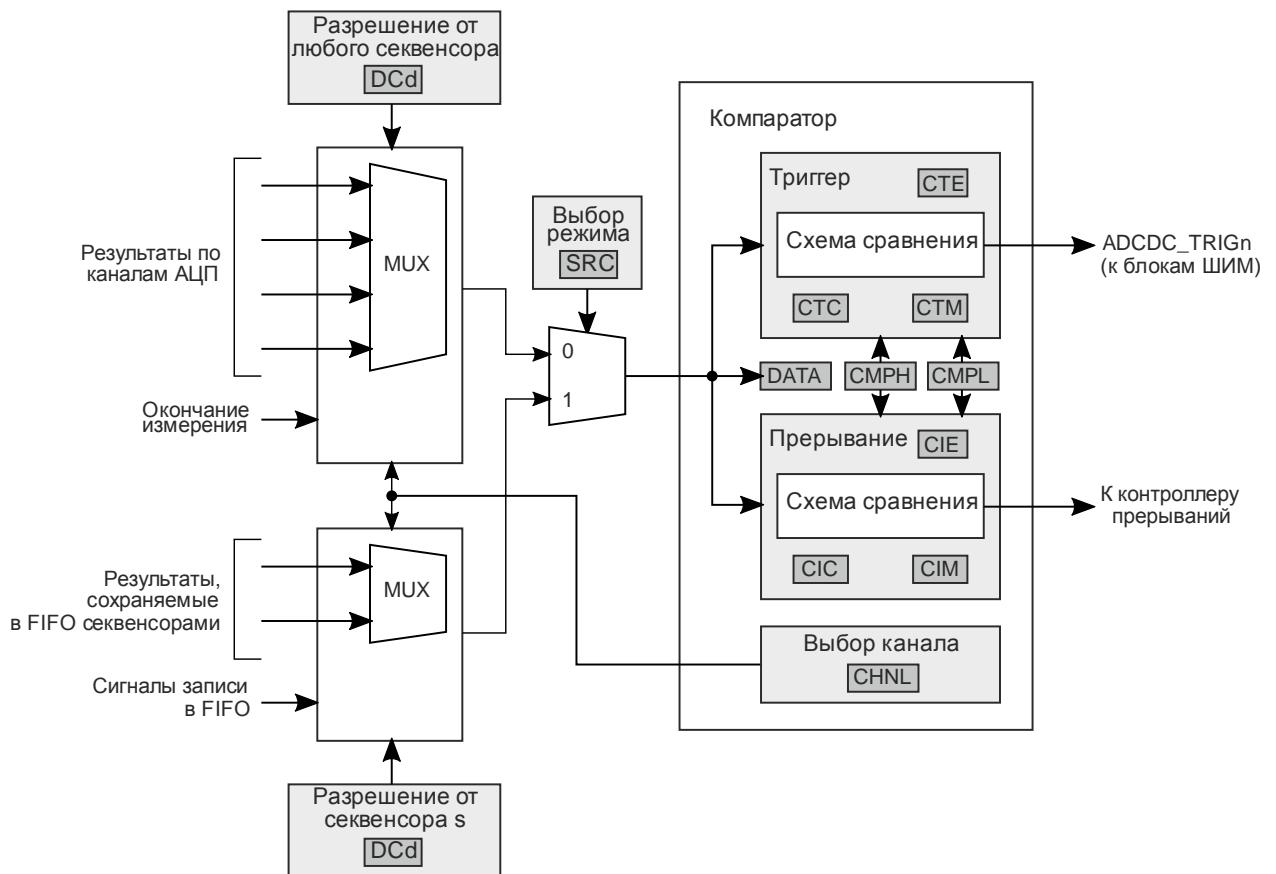

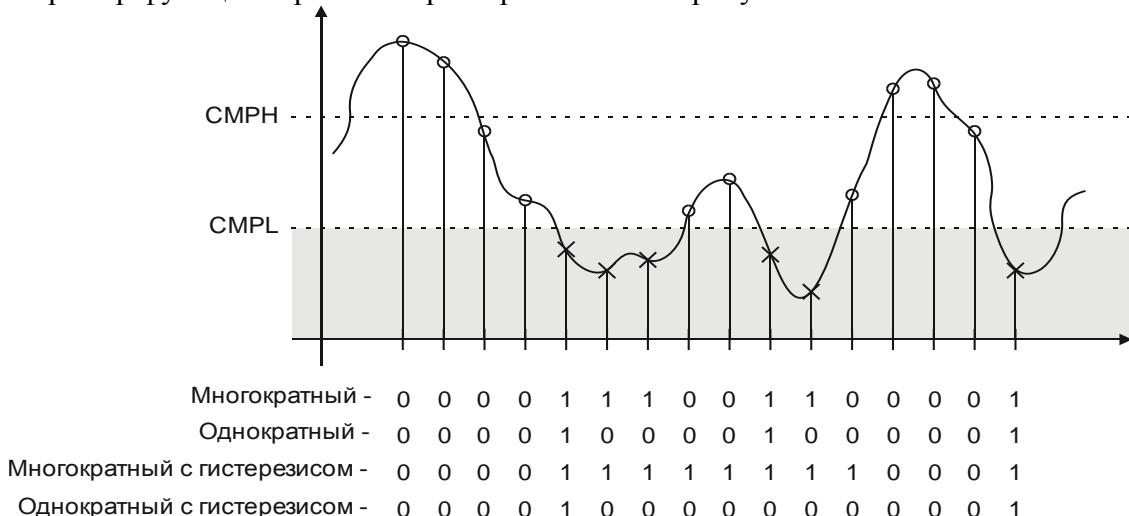

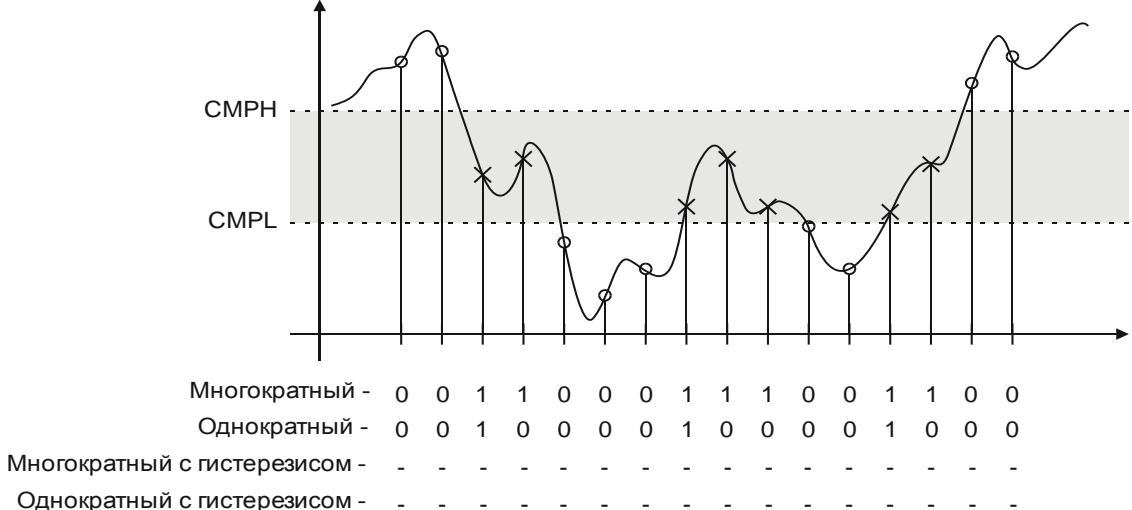

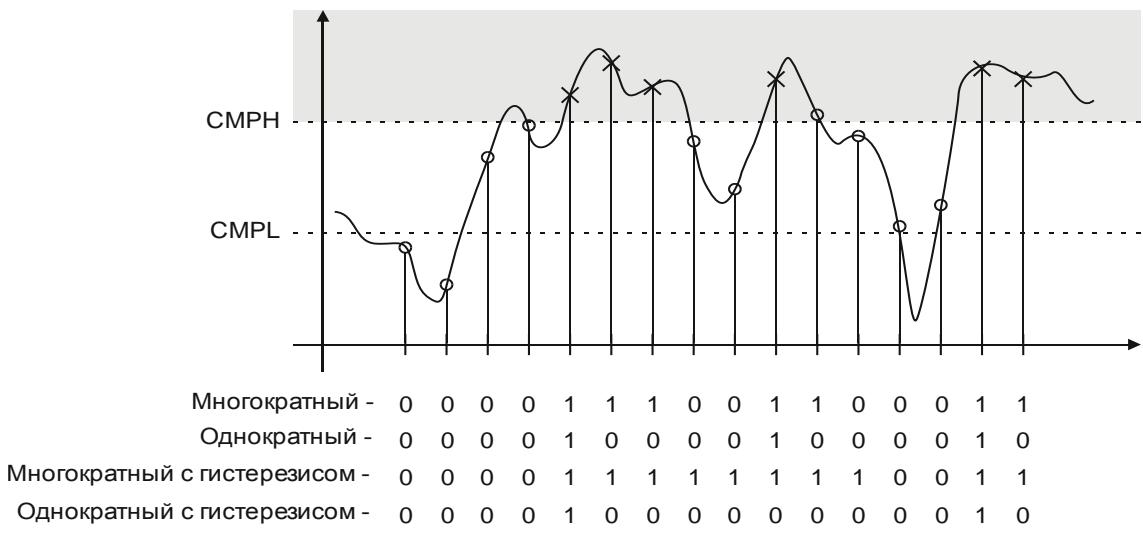

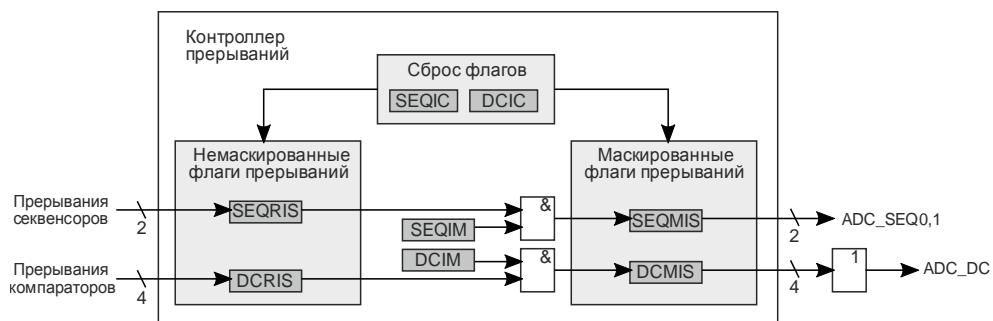

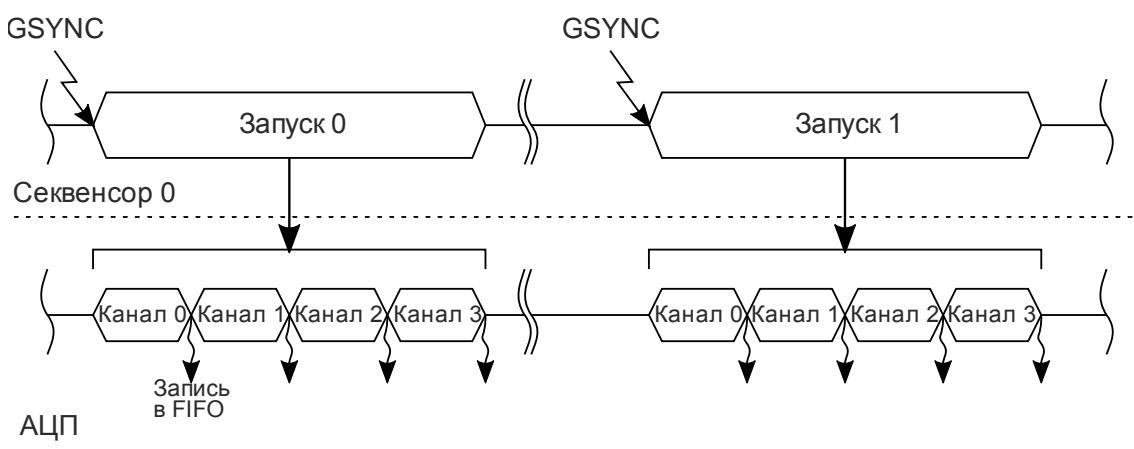

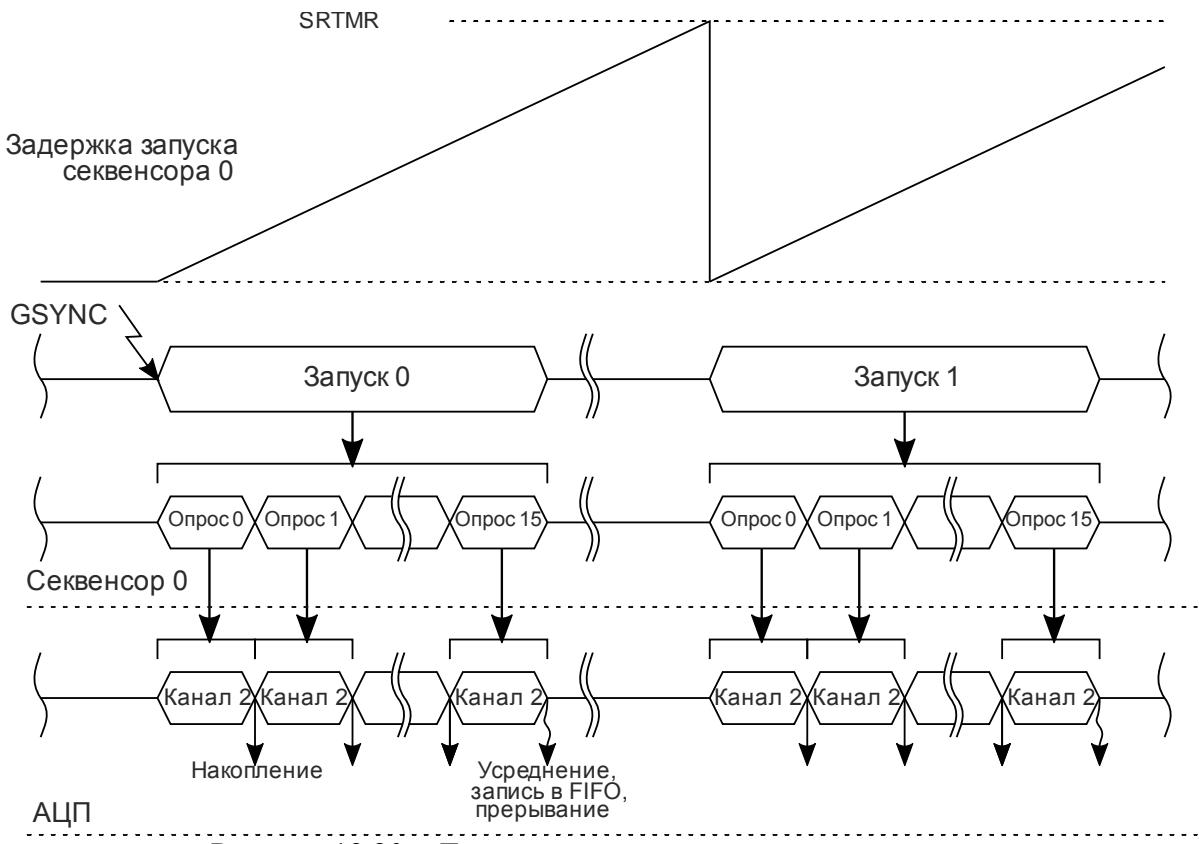

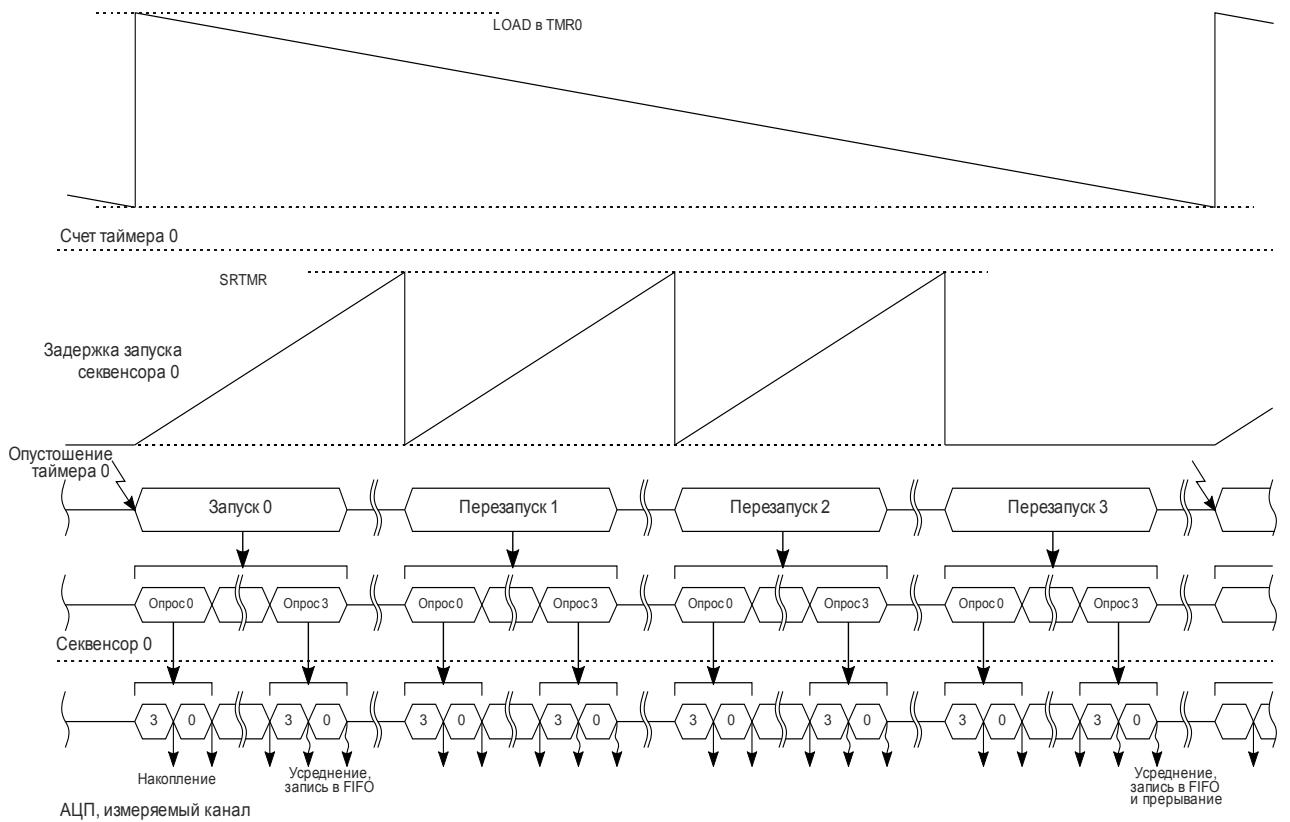

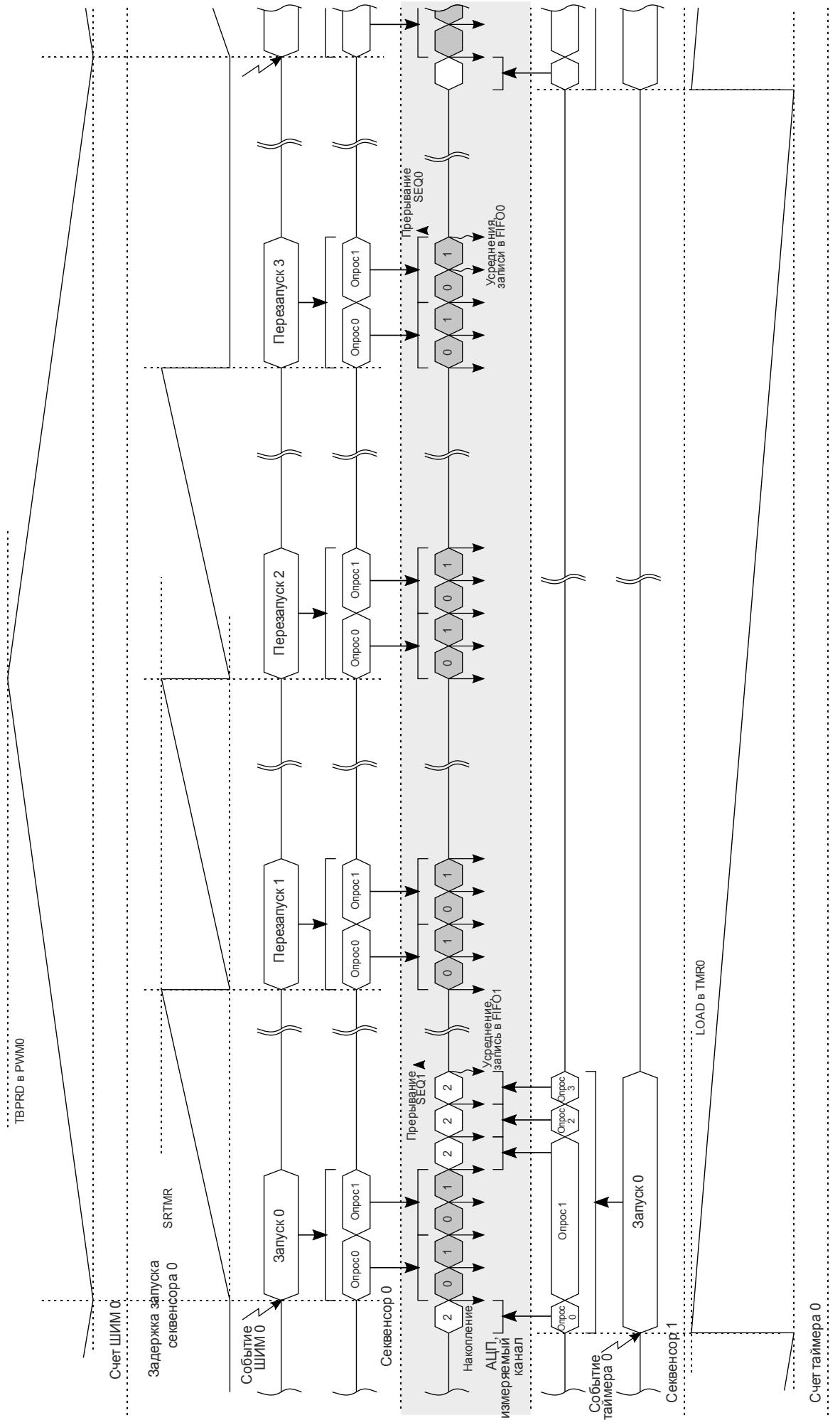

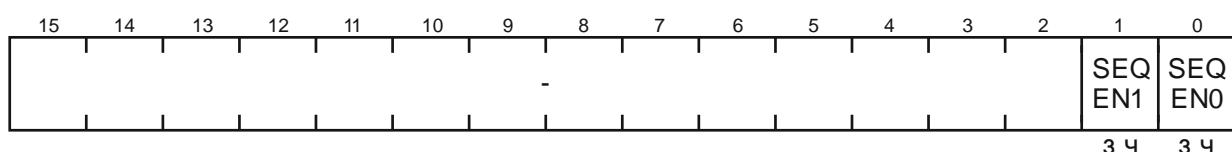

Рисунок 8.1 – Карта памяти для 16 каналов контроллера DMA, включая альтернативную структуру