## Отладочная плата *LDM-EP1C3-T100*

LDM SYSTEMS

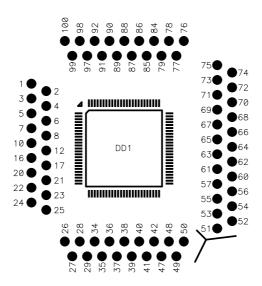

LDM-EP1C3-T100 Отладочная плата представляет собой печатную плату размером 97х71х12 мм и макетным полем 71х45 мм (шаг отверстий 2.54 мм) с установленной на ней микросхемой ПЛИС DD1 фирмы Altera Cyclone FPGA корпусе TQFP-100. семейства В Для проектирования плата под микросхемой DD1 разведена так, чтобы было удобно производить пайку проводным монтажом (ножки ввода/вывода имеют соответствующие площадки, отведенные от корпуса DD1, обозначения номеров выводов указаны на рис. 4). Плата снабжена разъемом XS2 (IDC-10MS) для подключения загрузочных кабелей LDM-USB-Blaster, LDM-PB 2.01 ByteBlasterMV или их аналогов (в режиме JTAG). Питание платы осуществляется от внешнего стабилизированного источника с напряжением + 9...12 В, который подключается к разъему XS1. Светодиод VD2 является индикатором наличия питания.

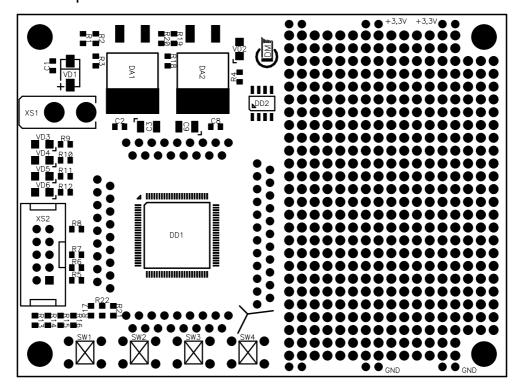

Рис. 1. Общий вид отладочной платы

Линейные преобразователи напряжения DA1 и DA2 (LM317D2P) в корпусе D2PAK преобразуют напряжение источника питания в напряжение VCCINT = 1.5 В и VCCIO = 3.3 В.

Таблица 1 Основные характеристики отладочной платы

| Версия платы   | Тип ПЛИС  | Напряжение<br>питания ПЛИС,<br>В | Кол-во ножек<br>ввода/вывода | Логическая<br>емкость,<br>элементов<br>LEs |

|----------------|-----------|----------------------------------|------------------------------|--------------------------------------------|

| LDM-EP1C3-T100 | EP1C3T100 | 1.5                              | 65                           | 2 910                                      |

На плате предусмотрена монтажная площадка под установку конфигурационной микросхемы DD2 (EPCS1SI8) в корпусе SOIC-8. Эта микросхема позволяет производить конфигурацию ПЛИС в режиме Active Serial. Для программирования конфигурационного ПЗУ в ПЛИС по JTAG-интерфейсу загружается специально подготовленный проект - Serial FlashLoader (SFL). SFL представляет собой мост между интерфейсами JTAG и Active Serial и преобразует поток данных, поступающих по JTAG-интерфейсу в формат, необходимый для программирования последовательного конфигурационного ПЗУ.

Отладочная плата предназначена для макетирования устройств, проектируемых на ПЛИС фирмы Altera семейства Cyclone, а также устройств сборки законченных путем монтажа необходимых компонентов на макетном поле платы. Использование LDM-EP1C3-T100 позволяет сократить время внедрения максимально продукта пользователя на рынок.

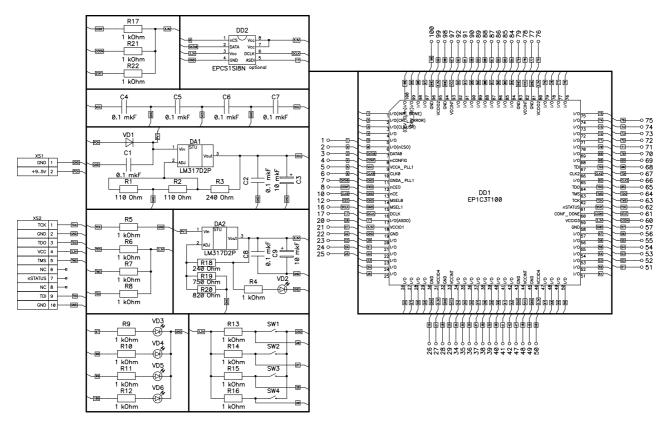

Рис. 2. Схема электрическая принципиальная

На плате расположены четыре светодиода VD3-VD6 и четыре кнопки SW1-SW4, которые подключены к выводам ПЛИС. Они предназначены для упрощения проектирования и могут пригодиться при тестировании проекта.

Рис. 3. Внешний вид печатной платы

Рис. 4. Обозначение монтажных площадок

## Комплектация:

- отладочная плата;

- описание к отладочной плате;

- примеры проектов для Quartus II Web Edition Software;

- описание к семейству ПЛИС Altera.