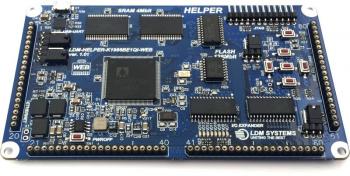

LDM-HELPER-K1986BE1QI-WEB

Отладочная плата LDM-HELPER-K1986BE1QI-WEB представляет собой master-модуль к мультиплатформенной системе проектирования семейства HELPER. Имеет габаритные размеры 130 х 74 х 8 мм.

LDM-HELPER-K1986BE1QI-WEB – создана на базе российского микроконтроллера фирмы ЗАО «ПКК Миландр» K1986BE1QI в пластиковом корпусе TQFP-144.

-

K1986BE1QI - Микроконтроллер для авиационного применения со встроенной Flash-памятью программ и построен на базе высокопроизводительного процессорного RISC ядра. Микроконтроллер работает на тактовой частоте до 140 МГц и содержит 128 Кбайт Flash-памяти программ и 48 Кбайт ОЗУ. Периферия включает в себя контроллер USB интерфейса со встроенным аналоговым приемопередатчиком и со скоростью передачи 12 Мбит/с (Full Speed) и 1.5 Мбит/с (Low Speed), стандартные интерфейсы UART и SPI, авиационные интерфейсы по ГОСТ 18977-79 и ГОСТ Р52070-2003, цифровой интерфейс Ethernet со скоростью передачи 10/100 Мбит, интерфейсом MII и со встроенным аналоговым приемопередатчиком, контроллер внешней системной шины, позволяющий работать с внешними микросхемами статического ОЗУ и ПЗУ, NAND Flash памятью и другими периферийными устройствами.

Микроконтроллер содержит четыре 32-х разрядных таймера с 4 каналами схем захвата и ШИМ с функциями формирования «мертвой зоны» и аппаратной блокировки. Также микроконтроллер содержит системный 24-х разрядный таймер и два сторожевых таймера. Микроконтроллер содержит 12-ти разрядный высокоскоростной (до 512 Квыб/с) АЦП с возможностью оцифровки информации с 8 каналов, встроенного датчика температуры и опорного напряжения. Два 12-ти разрядных ЦАП.

Встроенные RC генераторы HSI (8 МГц) и LSI (40 кГц) и внешние генераторы HSE (2…16 МГц) и LSE (32 кГц) и две схемы умножения тактовой частоты PLL для ядра и USB интерфейса позволяют гибко настраивать скорость работы микроконтроллеров.

Архитектура системы памяти за счет матрицы системных шин позволяет минимизировать возможные конфликты при работе системы и повысить общую производительность. Контроллер DMA позволяет ускорить обмен информацией между ОЗУ и периферией без участия процессорного ядра.

Кроме этого, имеет следующие блоки:

-

MCP23S18 - Общего назначения 16-битный расширитель портов ввода/вывода с интерфейсом SPI. Максимальная тактовая частота - 10 МГц.

-

M25P128-VMF6TP - 128 Мб флэш-память, совместима с последовательным интерфейсом SPI на тактовой частоте 54 МГц. Более 10000 циклов стирания /записи, хранения данных более 20 лет.

-

CY7C1041DV33-10ZSXI - 4 Мбит (256 × 16) StaticRAM. ОЗУ с организацией 256К х 16 бит.